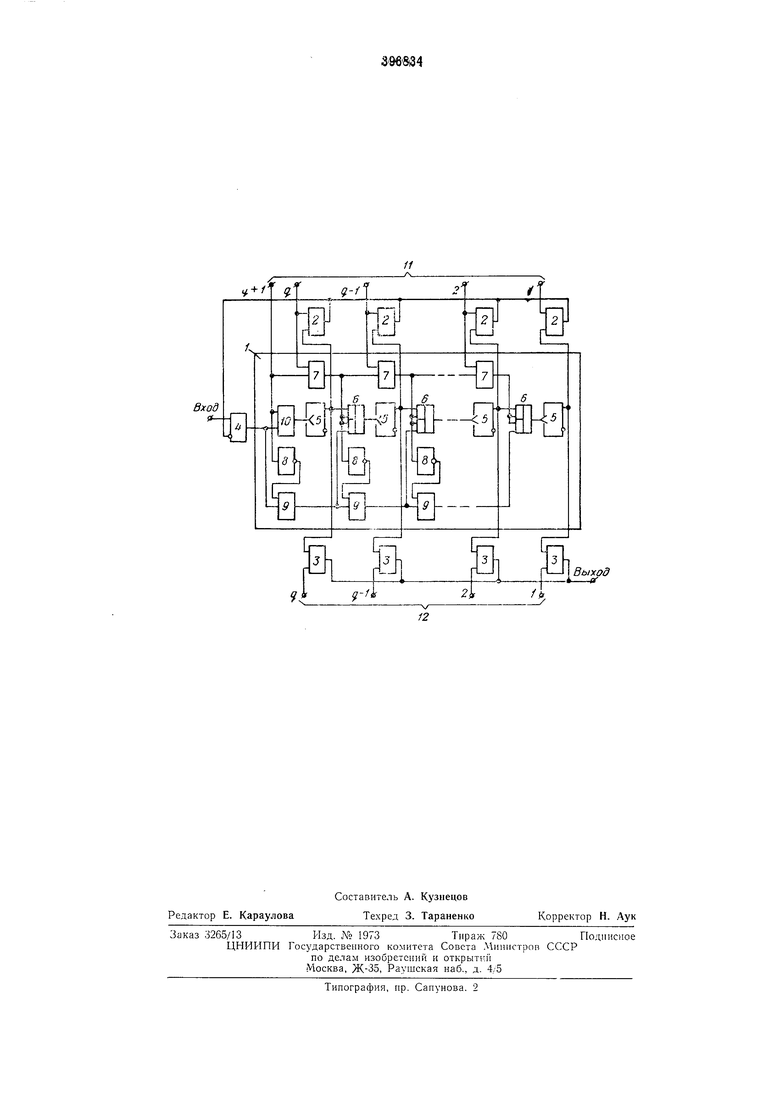

Изобретение относится к области кодирования и преобразования информации. Известно устройство, содержащее двоичные умножители частоты, входы которых соединены со схемой занрета, а вход занрещения схемы занрета соединен с выходом одного из двоичных умножителей частоты. Однако в таких устройствах пределы изменения коэффициентов деления делителей ограничены фиксированным числом разрядов двоичных умножителей, входящих в состав делителей, в частности числом разрядов двоичного умножителя, связанного с входом запрещения схемы запрета. Числе разрядов этого умножителя определяет пределы изменения числителя коэффициентов деления. С целью расширения пределов изменения коэффициента деления в предлагаемом устройстве двоичные умножители частоты выполнены в виде двух групп вентилей н двоичного счетчика, состоящего из триггеров, схем «ИЛИ, инверторов, внтилей и четырехБходовых схем «2И-ИЛИ, причем управляемые входы вентилей каждой группы подключены к параллельным выходам двоичного счетчика, а выходы этих вентилей объедине;;ы и подсоединены к выходам умножителей частоты, выход триггера каждого разряда двоичного счетчика соединен с первым входом схемы «2И-ИЛИ, выход которой соединен с входом триггера последующего разряда, второй и третий входы каждой схемы «2И-ИЛИ объединены н соединены с входом инвертора и с выходом схемы «ИЛИ, один из входов которой соединен с управляющим входом вентиля одного из умножителей частоты и с входными клеммами ввода двоичных кодов числителя, четвертый вход каждой схемы «2И-ИЛИ соединен с управляемым входом вентиля двоичного счетчика, управляющий вход этого вентиля соединен с выходом инвертора, выход каждого предыдущего вентиля соединен с управляемым входом каждого последующего вентиля, выход каждой предыдущей схемы «ИЛИ соединен с Еходом каждой последующей, а управляющие входы вентилей другого умножителя частоты соединены с входными клеммами ввода дсоичных кодов знаменателя. На чертеже прнведена функцнональнзя предлагаемого устройства. счетчик /, пфоиство содержит двоичный 2 л 3 ..,... .. .. . . две групгы 11 i пе Пилей и схему 4 запрета. С.:четчик / содержит триггеры 5, схемы 6 «2И-ИЛИ, схемы 7 «ИЛИ, инверторы 8, вентили 9 и 10 «И. Устройетво имеет входы /. Bi::7,a дг1оичных котов числителя и / диоичных кодов знаменателя. Число разрядов -разрядного счетчика /, /4acTB iOL,nx г; процессе деления частоты, зависит от числа разрядов двоичного кода, установленного на входах // ввода двоичных кодов числителя. Для г-разрядного числа Р в нроцессе деления частоты участвует f-1 старших разрядов счетчика. Это следует из того, что схемы 6 «2И-ИЛИ, включенные на счетных входах триггеров, находящихся в I-1 старших разрядов счетчика, открыты единичными потенциалами, поступаюш,ими с выходов схемы 7 «ИЛИ, связанных со схемой «ИЛИ, нодключенной к t-й кодовой шине П ввода двоичных кодов числителя. В то же время схемы 10 «И, схемы 6 «2И--ИЛИ, включенные на входах триггеров, находяш,ихся в q-(i-1) младших разрядах счетчика, закрыты нулевыми потенциалами, поступающими с выходов схем «ИЛИ, связанных кодовыми шинами И ввода двоичных кодов числителя. Так как управляющие входы вентилей 9 связаны через инверторы 8 с выходами схем «ИЛИ, то вентили, выходы которых подключены через схемы «2Р1-ИЛИ к счетным входам триггеров 5, находящихся в i-1 старших разрядах счетчика, закрыты, а остальные вентили открыты; следовательно, частота с выхода схемы 4 запрета поступает через открытые вентили 9 на счетный вход триггера, находящегося в разряде счетчика. Счетчик / совместно с группой 2 вентилей образует первый двоичный умножитель, который совместно со схемой 4 запрета образует делитель частоты с коэффициентом деления, заданным неправильной двоичной дробьюь - 2 йд 1 4- ггг где йд - коэффициент деления; / - число, находящееся после запятой. Частота на входе счетчика / равна где - частота на входе устройства. Счетчик / совместно с группой 3 вентилей образует второй двоичный умножитель с козффициентом умножения 2-(-1) yfey 1 - 2-(-1). Следовательно, при подаче на входы 12 ввода двоичных кодов знаменателя числа К Q - 1 с объединенных выходов группы 3 вентилей на выход устройства поступают импульсы со средней частотой повторения Р - b Р - F вых - «у J - вхВ целом устройство реализует дробный корэффициент деления - 1, пределы изменеПИЯ числителя которого ограничены значениями. В случае, когда коэффициенты деления имеют числитель, равный 1 или О, все схемы совпадения, включенные на входах триггеров счетчика, закрыты нулевыми сигналами, поступающими с кодовых щин // ввода двоичных кодов числителя, вследствие чего деление частоты не происходит. Это исключает ненравильную работу устройства. Предмет изобретения Делитель частоты, содержащий двоичные умножители частоты, входы которых соединены со схемой запрета, а вход запрещения схемы запрета соединен с выходом одного из двоичных умножителей частоты, отличающийся тем, что, с целью расширения пределов изменения коэффициента деления, двоичные умножители частоты выполнены в виде двух групп вентилей и двоичного счетчика, состоящего из триггеров, схем «ИЛИ, инверторов, вентилей и четырехвходовых схем «2И- ИЛР1, причем управляемые входы вентилей каждой группы подключены к параллельным выходам двоичного счетчика, а выходы этих вентилей объединены и подсоединены к выходам умножителей частоты, выход триггера каждого разряда двоичного счетчика соединен с первым входом схемы «2И-ИЛИ, выход которой соединен с входом триггера последующего разряда, второй и третий входы каждой схемы «2И-ИЛИ объединены н соединены с входом инвертора и с выходом схемы «ИЛИ, один из входов которой соединен с управляющим входом вентиля одного из умножителей частоты и с входными клеммами ввода двоичных кодов числителя, четвертый вход каждой схемы «2И-ИЛИ соединен с управляющим входом вентиля двоичного счетчика, управляющий вход этого вентиля соединен с выходом инвертора, выход каждого предыдущего вентиля соединен с управляемым входом каждого последующего вентиля, выход каждой предыдущей схемы «ИЛИ соединен с входом каждой последующей, а управляющие входы вентилей другого умножителя частоты соединены с входными клеммаЛИ ввода двоичных кодов знаменателя.

Вход

| название | год | авторы | номер документа |

|---|---|---|---|

| ОЮЗНАЯ | 1973 |

|

SU375796A1 |

| Цифровой частотомер | 1973 |

|

SU447637A1 |

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Делитель частоты импульсов с управляемым коэффициентом деления | 1976 |

|

SU738174A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| Преобразователь частота-код | 1983 |

|

SU1129543A1 |

| ДВОИЧНЫЙ УМНОЖИТЕЛЬ | 1992 |

|

RU2006918C1 |

| Делитель частоты импульсов с регулируемым коэффициентом деления | 1976 |

|

SU571915A1 |

| Импульсно-дискретное устройство для изменения частоты следования импульсов | 1977 |

|

SU621100A1 |

| Дробный делитель частоты следования импульсов | 1981 |

|

SU993480A1 |

Авторы

Даты

1973-01-01—Публикация