Изобретение относится к импульсной технике и может использоваться в частотнопреобразующих узлах аппаратуры времени и образцовых частотf измерительных приборов, средств связи и передачи данных, устройств автоматики, в составе которых имеются вычислительные устройства, например микропроцессоры.

Известен дробный делитель частоты, содержащий делитель частоты с переменным целочисленным коэффициентом деления, сумматоры, элемент сравнения и блок задержки tl 3Недостатки известного устройства ограниченные функциональные возможности и низкая надежность.

Наиболее близким по технической сущности к предлагаемому является делитель частоты следования импульсов с дробньм коэффициентом деления, содержащий делитель частоты с переменным коэффициентом деления, один вход которого соединен с входной шиной, второй вход - с первой шиной управления, третий вход - с первым выходом блока сравнения, входаг Которого соединены с выходами двух сумматоров, первые входы которых подключены к второй и третьей шине

управления, второй вход одного сумматора соединен с выходом второго . сумматора, а выход делителя частоты с переменным коэффициентом деления через элемент задержки соединен с выходной шиной, блок памяти, первыйи второй входы которого соединены с выходами сумматоров, два вентиля умножитель и делитель чисел, входы

10 которого соединены с третьей и четвертой шинами управляющих сигналов, а выход соединен с первым входом умножителя чисел, второй вход которого соединен с выходом элемента за15держки и первыми входами вентилей, вторые входы которых соединеныс выходами блока сравнения, а выходы вентилей подключены к третьему и четвертому входам блока памяти, вы20ход которого соединен с третьим входом умножителя чисел, с выходом которого соединен вход управления управляемого элемента задержки Недостатком делителя является

25 ограниченные функциональные возможности, так как он не рассчитан на работу в составе средств, имеющих собственное вычислительное устройство. Например, при применении в

30 составе цифровой системы фазовой

автоподстройки с цифровым импульсным фазовым дете1{тором код фазовой погрешности дробного делителя мо- . жет быть учтен .при формировании выходного кода цифрового импульснофазового детектора. Для этого и подобных применений в дробном делителе важно не скомпенсировать фазовую погрешность, а получить точное значение кода этой погрешности дри каждом очередном выходном импульсе. Кроме того делитель имеет низкую надежность ,

Цель изобретения - расширение функциональных возможностей при одновременном повышении надежности.

Для достижения цели в дробный делитель частоты следования импульсов, содержащий сумматор, разрядные выходы которого соединены с соответствующими входами запоминающего блока, выходы которого соединены с первой группой входов сумматора, делитель частоты с переменным коэффициентом деления, первый вход которого соединен с входной шиной, разрядные входы - с первой группой шин управления, а выход через элемент задержки - с первым входом вентиля, введены элемент ИЛИ, триггер и мультиплексор, первый и второй управляющие входы которого соединены соот ветственно с единичным и нулевым выходами триггера, первая и вторая информационные группы входов - соответственно с второй и третьей группами шин управления, а выходы - с второй группой входов сумматора, выходы всех разрядов которого, кроме знакового и старшего, подквпочены к шинам кода коррекций, а выход старшего разряда - к второму входу вентиля, выход которого соединен с первым единичным входом триггера и первым входом элемента ИЛИ, второй вход которого соединен с выходом делителя частоты с переменным коэффициентом деления и нулевым входом триггера, а выход - с входом разрешения записи запоминающего блока, выход старшего разряда которого подключен к третьему входу делителя частоты с переменным коэффициентом деления.

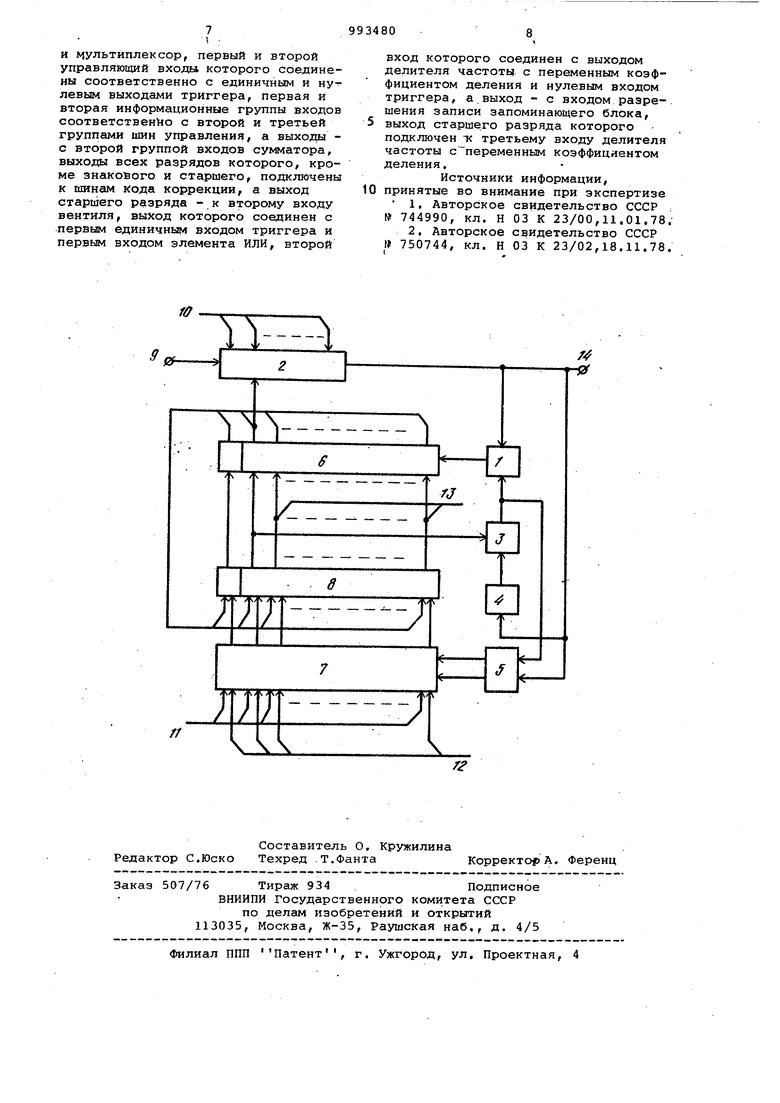

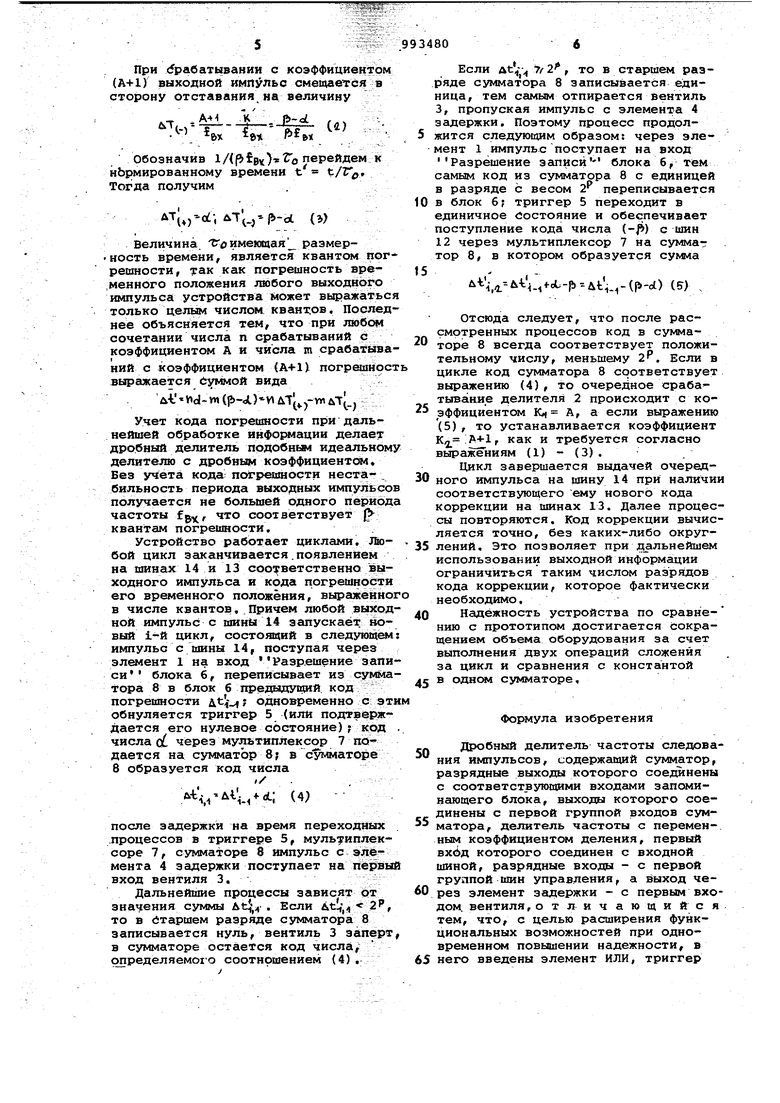

На чертеже представлена структурная схема делителя.

Делитель содержит элемент ИЛИ 1, делитель 2 частоты с переменным коэффициентом деления, вентиль 3, элемент 4 задержки, триггер 5, запоминающий блок б, мультиплексор 7, сумматор 8, входную шину 9, первую группу шин 10 управления кода целой части.коэффициента деления, вторую группу шин 11 управления кода числителя дробной части коэффициента деления, третью группу 12 управления кода знаменателя дробной части

фициента деления, шину 13 кода коррекции, выходную шину 14, .

Коэффициент деления делителя 2 может иметь одно из двух значений К А или К2 А+1, где А - целая

часть дробного коэффициента деления устройства. Значение .К устанавливается при логическом нуле, значение К - при логической единице на третьем входе делителя 2, Код числа А

подается на ши«ы 10, На шины 11 подается прямой, а на шины 12 - обратный код соответственно числителя и знаменателя дробного коэффициента К, Поэтому сумматор в рассчитан на

работу с обратными кодами чисел

(цепь переноса из знакового разряда в младший на чертеже не показана), Элемент 4 задержки служит для задержки сигнала на время переходных

процессов в мультиплексоре 7 .и сумматоре 8, Триггер 5 управляет мультиплексором If который передаёт на сумматор 8 код с шин 11 при нулевом и с шин 12 при единичном состоянии

триггера 5, Если сумматор 8 двоичный, то коды на шинах 11 - 13 тоже двоич ные. На шинах 10 код соответствует типу делителя 2, Необходимая, разрядность блоков 6-8 устройства устанавливается исходя из

того, что вес старшего разряда сумматора 8 должен удовлетворять неравенству

Ртак- Ьуу,ах, .- наибольшее возможное

где fwrtKC

значение знаменателя дробной части К.

Дробный делитель частоты следоан.ия импульсов работает следующим образо.

Пусть X - логическая переменная на третьем входе делителя 2, Если О, то делитель 2 срабатывает с коэффициентом К А, а если X 1, то с коэффициентом К А-И, Соответственно очередной выходной импульс устройства сдвигается в сторону опережения или отставания, так как

(AH)/fg,

-)

где aL - дробный коэффициент де ления; о/ ft - числитель и знаменатель

его дробной части; f - частота импульсов на входе устройства. При срабатывании делителя 2 с коэффициентом деления А выходной импульс смещается в сторону опережения на величину

«4 A -oL. 01

Wi. При Срабатывании с коэффициентом (А+1} выходной импульс смещается в сторону отставання на величину -vr-T V 2 11 I I.II . I.. I ..а tft 6Х Обозначив l/()o перейдем к нЬрмированному времени t . Тогда получим . ) (ЪУ Величина. ТГоимеющая раэмерность времени, является квантом пог решности, так как погрешность вре,менного положения /иобого выходного импульса устройства может выражатьс только цельпи числом квантов. Послед нее объясняется тем, что при любом сочетании числа п срабатываний с коэффициентом А и числа m срабатыва ний с коэффициентом (А+1): погрешнос выражается (:;уммой вида Л-tWcJ-W () ЛТ|.., Учет кода погрешности при дальнейшей обработке информации делает дробный делитель прдобннм идеальном делителю с дробным коэффициентам Без учёта кода пот-ретдности неста- бильность периода выходных импульсо получается не большей Одного период частоты что соответствует квантам погрешности. Устройство работает циклами, Jboбой цикл заканчивается.появлением на шинах 14 и 13 соог ветственно выходного импульса и кода погрешности его временного положения, выраженно в числе квантов, Причем любой выход ной импульс с шинЫ 14 запускает вовый 1-й цикл, состоящий в следующем импульс с шины 14, поступая через элет«ент 1 на вход Разрешение запи си блока 6, переписывает из сумма тора 8 в блок 6 предьвДУЩий код погрешности itif,;,; одновременно с эт обнуляется триггер 5 (или подтверждается его нулевое состояние); код числа 0 через мультиплексор 7 подается на сумматор 8 в сумматоре 8 образуется код числа i, после задержки на время переходных .процессов в триггере 5, мультиплексоре 7, сумматоре 8 импульс с элемента 4 задержки поступает на вход вентиля 3. Дальнейшие процессы зависят от значения суммы лЦн- Если Atl/j,, 2, то в атаршем разряде сумматора 8 записывается нуль, вентиль 3 заперт в сумматоре остается код числа, определяемохО соотношением 4) , Если At,-- 7/-2 , то в старшем разряде сумматора 8 записывается единица, тем самым отпирается вентиль 3, пропуская импульс с элемента 4 задержки. Поэтому процесс продолжится следующим образом: через элемент 1 импульс поступает на вход Разрешение записи блока б, тем самым код из сумматора 8 с единицей в разряде с весом 2 переписывается в блок 6; триггер 5 переходит в единичное состояние и обеспечивает поступление кода числа (-/) с шин 12 через мультиплексор 7 на сумматор 8, в котором образуется сумма X2.- -i -ib--&t4.-(p-ot) (в) . Отсюда следует, что после рассмотренных процессов код в сумматоре 8 всегда соответствует положительному числу, меньшему 2, Если в цикле код сумматора 8 соответствует вырсокению (4) , то очередное срабатывани е делителя 2 происходит с коэффициентом К|( А, а если выражению (5), то устанавливается коэффициент Ky. как и требуется согласно выражениям (1) - (3). Цикл завершается выдачей очередного импульса на шину 14 при: наличии соответствующего ему нового кода коррекции на шинах 13. Далее процессы повторяются. Код коррекции вычисляется точно, без каких-либо округлений. Это позволяет при цальнейшем использовании выходной информации ограничиться таким числом разрядов кода коррекции, которое фактически необходимо, Надёжность устройства по сравнению с прототипом достигается сокращением объема оборудования за счет выполнения двух операций сложения за цикл и сравнения с константой в однсах сумматоре. Формула изобретения Дробный делитель частоты следования импульсов, содержащий сумматор, разрядные выходы которого соединены с соответствующими входами запоминающего блока, выходы которого соединены с первой группой входов сумматора, делитель частоты с переменным коэффициентом деления, первый вхбд которого соединен с входной шиной, разрядные входы - с первой группой шин управления, а выход через элемент задержки - с первым входом, вентиля,отличающийся тем, что, с целью расширения функциональных возможностей при одновременном повышении надежности, в него введены элемент или, триггер

и мультиплексор, первый и второй управляющий входы которого соединены соответственно с единичным и нулевым выходами триггера, первая и вторая информационные группы входов соответствен 1о с второй и третьей группами шин управления, а выходы с второй группой входов сумматора, выходы всех разрядов которого, кроме знакойого и старшего, подключены К шинам кода коррекции, а выход старшего разряда - к второму входу вентиля, выход которого соединен с .первым единичным входом триггера и первым входом элемента ИЛИ, второй

вход которого соединен с выходом делителя частоты с переменным коэффициентом деления и нулевым входом триггера, а.выход - с входом разре-. шения записи запоминающего блока,

выход старшего разряда которого подключен К третьему входу делителя частоты с переменным коэффициентом деления,

Источники информации,

принятые во внимание при экспертизе 1, Авторское свидетельство СССР . № 744990, кл. Н 03 К 23/00,11.01.78.

2. Авторское свидетельство СССР № 750744, кл. Н 03 К 23/02,18.11.78.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с дробнымпЕРЕМЕННыМ КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU849493A1 |

| Делитель частоты с переменным коэффициентом деления | 1976 |

|

SU657619A1 |

| Устройство для контроля метрологических характеристик средств измерений | 1982 |

|

SU1117592A1 |

| Программируемый делитель частоты следования импульсов | 1981 |

|

SU993481A1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕРВАЛА ВРЕМЕНИ | 2014 |

|

RU2570116C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 2002 |

|

RU2222101C2 |

| Умножитель частоты | 1978 |

|

SU765818A1 |

fff

Jr 1ф

0

V---

N

1

в

i. Л V А

Л Л. t ЛЧ

//

Авторы

Даты

1983-01-30—Публикация

1981-06-01—Подача