1

Изобретение относится к области кодирования и преобразования информации.

Известны умножители частоты повторения импульсов, содержащие делитель опорной частоты, счетчик импульсов поделенной опорной частоты, счетчик импульсов опорной частоты, запоминающий регистр и схему сравнения кодов.

Однако в известных умножителях с увеличением коэффициента умножения увеличивается относительная погрещность преобразования частот и уменьшается диапазон умножаемых частот.

С целью увеличения точности умножения и расширения диапазона умножаемых частот в предлагаемом умножителе частоты повторения импульсов параллельные входы счетчика импульсов эталонной частоты подключены через первую группу вентилей переноса кодов ко входам первого запоминающего регистра, а через вторую группу вентилей переноса кодов и через первую схему «ИЛИ - ко входам второго запоминающего регистра, выходы которого соединены со входами второй схемы «ИЛИ и со входами ввода кодов числителя делителя частоты, подключенного входами ввода кодов знаменателя к шинам установки кодов коэффициентов умножения умножителя, счетным входом через один из сходов первой схемы «И - к источнику эталонной частоты, первым выходом - к выходу умножителя, а вторым выходом - ко входу приема команды «Гашение второго запоминающего регистра и через элементы задержки - к управляемым входам третьей группы вентилей переноса кодов и ко входу приема команды «Гашение первого запоминающего регистра, связанного параллельными выходами через третью группу вентилей

переноса кодов через первую схему «ИЛИ со входами приема кодов второго запоминающего регистра и через схему «ИЛИ - ИЕ с первыми входами второй и третьей схем «И, вторые входы которых подключены к выходу

схемы привязки импульсов эталонной частоты к асинхронному сигналу, при этом выход второй схемы «ИЛИ подключен к третьему входу второй схемы «И, ,ко второму входу первой схемы «И и через схемы «ИЕ - к

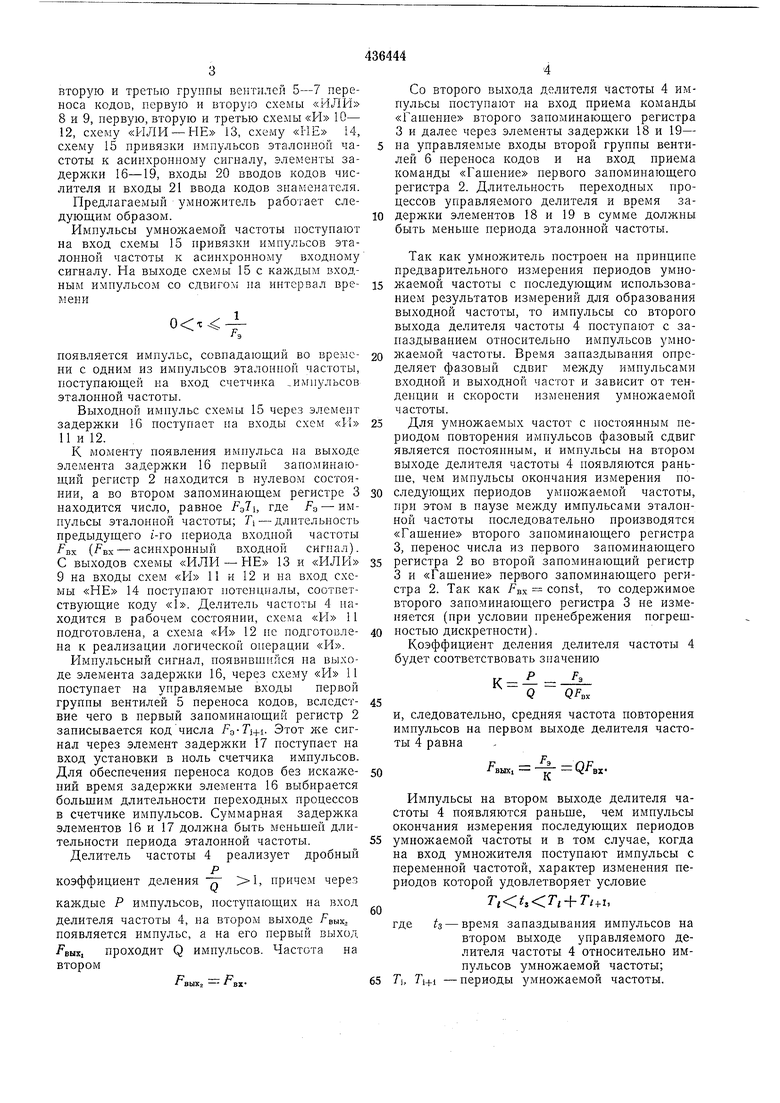

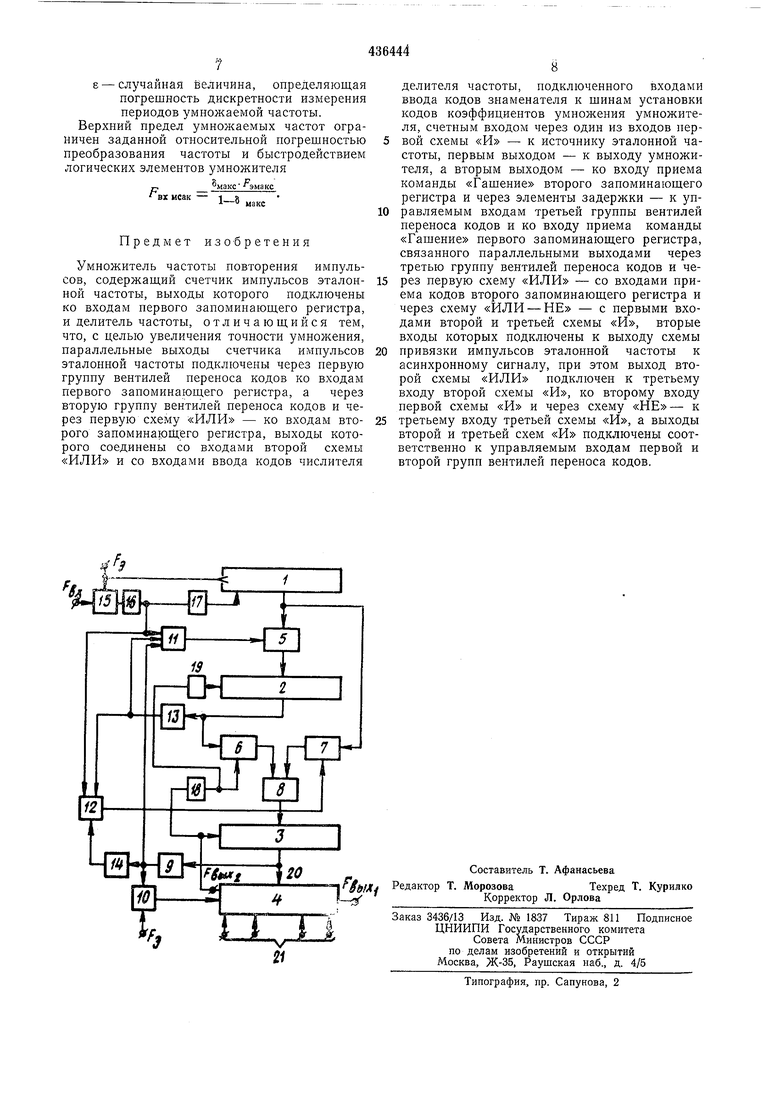

третьему входу третьей схемы «И, а выходы второй и третьей схем «И подключены соответственно к управляемым входам первой и второй групп вентилей переноса кодов. На чертеже приведена функциональная схема умножителя частоты повторения импульсов.

Умножитель частоты повторения импульсов содержит счетчик 1 импульсов эталонной частоты, первый и второй запоминающие регистры 2 и 3, делитель частоты 4, первую, вторую и третью группы вентилей 5-7 переноса кодов, первую и вторую схемы «ИЛИ 8 и 9, первую, вторую и третью схемы «РЬ 10- 12, схему «ИЛИ - НЕ 13, схему «ЫЕ i4, схему 15 привязки импульсов эталонной частоты к асинхронному сигналу, элементы задержки 16-19, входы 20 вводов кодов числителя и входы 21 ввода кодов знаменателя. Предлагаемый умножитель работает следующим образом. Импульсы умножаемой частоты поступают на вход схемы 15 привязки импульсов эталонной частоты к асинхронному входному сигналу. На выходе схемы 15 с каждым входным импульсом со сдвигом па интервал времени0 появляется импульс, совпадающий во врегисни с одним из импульсов эталонной частоты, поступающей на вход счетчика .импульсов эталонной частоты. Выходной имнульс схемы 15 через элемент задержки 16 поступает на входы схем «И 11 и 12. К моменту появления импульса на выходе элемента задержки 16 первый запоминающий регистр 2 находится в нулевом состоянии, а во втором запоминающем регистре 3 находится число, равное FsTi, где Рэ - импульсы эталонной частоты; jTi - длительность предыдущего i-ro периода входной частоты Рвх ( - асинхронный входной сигнал). С выходов схемы «ИЛИ - НЕ 13 и «ИЛИ 9 на входы схем «И 11 и 12 и на вход схемы «НЕ 14 поступают потенциалы, соответствующие коду «1. Делитель частоты 4 находится в рабочем состоянии, схема «И 11 подготовлена, а схема «И 12 не подготовлена к реализации логической операции «И. Импульсный сигнал, появившийся на выходе элемента задержки 16, через схему «И 11 ностунает на управляемые входы первой группы вентилей 5 переноса кодов, вследствие чего в первый запоминающий регистр 2 записывается код числа F -Ti+i. Этот же сигнал через элемент задержки 17 ноступает на вход установки в ноль счетчика импульсов. Для обеспечения нереноса кодов без искажений время задержки элемента 16 выбирается большим длительности переходных процессов в счетчике импульсов. Суммарная задержка элементов 16 и 17 должна быть меньшей длительности периода эталонной частоты. Делитель частоты 4 реализует дробный коэффициент деления - 1, причем через каждые Р импульсов, поступающих на вход делителя частоты 4, на второл выходе РВЫ,, появляется импульс, а на его первый выход , проходит Q имнульсов. Частота на втором Р - Р ВЫХо вх Со второго выхода делителя частоты 4 импульсы поступают на вход приема команды «Гашение второго запоминающего регистра 3 и далее через элементы задержки 18 и 19- на управляемые входы второй группы вентилей б переноса кодов и на вход приема команды «Гашение первого запоминающего регистра 2. Длительность переходных процессов управляемого делителя и время задержки элементов 18 и 19 в сумме должны быть меньше периода эталонной частоты. Так как умножитель построен на принципе предварительного измерения периодов умножаемой частоты с последующим использованием результатов измерений для образования выходной частоты, то импульсы со второго выхода делителя частоты 4 поступают с запаздыванием относительно импульсов умножаемой частоты. Время запаздывания определяет фазовый сдвиг между импульсами входной и выходной частот и зависит от тенденции и скорости изменения умножаемой частоты. Для умножаемых частот с постоянным периодом повторения импульсов фазовый сдвиг является постояиным, и импульсы на втором выходе делителя частоты 4 появляются раньше, чем импульсы окончания измерения последующих периодов умпожаемой частоты, при этом в паузе между импульсами эталонной частоты последовательно производятся «Гашение второго запоминающего регистра 3, перенос числа из первого запоминающего регистра 2 во второй запоминающий регистр 3 и «Гащение первого запоминающего регистра 2. Так как /вх const, то содержимое второго запоминающего регистра 3 не изменяется (при условии пренебрежения иогрещиостью дискретности). Коэффициент деления делителя частоты 4 будет соответствовать значению и, следовательно, средняя частота повторения импульсов на первом выходе делителя частоты 4 равна Гвых - 17 -- О.вхИмнульсы на втором выходе делителя частоты 4 появляются раньще, чем импульсы окончания измерения последующих периодов умножаемой частоты и в том случае, когда на вход умножителя поступают импульсы с переменной частотой, характер изменения периодов которой удовлетворяет условие ,Ti+Ti i, где ta - время запаздывания импульсов на втором выходе управляемого делителя частоты 4 относительно импульсов умножаемой частоты; Ti, TI+I - периоды умножаемой частоты. Средняя частота Повторения импульсов на первом выходе делителя частоты 4 равна FBIKI QFnt а на втором выходе fsbtX: - ВХВ случае проявления тенденции к понижению умножаемой частоты по мере уменьшения входной частоты фазовый сдвиг между импульсами умножаемой частоты и импульсами, поступающими со второго выхода делителя частоты 4, уменьшается; когда он становится меньше периода умножаемой частоты, импульсы на втором выходе делителя появляются раньше, чем в первый запоминающий регистр 2 записываются числа, соответ ствующие измеренным значениям последую щих периодов умножаемой частоты. В этом случае после «Гашения второго запоминающего регистра 3 и до прихода очередного импульса умножаемой частоты делитель частоты 4 находится в нерабочем состоянии, первая схема «И 11 неподготовлена, а вторая и третья схемы «И 10 и 12 подготовлены к выполнению логических операплй «И. Очередной импульс умножаемой частоты через третью схему «И 12 поступает на управляемые входы третьей группы вентилей 7 переноса кодов, вследствие чего во второй запоминающий регистр 3 записывается содержимое счетчика 1, а на выходе второй схемы «ИЛИ 9 появляется потенциал, соответствующий коду «Ь. Импульсы эталонной частоты начинают поступать через вторую схему «И 10 на вход делителя частоты 4. В момент, когда фазовый сдвиг становится меньше периода умножаемой частоты, частота повторения импульсов на втором выходе делителя частоты 4 равна Г где АГ /(0, а на первом выходе F - Q - TI + AT где АГ - нриращение периодов умножаемой частоты. При проявлении тенденции к повышению умножаемой частоты по мере уменьшения длительности периодов умножаемой частоты фазовый сдвиг между импульсами умножаемой частоты и импульсами, поступающими со второго выхода делителя частоты 4, увеличивается. В момент времени, когда фазовый сдвиг станет больше двух периодов умножаемой частоты, очередной импульс умножаемой частоты появится на входе умножителя раньше, чем произведется перезапись кода из первого запоминающего регистра 2 во второй запоминающий регистр 3. Во втором запоминаюш,ем регистре 3 содержится код числа FsTi, а в первом запоминающем регистре 2 - код числа FaTi+i, поэтому первая и третья схемы «И 11 и 12 неподготовлены к выполнению логической операции «И. Импульс, поступающий на вход умножителя, совпадает во времени с момента окончания отсчета i -Ь 2-го и началом отсчета (- -З-го периодов умножаемой частоты. Этот импульс поступает только на вход установки в О счетчика 1. В момент окончания процесса преобразования делителем частоты 4 i-ro периода умножаемой частоты на втором выходе делителя частоты 4 появляется импульс, вследствие чего последовательно производится «Гашение второго запомипающего регистра 6, перезапись кода числа /aTi+i из первого запоминающего регистра 2 во второй запоминающей регистр 3 и «Гашение первого запоминающего регистра 2. Потенциал, соответствующий коду «1 и поступающий с выхода схемы «ИЛИ - НЕ 13, подготавливает первую схему «И 11 к выполнению логической операции. Импульс окончапия г+З-го периода умножаемой частоты через первую схему «И 11 поступает на управляемые входы первой группы вентилей 5 переноса кодов, вследствие чего в первый запоминающий регистр 2 записывается код числа FoTj+s. В момент окончания отработки делителем частоты 4 I + 1-го периода и начала отработки i + 3-го периода умножаемой частоты фазовый сдвиг между умножаемой частотой и частотой, поступающей со второго выхода делителя частоты 4, скачком уменьшается до значения меньн1его, чем два периода умножаемой частоты. В случае, когда после первого скачкообразного изменения фазового сдвига, изменение умножаемой частоты сохраняется прежней, скачкообразные изменения фазового сдвига повторяются, причем частота повторения скачков зависит от скорости изменения умножаемой частоты и увеличивается с увеличением последней. Скачкообразное изменение фазового сдвига на выходах делителя частоты 4 нроявляется в том, что один из периодов частоты, поступающей со второго выхода делителя частоты 4, скачкообразно уменьшается и соответственно в течение временного интервала, равного длительности этого периода, частота на первом выходе делителя частоты 4 увеличивается. Относительная ногрешность преобразования частоты и диапазон умнол аемых частот не зависит от коэффициентов умножения частоты-; е 0, +1, -1, Jia 2 Rгде 8 - относительная погрешность преобразования частоты:

8 - случайная величина, определяющая погрешность дискретности измерения периодов умножаемой частоты. Верхний предел умножаемых частот ограничен заданной относительной погрешностью преобразования частоты и быстродействием логических элементов умножителя

вх Исак -

макс

Предмет изобретения

Умножитель частоты повторения импульсов, содержащий счетчик импульсов эталонной частоты, выходы которого подключены ко входам первого запоминающего регистра, и делитель частоты, отличающийся тем, что, с целью увеличения точности умножения, параллельные выходы счетчика импульсов эталонной частоты подключены через первую группу вентилей переноса кодов ко входам первого запоминаюш,его регистра, а через вторую группу вентилей переноса кодов и через первую схему «ИЛИ - ко входам второго запоминающего регистра, выходы которого соединены со входами второй схемы «ИЛИ и со входами ввода кодов числителя

делителя частоты, подключенного входами ввода кодов знаменателя к шинам установки кодов коэффициентов умножения умножителя, счетным входом через один из входов первой схемы «И - к источнику эталонной частоты, первым выходом - к выходу умножителя, а вторым выходом - ко входу приема команды «Гашение второго запоминающего регистра и через элементы задержки - к управляемым входам третьей группы вентилей переноса кодов и ко входу приема команды «Гашение первого запоминающего регистра, связанного параллельными выходами через третью группу вентилей переноса кодов и через первую схему «ИЛИ - со входами приема кодов второго запоминающего регистра и через схему «ИЛИ - НЕ - с первыми входами второй и третьей схемы «И, вторые входы которых подключены к выходу схемы

привязки импульсов эталонной частоты к асинхронному сигналу, при этом выход второй схемы «ИЛИ подключеп к третьему входу второй схемы «И, ко второму входу первой схемы «И и через схему к

третьему входу третьей схемы «И, а выходы второй и третьей схем «И подключены соответственно к управляемым входам первой и второй групп вентилей переноса кодов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой частотомер | 1973 |

|

SU481851A1 |

| Умножитель частоты следования импульсов | 1979 |

|

SU809526A1 |

| Устройство для умножения частоты следования периодических импульсов | 1975 |

|

SU544112A2 |

| Способ фазового управления асинхронным электродвигателем и устройство для его осуществления | 1978 |

|

SU928582A1 |

| Устройство для умножения частоты следования импульсов | 1980 |

|

SU884102A1 |

| Умножитель частоты следования импульсов | 1974 |

|

SU513510A1 |

| Цифровой умножитель частоты следования импульсов | 1982 |

|

SU1034146A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Фазометр | 1991 |

|

SU1817037A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU993451A1 |

Даты

1974-07-15—Публикация

1972-07-12—Подача