1

Устройство относится к вычислительной технике.

Для проверки передач информации между устройствами вычислительных машин широко используется способ контроля «четности кода. Признак четности или нечетности числа единиц в коде определяется с помош,ью специальных схем формИ|рования четности .кода.

Известные двоичны-е счетчики с контролем четности кода строятся по пиромидальному принципу из однотипных логических схем, определяющих значение четности, например, двухразрядного кода, либо определяют признак четности, последовательно учитывая все разряды числа.

В обоих случаях схемы счетчиков сложны .и требуют значительного оборудования.

Цель изобретения - упрощение схемы устройства.

Сущность изобретения состоит в следующем.

Если разбить весь счетчик на двухразрядные группы, начиная с младшего разряда, можно видеть, что признак четности в любой группе изменяется при изменении кода с 00 на 01 и € 10 на 11. В счетчике такие изменения происходят только в случае, когда код во всех группах справа от рассматриваемой изменяется с И на 00. При этом признак четности в разрядах справа от рассматриваемой

груггпы, как видно, не меняется. Таким образом, изменение значения младшего разряда группы с О на 1 означает изменение признака четности. Изменения состояния в младших с разрядах групп с О на 1 определяются с помощью дифференцирующих цепочек, входы которых соединены с выходами нечетных, начиная с младшего разряда, триггеров счетчика.

Посколькутакое изменение состояния с О

0 на 1 в счетчике в любой момент может происходить только в одном разряде, выходы дифференцирующих цепочек подключаются ко входам лолической схемы «ИЛИ. Сигнал 2 с выхода логической схемы «ИЛИ являетсясигналом изменения значения четности, а само значение четности определяется триггером четности кода, на счетный вход которого поступает сигнал изменения значения четности.

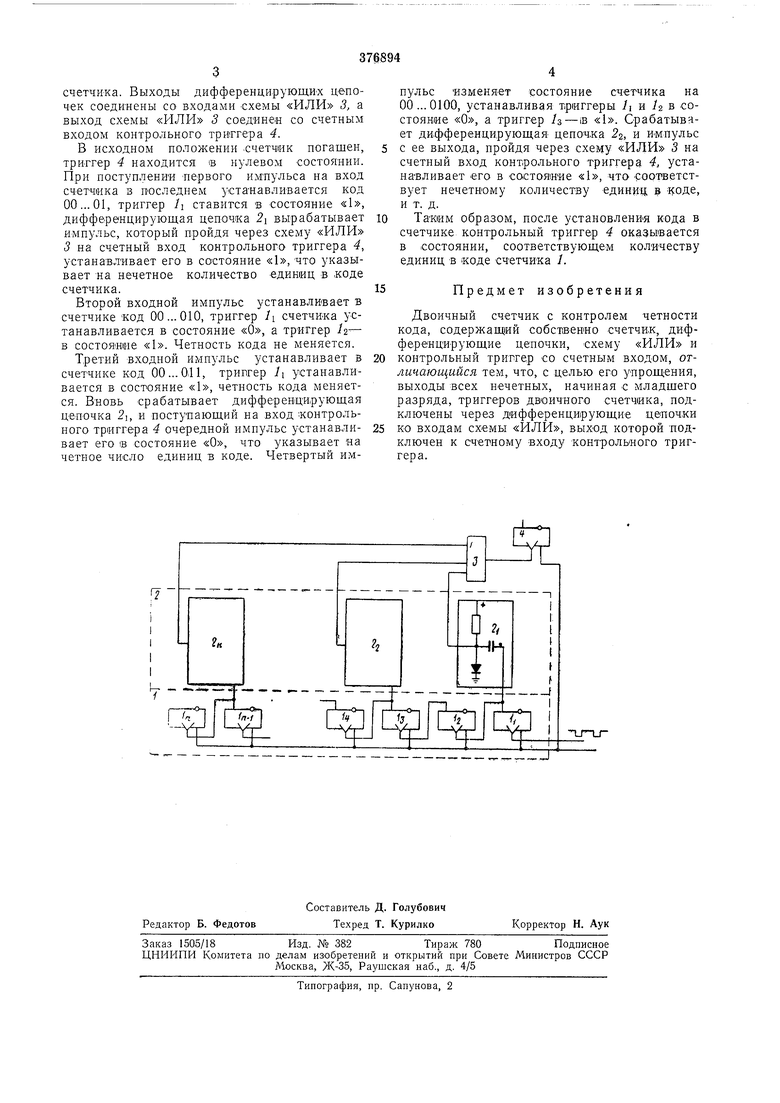

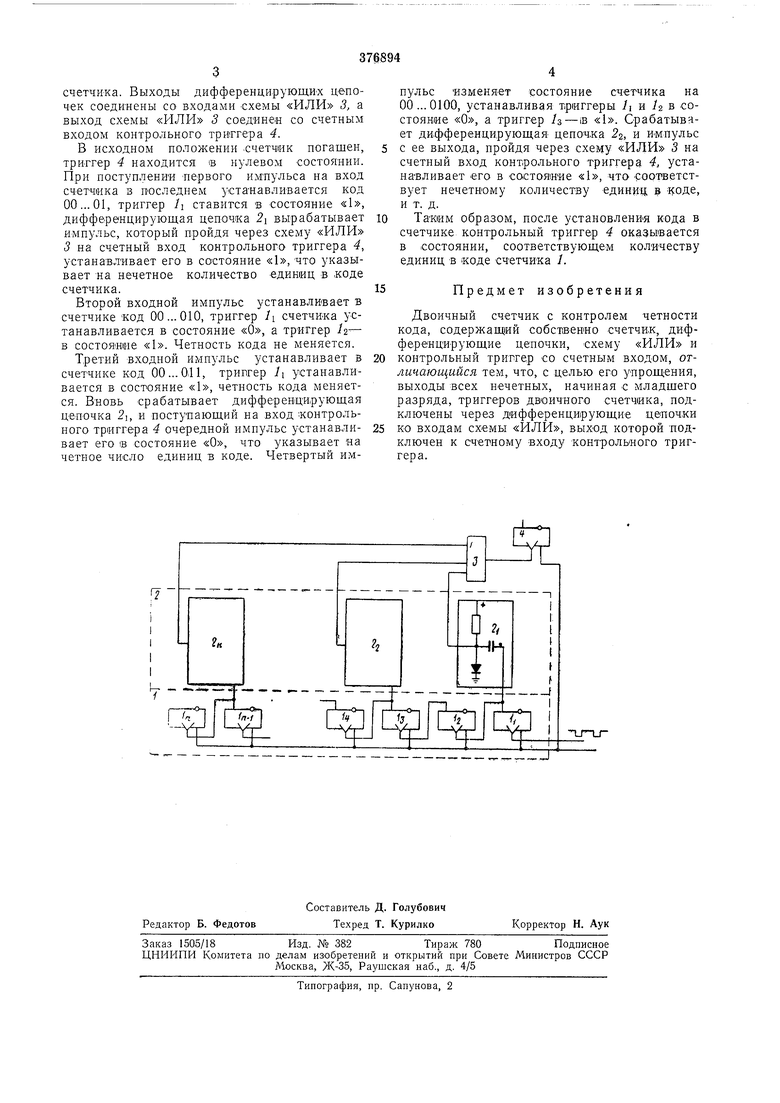

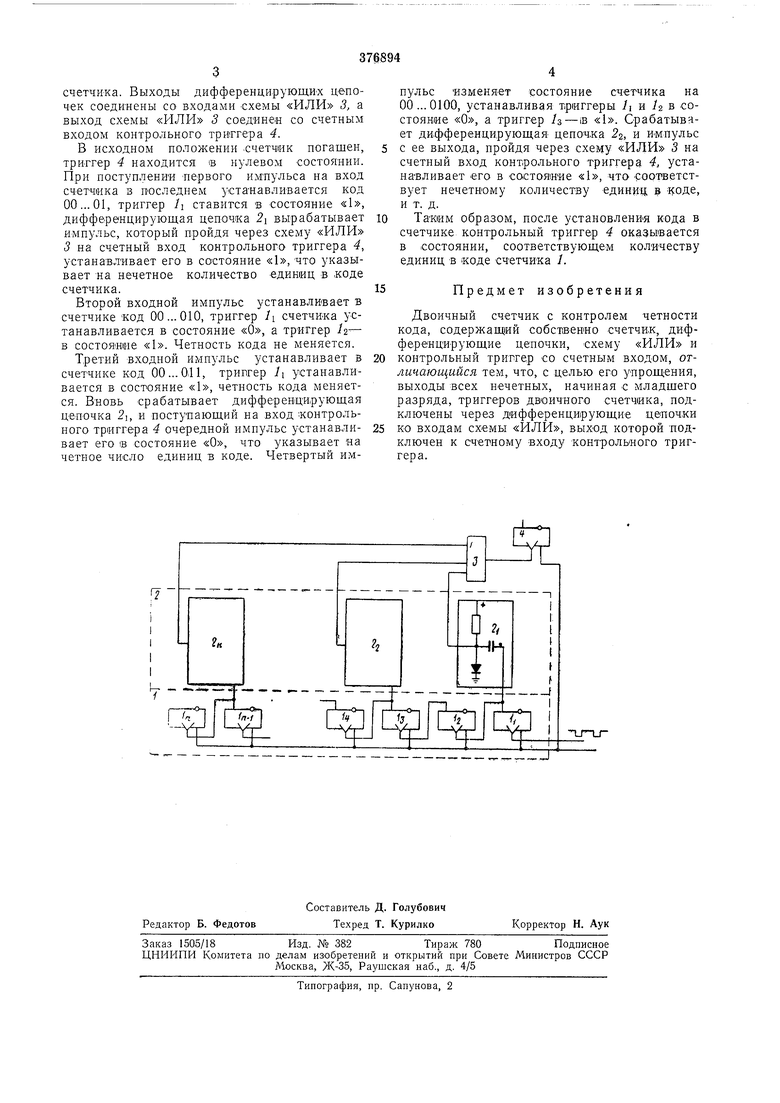

На чертеже изображен двоичный счетчик с

0 контролем четности кода. Для определенности принято, что количество разрядов в счетчике четно.

Описываемое устройство состоит из двоич5ного «-разрядного счетчика на триггерах li-In, дифференцирующих цепочек 2i-2k, схемы «ИЛИ 3 и контрольного триггера 4 со счетным входом. Входы дифференцирующих цепочек /i-In подключены к выходам нечетных, начиная с младшего разряда, триггеров

счетчика. Выходы дифференцирующих цепочек соединены со входами схемы «ИЛИ 3, а выход схемы «ИЛИ 3 соединен со счетным входом контрольного триггера 4.

В исходном положении .счетчик погашен, триггер 4 находится в нулевом состоянии. Ири поступлении первого импульса на вход счетчика в последнем устанавливается код 00 ...01, триггер /1 ставится в состояние «1, дифференцирующая цепочка 2i вырабатывает импульс, который пройдя через схему «ИЛИ 3 на счетный вход контрольного триггера 4, устанавливает его в состояние «1, что указывает на нечетное количество единиц в коде счетчика.

Второй входной импульс устанавливает в счетчике код 00 ...010, триггер Л счетчика устанавливается в состояние «О, а триггер h- в состояние «1. Четность кода не меняется.

Третий входной импульс устанавливает в счетчике код 00 ...011, триггер Л устанавливается в состояние «1, четность кода меняется. Вновь срабатывает дифференци.рующая цепочка 2i, и поступающий на вход контрольного триггера 4 очередной импульс устанавливает его в состояние «О, что указывает яа четное число единиц в коде. Четвертый импульс изменяет состояние счетчика на 00 ...0100, устанавливая триггеры /i и /2 в состояние «О, а триггер /з-IB «1. Срабатывает дифференцирующая цепочка 22, и импульс с ее выхода, пройдя через схему «ИЛИ 3 на счетный вход контрольного триггера 4, устанавливает его в со.стоя1ние «1, что соответствует нечетному количеству единиц в коде, и т. д.

Таким образом, после установленИЯ кода в счетчике контрольный триггер 4 оказывается в состоянии, соответствующем количеству единиц в коде счетчика /.

Предмет изобретения

Двоичный счетчик с контролем четности кода, содержащий собственно счетчик, дифференцирующие цепочки, схему «ИЛИ и контрольный триггер со счетным входом, отличающийся тем, что, с целью его упрощения, выходы всех нечетных, начиная с младщего разряда, триггеров двоичного счетчика, подключены через дифференцирующие цепочки ко входам схемы «ИЛИ, выход которой подключен к счетному входу контрольного триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| Устройство для фиксации входных импульсов в двоичном и двоично-рефлексном кодах | 1957 |

|

SU113928A1 |

| Счетчик | 1987 |

|

SU1437993A1 |

| Устройство формирования признака четности кода | 1970 |

|

SU518773A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

| СУММАТОР В КОДЕ ГРЕЯ | 1965 |

|

SU172131A1 |

| ОБНАРУЖЕНИЕМ ЕДИНИЧНЫХСБОЕВ | 1972 |

|

SU340097A1 |

| Счетчик с контролем на четность | 1981 |

|

SU1010728A1 |

| УСТРОЙСТВО для ИНТЕГРИРОВАНИЯ ФУНКЦИЙ в ДВОИЧНО-ДЕСЯТИЧНОМ ЦИКЛИЧЕСКОМ КОДЕ | 1967 |

|

SU203321A1 |

| Устройство для контроля двухтактного двоичного счетчика | 1975 |

|

SU607221A1 |

T-T-LT

Авторы

Даты

1973-01-01—Публикация