1

Изобретение относится к области вычислительной техники.

Известно арифметическое устройство, содержащее два 2п-разрядных регистра слагаемых, регист.р суммы, я-разрядный сумматор и схему управления.

Недостатком данного устройства является невозможность выполнения операций с комплексными числами.

С целью расширения функциональных возможностей предлагаемое устройство дополнительно содержит второй п-разрядный сумматор (с разрядами от («+) до 2п), два 2лразрядных коммутатора слагаемых и 2л-разрядный коммутатор результата, каждый разряд коммутаторов содержит две схемы «И, выходы которых соединены с соответствующими входами схемы «ИЛИ, первые входы первых схем «И коммутаторов соединены с первым входом схемы управления, первые входы вторых схем «И коммутаторов соединены со вторым выходом схемы управления, выходы схем «ИЛИ коммутаторов слагаемых подключены ко входам соответствующего разряда сумматоров, вторые входы пе:рвых схем «И коммутаторов слагаемых подключены к выходам соответствующих разрядов регистров слагаемых, вторые входы вторых схем «И т-го разряда коммутаторов слагаемых подключены к выходу т-го разряда .соответствующего регистра слагаемых, вторые входы вторых схем «И (2m-f 1)-го разряда коммутаторов слагаемых подключены к ()-ту разряду соответствующего регистра слагаемого, выходы схем «ИЛИ коммутатора результата соединены со входо.м соответствующего разряда регистра результата, вторые входы первых схем «И коммутатора результаты подключены к выходам соответствующих

разрядов сумматоров, вторые входы вторых схем «И т-го разряда (для tn,n) коммутатора результата подключены к вы.ходам 2т-ых разрядов сумматоров, вторые .входы вторых схем «И т-го разряда (для )

коммутатора результата подключены к выходам (2т-2rt+l)-ro разрядов сумматоров, выходы переноса я-го и 2я-го разрядов сумматоров соединены с первым и вторым входами схем управления, входы переноса в 1-й и

()-й разряды сумматоров соединены соответственно с третьим и четвертым выходами схемы упра(Вления.

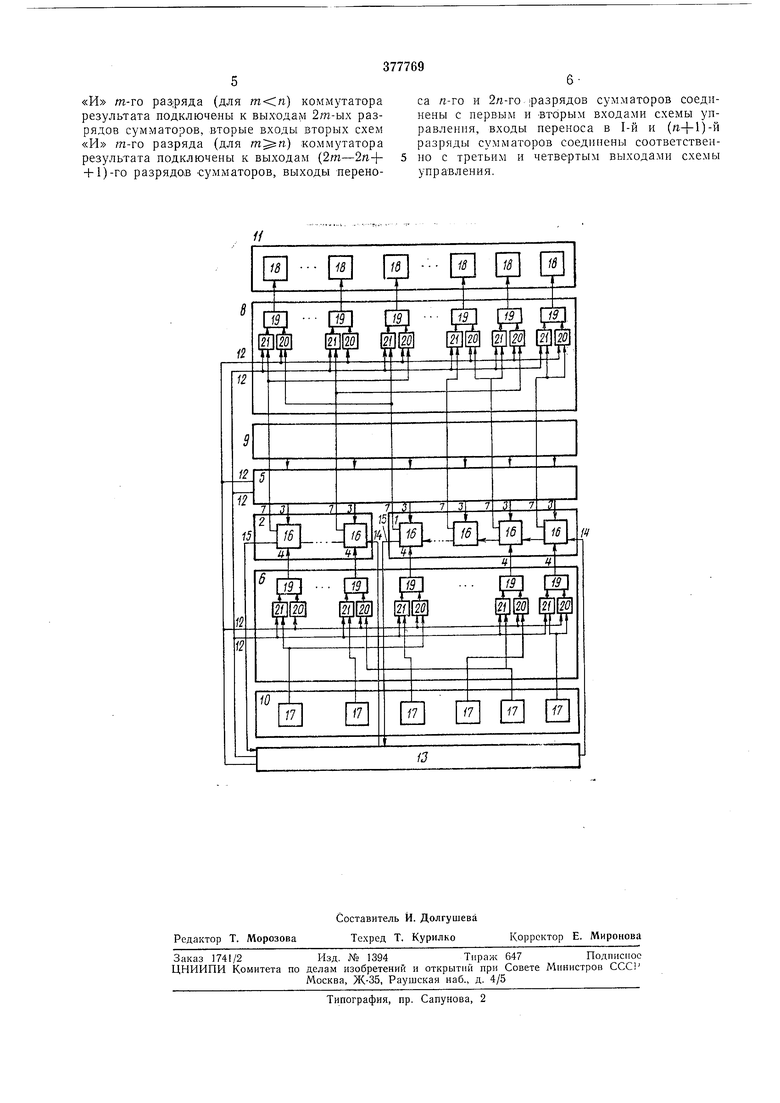

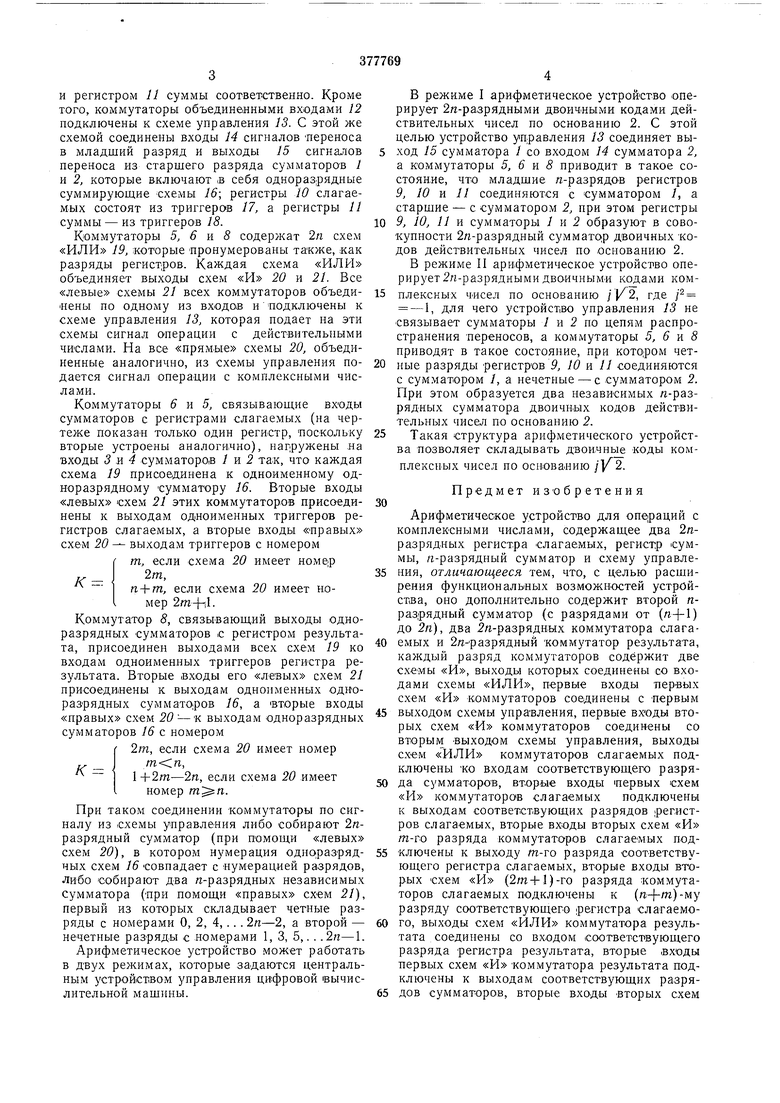

На чертеже представлена схема предлагаемого арифметического устройства.

Сумматоры / и 2 я-разрядных двоичных кодов по основанию 2 в.ходами 3 и 4 приооедипены к коммутаторам слагаемых 5 и 6, а выходами 7-к коммутатору 8 результата. Коммутаторы 5, б ,и 8, в свою очередь, связаны

с 2я-разрядными регистрами 9 и 10 слагаемых и регистром 11 суммы соответственно. Кроме того, коммутаторы объединенными входами 12 подключены к схеме управления 13. С этой же схемой соединены входы 14 сигналов переноса в младший разряд и выходы 15 сигналов переноса из старшего разряда сумматоров I и 2, которые включают ,в себя одноразрядные суммирующие схемы 16; регистры 10 слагаемых состоят из триггеров 17, а регистры 11 суммы - из триггеров 18. Коммутаторы 5, 6 w. 8 содержат 2я схем «ИЛИ 19, которые -пронумерованы также, .как разряды регистров. Каждая схема «ИЛИ объединяет выходы схем «И 20 и 21. Все «левые схемы 21 всех коммутаторов объединены по одному из входов и подключены к схеме управления 13, которая подает на эти схемы сигнал операции с действительными числами. На все «прямые схемы 20, объединенные аналогично, из схемы управления подается сигнал операции с комплексными чисКоммутаторы 6 и 5, связываюн;ие входы сумматоров с регистрами слагаемых (на чертеже показан только один регистр, поскольку вторые устроены аналогично), нагружены на входы 5 и 4 сумматоров / и 2 так, что каждая схема 19 присоединена к одноименному одноразрядному сумматору 16. Вторые входы «левых схем 21 этих коммутаторов присо-единены к выходам одноименных триггеров регистров слагаемых, а вторые входы «правых схе-м 20 - выходам триггеров с номером т, если схема 20 имеет номер п + т, если схема 20 имеет номер 2m-hl. Коммутатор 8, связывающий выходы одноразрядных сумматоров с регистром результата, присоединен выходами всех схем 19 ко входам одноименных триггеров регистра результата. Вторые входы его «левых схем 21 присоеди«ены к выходам одноименных одноразрядных сумматоров 16, а вторые входы «правых схем 20 -к выходам одноразрядных сумматоров 16 с номером 2т, если схема 20 имеет номер 1 +2т-2п, если схема 20 имеет номер . При таком соединении коммутаторы по сигналу из схемы управления либо собирают 2празрядный сумматор (при помощи «левых схем 20), в котором нумерация одноразрядных схем 76 совпадает с нумерацией разрядов, либо собирают два п-разрядных независимых Сумматора (при помощи «правых схем 21, первый из которых складывает четные разряды с номерами О, 2, 4, ... 2п-2, а второй - нечетные разряды с номерами 1, 3, 5,.. .2п-1. Арифметическое устройство может работать в двух режимах, которые задаются центральным устройством управления цифровой вычислительной машины. В режиме I арифметическое устройство оперирует 2п-разрядными двоичными кодами действительных чисел по основанию 2. С этой целью устройство управления 13 соединяет выход 15 сумматора / со входом 14 сумматора 2, а коммутаторы 5, б и 5 приводит в такое состояние, что младшие л-разрядов регистров 9, 10 и 11 соединяются с сумматором 1, а старшие - с сумматором 2, при этом регистры 9, 10, 11 и сумматоры / и 2 образуют в совокупности 2/г-разрядный суммато;р двоичных кодов действительных чисел по основанию 2. В режиме И ари:фметическое устройство оперирует 2п-разрядными двоичными кодами комплексных чисел по основанию / К2, где /2 -i для чего устройство управления 13 не связывает сумматоры 7 и 2 по цепям распространения -переносов, а коммутаторы 5, 6 8 приводят в такое состояние, при котором четные разряды регистров Я Юл П соединяются с сумматором /, а нечетные- с сумматором 2. При этом образуется два независимых /г-разрядных сумматора двоичных кодов действительных чисел по основанию 2. Такая структура арифметического устройства позволяет складывать двоичные коды комплексных чисел по основанию . Предмет изобретения Арифметическое устройство для операций с комплексными числами, содержащее два 2празрядных регистра слагаемых, регистр суммы, «-разрядный сумматор и схему управления, отличающееся тем, что, с целью расширения функциональных возможностей устройства, оно дополнительно содержит второй празрядный сумматор (с разрядами от () до 2п), два 2/г-разрядных коммутатора слагаемых и 2/г-разрядныЙ коммутатор результата, каждый разряд коммутаторов содержит две , выходь которых соединены со вхо хемы «ИЛИ, первые входы первых коммутаторов соединены с нервым вь1ходом схемы щраБл ен 1 я,перв ь е входь. вто рых схем «И коммутаторов соединены со вторым выходом схемы управления, выходы схем «ИЛИ коммутаторов слагаемых подключены ко входам соответствующего разряда сумматоров, вторые входы иервых схем «И коммутаторов слагаемых подключены к выходам соответствующих разрядов регистров слагаемых, вторые входы вторых схем «И т-го разряда коммутаторов слагаемых подключены к выходу т-го разряда соответствующего регистра слагаемых, вторые входы вторых схем «И (2m-f 1)-го разряда коммутаторов слагаемых подключены к ()-Щ разряду соответствующего регистра слагаемого, выходы схем «ИЛИ коммутатора результата соединены со входом соответствующего разряда регистра результата, вторые входы нервых схем «И коммутатора результата подключены к выходам соответствующих разрядов сумматоров, вторые входы вторых схем

«И m-го раз;ряда (для ) коммутатора результата подключены к выходам 2т-ых разрядов сумматоров, вторые входы вторых схем «И ш-го разряда (для ) коммутатора результата подключены к выходам (2т-2п-}+ 1)-го разрядо-в сумматоров, выходы переноса /1-го и 2д-го разрядов сумматоров соединены с первым и вторым входами схемы управления, входы переноса в 1-й и (п-)-1)-й разряды сумматоров соедннены соответственно с третьим и четвертым выходами схемы управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения | 1991 |

|

SU1807481A1 |

| Устройство для умножения | 1976 |

|

SU744563A1 |

| Матричное устройство для решения уравнений в частных производных | 1985 |

|

SU1302276A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1532918A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1981 |

|

SU991416A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1111155A1 |

| Сумматор в системе остаточных классов | 1983 |

|

SU1111170A1 |

Авторы

Даты

1973-01-01—Публикация