(54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Последовательное множительное устройство | 1981 |

|

SU1067500A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1056184A2 |

| Устройство для умножения с накоплением | 1982 |

|

SU1108087A1 |

| Устройство для умножения элементов конечных полей | 1984 |

|

SU1226445A1 |

| Устройство для умножения | 1988 |

|

SU1654814A2 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для умножения | 1984 |

|

SU1256016A1 |

| Устройство для умножения двух @ -разрядных чисел | 1988 |

|

SU1575174A1 |

| Устройство для умножения | 1978 |

|

SU896617A2 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при построении арифметических устройств ЦВМ, в системах цифровой фильтрации, в автоматизированных комплексах обработки информации.

Известны последовательные умножители, в которых образуется произведение сомножителей, поступающих последовательным кодом, начиная со старших разрядов, причем интервал времени между моментом выдачи произведения и моментом начала поступления сомножителей велик, так как результат вычислений формируется только прсле прихода последних младших разрядов сомножителей, .либо сомножители поступают последовательным кодом, начиная с младашх разрядов, при этом . частота поступления сомножителей низкая, так как выдача произведения производится последовательным кодом из 2П двоичных разрядов, а коды сомножителей содержат по п двоичных разрядов tlj и 2.

Наиболее близким к предлагаемому является устройство для умножения, содержсццее несколько последовательно . соединенных узлов умножения и шесть

электрически с ними связанных шин, первая и вторая шины соединены со входами узлов умножения, третья ши-., на соединяется с одним из входов узла умножения через элемент задержки, четвертая шина связана со вторыми входами узлов у Л1ожения, входы узлов умножения соединены через элемент задержки, либо через дополни10тельный элемент задержки, включенный между первой и второй шинами. Двоичные разряды произведения формируются в уэлах умножения путем формирования перекрестных произведений соответст вующих разрядов сомножителей и их суммирования. На вход устройства для умножения подается непрерывный поток пар сомножителей последовательно и с заданной скоростью, при этом сиг20налы , соответствующие младшим разрядам, поступают первыми. С выхода устройства выдается последовательный код .получаемого произведения 3.

25

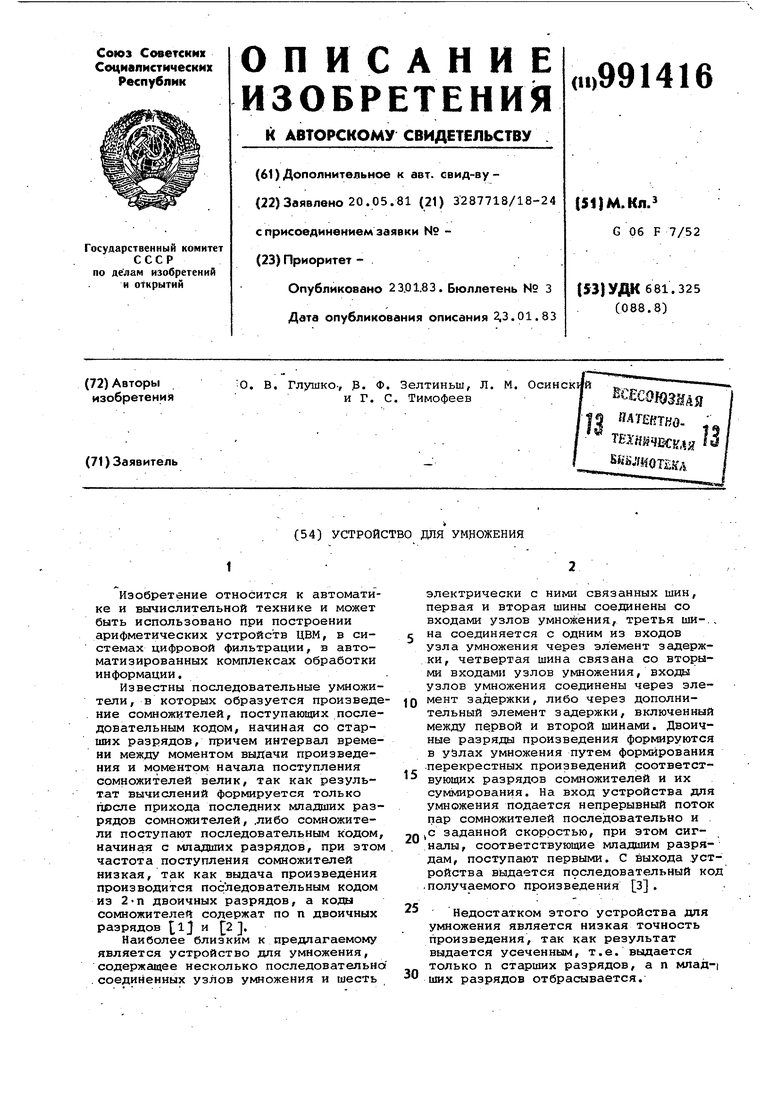

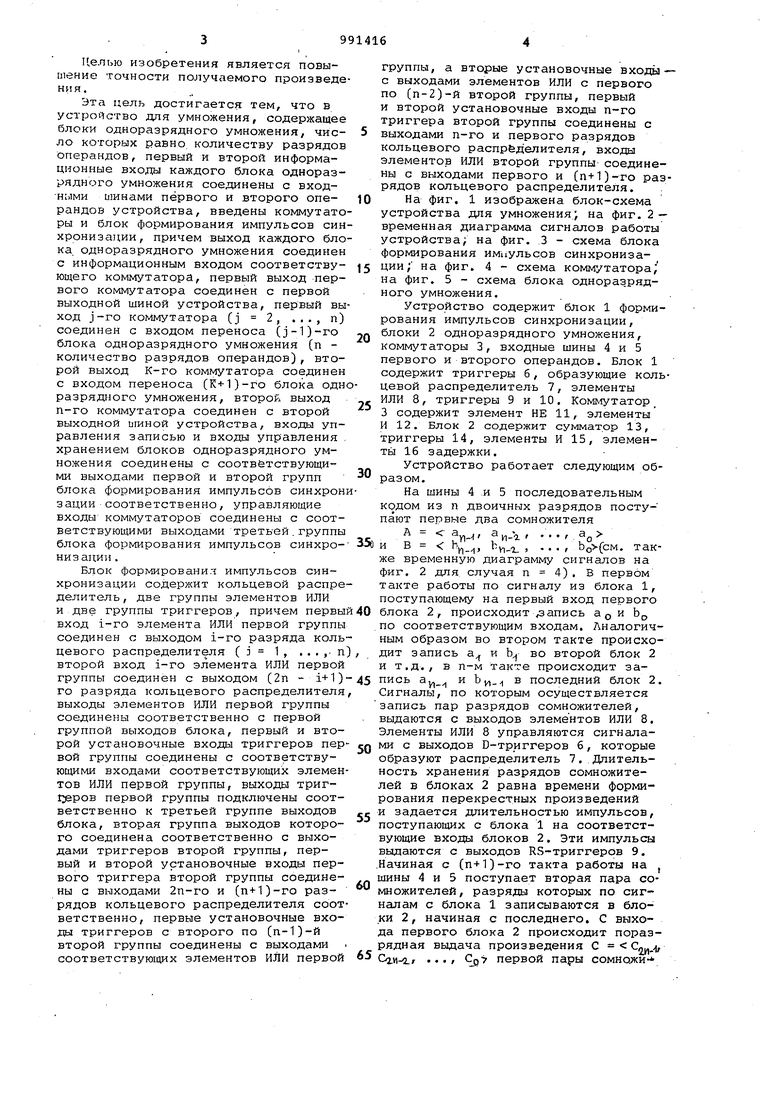

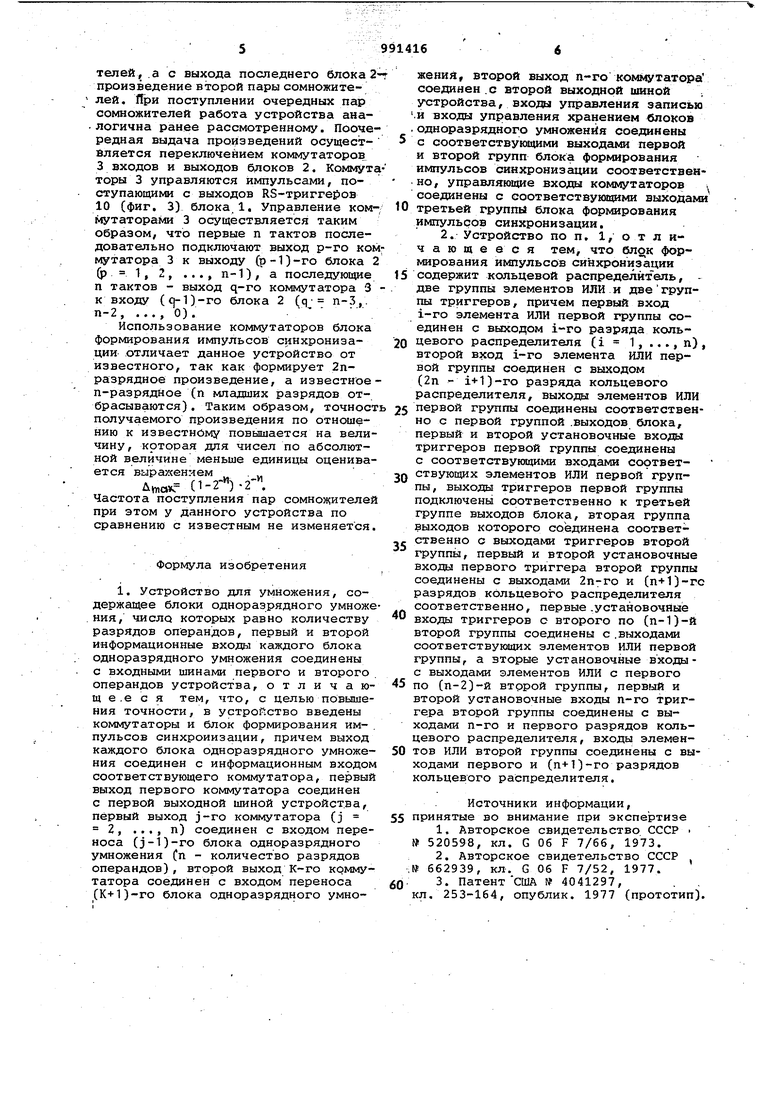

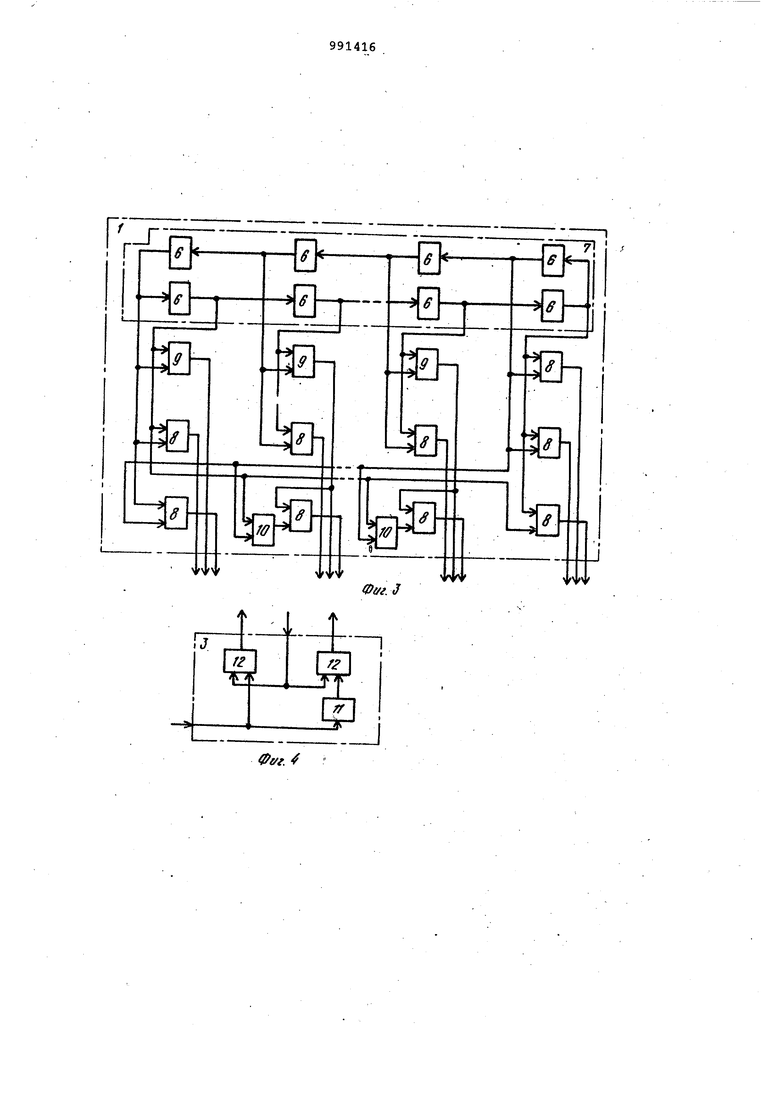

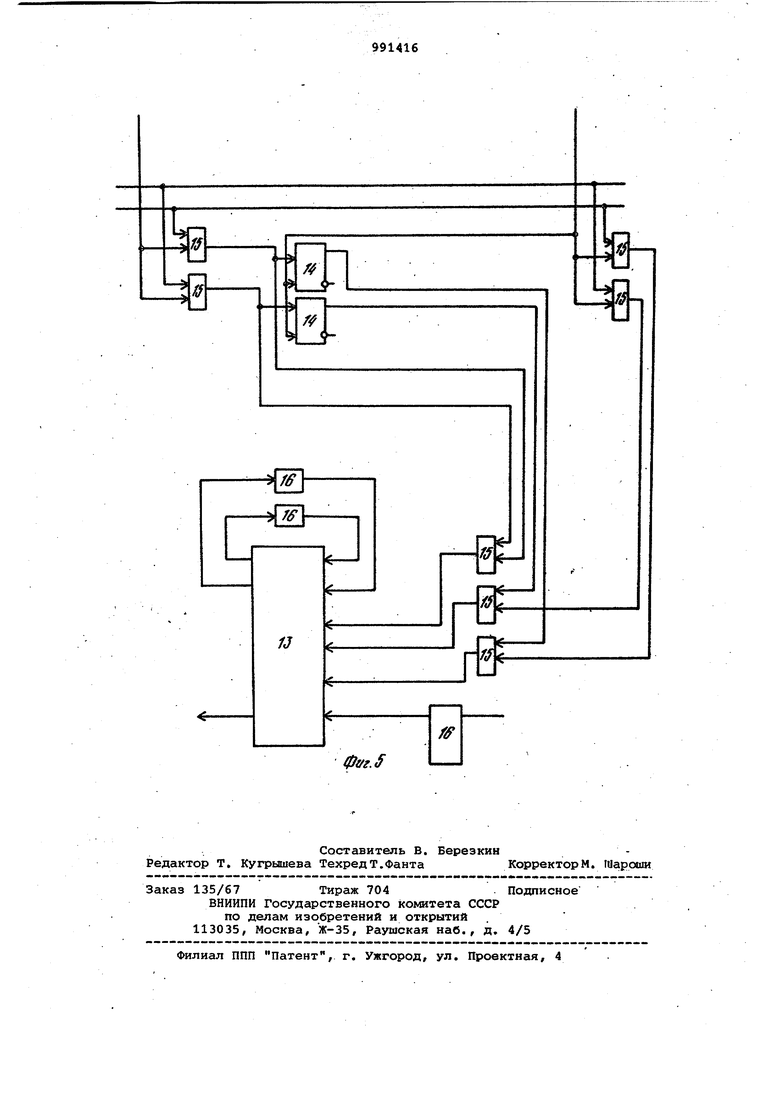

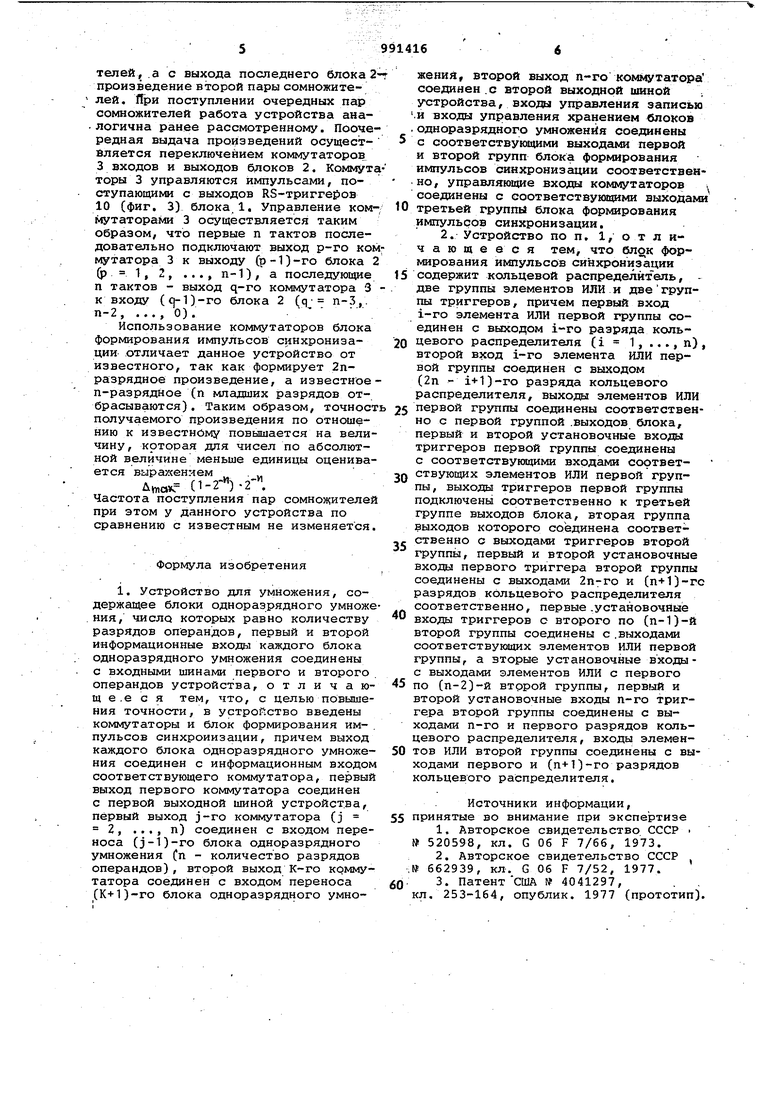

Недостатком этого устройства для умножения является низкая точность произведения, так как результат выдается усеченным, т.е. выдается только п старших разрядов, а п мпад30ших разрядов отбрасывается. ,елыо изобретения является повышение точности получаемого произведе ния. Эта цель достигается тем, что в устройство для умножения, содержащее блоки одноразрядного умножения, число которых равно, количеству разрядов операндов, первый и второй информационные входы каждого блока одноразрядного умножения соединены с входными шинами первого и второго oneрандов устройства, введены коммутато ры и блок формирования импульсов син хронизации, причем выход каждого бло ка одноразрядного умножения соединен с информационным входом соответствующего коммутатора, первый выход первого коммутатора соединен с первой выходной шиной устройства, первый вы ход j-ro коммутатора (j 2, ..., п) соединен с входом переноса (j-l)-ro блока одноразрядного умножения (п количество разрядов операндов), второй выход К-го коммутатора соединен с входом переноса СК+1)-го блока одн разрядного умножения, второй выход п-го коммутатора соединен с второй выходной ишной устройства, входы управления записью и входы управления , хранением блоков одноразрядного умножения соединены с соответствующими выходами первой и второй групп блока формирования импульсов синхрон зации соответственно, управляющие входы коммутаторов соединены с соответствующими выходами третьей.группы блока формирования импульсов синхронизации. БЛОК формирования импульсов синхронизации содержит кольцевой распре делитель , две группы элементов ИЛИ и две группы триггеров, причем первы вход i-ro элемента ИЛИ первой группы соединен с выходом i-ro разряда коль цевого распределителя ( i 1 , . . . ,. п второй вход i-ro элемента ИЛИ первой группы соединен с выходом С2п - ) го разряда кольцевого распределителя выходы элементов ИЛИ первой группы соединены соответственно с первой группой выходов блока, первый и второй установочные входы триггеров пер вой группы соединены с соответствующими входами соответствующих элемен тов ИЛИ первой группы, выходы триг1;;эров первой группы подключены соответственно к третьей группе выходов блока, вторая группа выходов которого соединена соответственно с выходами триггеров второй группы, первый и второй установочные входы первого триггера второй группы соединены с выходами 2п-го и (n-t-l)-ro разрядов кольцевого распределителя соот ветственно, первые установочные входы триггеров с второго по Сп-1)-й второй группы соединены с выходами соответствующих элементов ИЛИ первой группы, а вторые установочные входы - с выходами элементов ИЛИ с первого по (п-2)-й второй группы, первый и второй установочные входы п-го триггера второй группы соединены с выходами п-го и первого разрядов кольцевого распределителя, входы элементов ИЛИ второй группы соединены с выходами первого и (п+1)-го разрядов кольцевого распределителя. На фиг. 1 изображена блок-схема устройства для умножения; на фиг, 2 - временная диаграмма сигналов работы устройства; на фиг. 3 - схема блока формирования имиульсов синхронизации; на фиг. 4 - схема коммутатора на фиг. 5 - схема блока однораз.рядного умножения. Устройство содержит блок 1 формирования импульсов синхронизации, блоки 2 одноразрядного умножения, коммутаторы 3, входные шины 4 и 5 первого и второго операндов. Блок 1 содержит триггеры 6, образующие кольцевой распределитель 7, элементы ИЛИ 8, триггеры 9 и 10, Коммутатор 3 содержит элемент НЕ 11, элементы и 12. Блок 2 содержит сумматор 13, триггеры 14, элементы И 15, элементы 16 задержки. Устройство работает следующим образом. На шины 4 и 5 последовательным кодом из п двоичных разрядов поступают первые два сомножителя I f и-а и в ,, tvi-i. ) / bo(cM. так - ц--( . ) же временную диаграмму сигналов на фиг. 2 для случая п 4). В первом такте работы по сигналу из блока 1, поступающему на первый вход первого блока 2, происходит л апись а Q и bj, по соответствующим входам. Аналогичным образом во втором такте происходит запись а и Ь во второй блок 2 и т.д., в п-м такте происходит запись а и Ь в последний блок 2. Сигналы, по которым осуществляется запись пар разрядов сомножителей, выдаются с выходов элементов ИЛИ 8. Элементы ИЛИ 8 управляются сигналами с выходов D-триггеров 6, которые образуют распределитель 7. Длительность хранения разрядов сомножителей в блоках 2 равна времени формирования перекрестных произведений и задается длительностью импульсов, поступающих с блока 1 на соответствующие входы блоков 2. Эти импульсы выдаются с выходов КЗ-триггерсэв 9. .Начиная с (п-ь1)-го такта работы на , шины 4 и 5 поступает вторая пара сомножителей, разряды которых по сигналам с блока 1 записываются в блоки 2, начиная с последнего. С выхода первого блока 2 происходит поразрядная выдача произведения С С.-) CiH-if ... Ср7 первой пары сомноди- телей, .а с выхода последнего блока 2 произведение второй пары сомножителей. Яри поступлении очередных пар сомножителей работа устройства аналогична ранее рассмотренному. Поочередная выдача произведений осущестВляется переключением коммутаторов 3 входов и выходов блоков 2. Коммут торы 3 управляются импульсами, поступающими с выходов К5-тригге)ОВ 10 (фиг, 3) блока.1, Управление коммутаторами 3 осуществляется таким образом, что первые п тактов последовательно подключают выход р-го ком мутатора 3 к выходу (р-1)-го блока 2 1, 2, ..., п-1), а последующие п тактов - выход q-ro коммутатора 3 к входу (с)-1)-го блока 2 {q п-3,. п-2, ..., 0), Использование коммутаторов блока формирования импульсов синхронизации .отличает данное устройство от известного, так как формирует 2празрядное произведение, а известное п-разрядное (п младших разрядов отбрасываются). Таким образом, точност получаемого произведения по отношению к известному повышается на величину, которая для чисел по абсолютной величине меньше единицы оценивается выразхением , (1-2-)-2-, Частота поступления пар сомножителей при этом у данного устройства по сравнению с известным не изменяется Формула изобретения 1. Устройство для умножения, содержащее блоки одноразрядного умноже ния, число которых равно количеству разрядов операндов, первый и второй информационные входы каждого блока одноразрядного умножения соединены с входными шинами первого и второго операндов устройства, отличающ е.е с я тем, что, с целью повышения точности, в устройство введены коммутаторы и блок формирования импульсов синхронизации, причем выход каждого блока одноразрядного умножения соединен с информационным входом соответствующего коммутатора, первый выход первого коммутатора соединен с первой выходной шиной устройства, первый выход j-ro коммутатора (j 2, ..., п) соединен с входом переноса (j-l)-ro блока одноразрядного умножения (п - количество разрядов операндов), второй выход К-го крммутатора соединен с входом переноса СК+1)-го блока одноразрядного умножения, второй выход п-го ко№4утатора соединен.с второй выходной шиной устройства, входы управления записью .и входы управления хранением блоков одноразрядного умножения соединены с соответствующими выходами первой и второй групп блока формирования импульсов синхронизации соответственно, управляющие входы коммутаторов соединены с соответствующими выходами третьей группы блока формирования импульсов синхронизации, 2, Устройство по п, 1, о т л ичающееся тем, что блок формирования импульсов синхронизации содержит кольцевой распределйтель, две группы элементов ИЛИ.и двегруппы триггеров, причем первый вход i-ro элемента ИЛИ первой группы соединен с выходом i-ro разряда кольцевого распределителя (i 1 , .. ., п), второй вход i-ro элемента ИЛИ первой группы соединен с выходом (2п - )-ro разряда кольцевого распределителя, выходы элементов ИЛИ первой группы соеда1нены соответственно с первой группой .выходов блока, первый и второй установочные входы триггеров первой группы соединены с соответствукнцими входами соответствующих элементов ИЛИ первой группы, выходы триггеров первой группы подключены соответственно к третьей группе выходов блока, вторая группа выходов которого соединена соответственно с выходами триггеров второй группы, первый и второй установочные входы первого триггера второй группы соединены с выходами 2п-го и (п+1)-гс разрядов кольцевого распределителя соответственно, первые.установочные входы триггеров с второго по (п-1)-й второй группы соединены с .выходами соответствующих элементов ИЛИ первой группы, а вторые установочные входыс выходами элементов ИЛИ с первого по (п-2)-и втррой группы, первый и второй установочные входы п-го триггера второй группы соединены с выходами п-го и первого разрядов кольцевого распределителя, входы элементов ИЛИ второй группы соединены с выходами первого и (п+1)-го разрядов кольцевого распределителя. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР . № 520598, кл, G Об F 7/66, 1973, 2,Авторское свидетельство СССР , № 662939, кл. G 06 F 7/52, 1977. 3. ПатентСША № 4041297, кл. 253-164, опублик. 1977 (прототип).

n

t

4г/М

Ш3{0)

LI SitJft)

i

SitA

/йгЛЩ

n n n n rm n m rr

ub Of fff ffj fffffff fffffj ffj fff eft ffj fff fff eft Oj ffffff fff a, аод, at

из.

- --:Г - - - --г|1г.Д:- - Г -- I;- - - - -г- - Иб/X.f

Лл fis Qo Or 8f Sy-ia fj off & ft a 6r fff Лз /, ifffSr StX .

гтттпП П у

///

с, Cf Cf Cj ff cs sfftc e, c,Cj f fsCff yCefrCiCjCf

Co Cr Сг Cj CfCs Cff CjC CfCtCjC CfCeCfC,, C, Cf C,

П t

11

ru

n

П

Г1/

-1

nj

I-и

ri r

Ю

11

11

/

ri

n

OoVrUk «O .

ГТ1 rv

n m MM n ф1/г.г

1

У

L

//

t

Г4

//

1

Lb§.

5

Авторы

Даты

1983-01-23—Публикация

1981-05-20—Подача