СП

СО

ю

о

00

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических операций.

Цель изобретения - расширение функциональных возможностей за счет вычисления ряда чисел а( аа; а0 аэ; а ,.««, а т(-а.

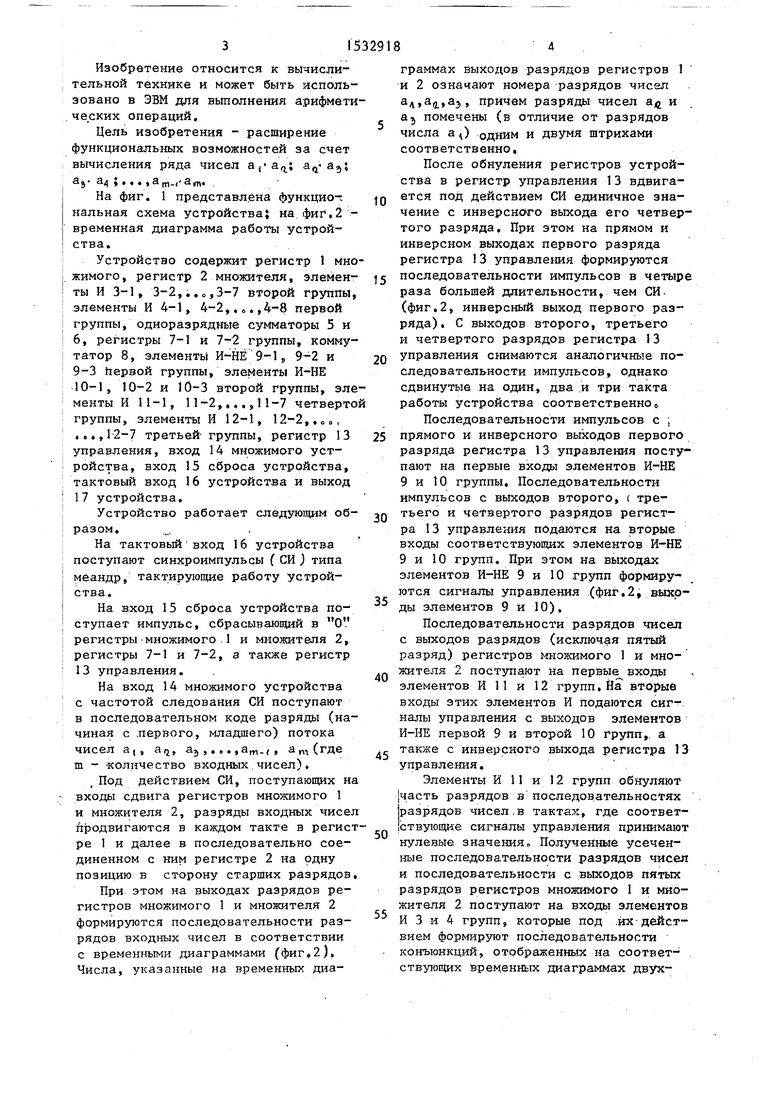

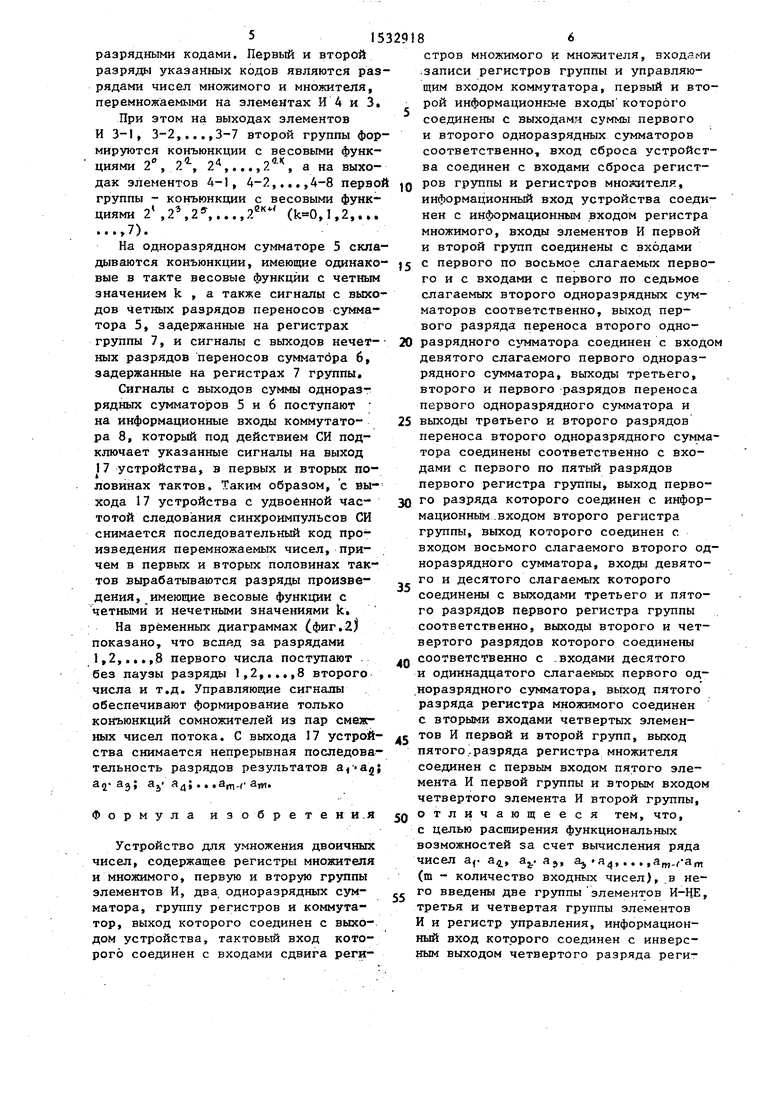

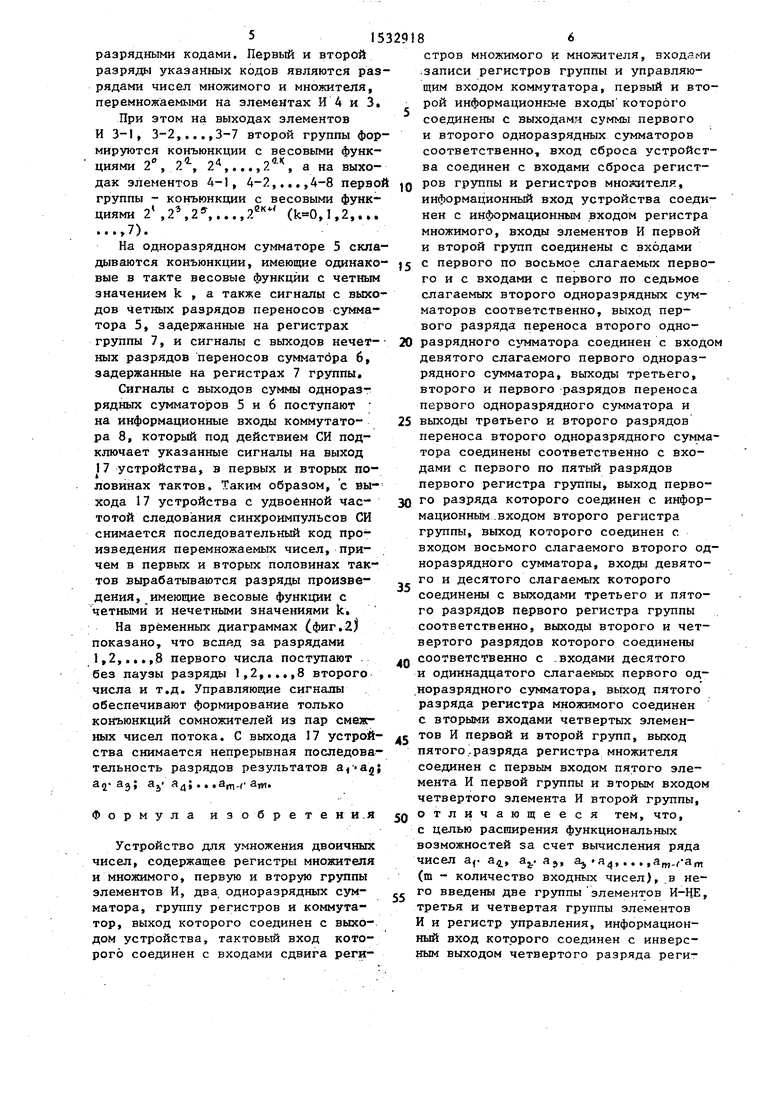

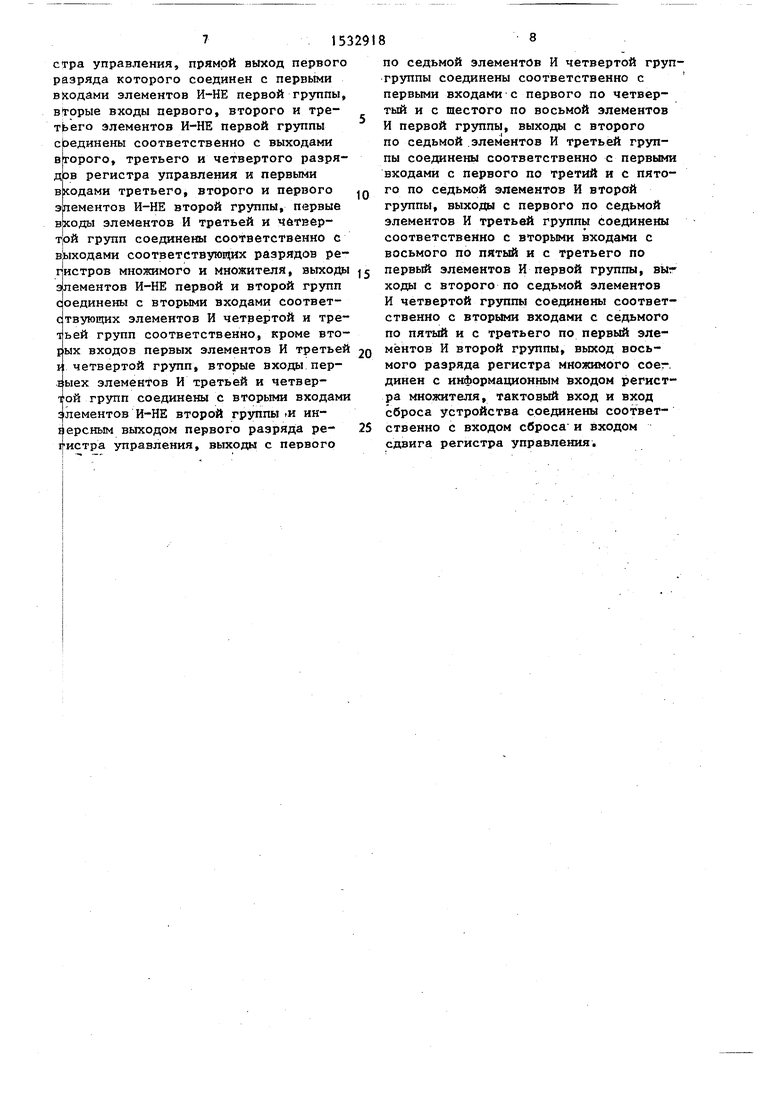

На фиг. 1 представлена функцио-, нальная схема устройства; на фиг.2 - временная диаграмма работы устройства.

Устройство содержит регистр 1 множимого, регистр 2 множителя, элементы И 3-1, 3-2,..о,3-7 второй группы, элементы И 4-1, 4-2,.„.,4-8 первой группы, одноразрядные сумматоры 5 и 6, регистры 7-1 и 7-2 группы, коммутатор 8, элементы И-НЕ 9-1, 9-2 и 9-3 первой группы, элементы И-НЕ 10-1, 10-2 и 10-3 второй группы, элементы И 11-1, 11-2,,,.,11-7 четверто группы, элементы И 12-1, 12-2,,,0, ...,12-7 третьей группы, регистр 13 управления, вход 14 множимого устройства, вход 15 сброса устройства, тактовый вход 16 устройства и выход 17 устройства.

Устройство работает следующим образом.

На тактовый вход 16 устройства поступают синхроимпульсы { СИ ) типа меандр, тактирующие работу устройства.

На вход 15 сброса устройства поступает импульс, сбрасывающий в О регистры множимого 1 и множителя 2, регистры 7-1 и 7-2, а также регистр 13 управления.

На вход 14 множимого устройства с частотой следования СИ поступают в последовательном коде разряды (начиная с первого, младшего) потока

чисел а,, а7, а5,...,ат,,

т

(где

т - количество входных чисел).

Под действием СИ, поступающих на входы сдвига регистров множимого 1 и множителя 2, разряды входных чисел продвигаются в каждом такте в регистре 1 и далее в последовательно соединенном с ним регистре 2 на одну позицию в сторону старших разрядов. При этом на выходах разрядов регистров множимого 1 и множителя 2 формируются последовательности разрядов входных чисел в соответствии с временными диаграммами (фиг,2), Числа, указанные на временных диа0

5

0

5

0

5

0

5

0

5

граммах выходов разрядов регистров 1 и 2 означают номера разрядов чисел ад,аа,аэ, причем разряды чисел ай и а помечены (в отличие от разрядов числа а А) одним и двумя штрихами соответственно.

После обнуления регистров устройства в регистр управления 13 вдвигается под действием СИ единичное значение с инверсного выхода его четвертого разряда. При этом на прямом и инверсном выходах первого разряда регистра 13 управления формируются последовательности импульсов в четыре раза большей длительности, чем СИ (фиг,2, инверсный выход первого разряда). С выходов второго, третьего и четвертого разрядов регистра 13 управления снимаются аналогичные последовательности импульсов, однако сдвинутые на один, два и три такта работы устройства соответственное

Последовательности импульсов с , прямого и инверсного выходов первого разряда регистра 13 управления поступают на первые входы элементов И-НЕ 9 и 10 группы. Последовательности импульсов с выходов второго, ( третьего и четвертого разрядов регистра 13 управления подаются на вторые входы соответствующих элементов И-НЕ 9 и 10 групп. При этом на выходах элементов И-НЕ 9 и 10 групп формируются сигналы управления (фиг.2, выходы элементов 9 и 10),

Последовательности разрядов чисел с выходов разрядов (исключая пятый разряд) регистров множимого 1 и множителя 2 поступают на первые входы элементов И 11 и 12 групп. На вторые входы этих элементов И подаются сигналы управления с выходов элементов И-НЕ первой 9 и второй 10 Групп, а также с инверсного выхода регистра 13 управления.

Элементы И 11 и 12 групп обнуляют |часть разрядов в последовательностях разрядов чисел в тактах, где соответствующие сигналы управления принимают нулевые значения. Полученные усеченные последовательности разрядов чисел и последовательности с выходов пятых разрядов регистров множимого 1 и множителя 2 поступают на входы элементов И 3 и 4 групп, которые под их действием формируют последовательности конъюнкций, отображенных на соответствующих временных диаграммах двухразрядными кодами. Первый и второй разряды указанных кодов являются разрядами чисел множимого и множителя, перемножаемыми на элементах И 4 и 3.

При этом на выходах элементов И 3-1, 3-2,...,3-7 второй группы формируются конъюнкции с весовыми функциями 2°, 2% 24,...,2ак, а на выходах элементов 4-1, 4-2,...,4-8 первой группы - конъюнкции с весовыми функциями 2 ,2,2ff, ..., (k-0,I,2f... )

На одноразрядном сумматоре 5 складываются конъюнкции, имеющие одинаковые в такте весовые функции с четным значением k , а также сигналы с выходов четных разрядов переносов сумматора 5, задержанные на регистрах группы 7, и сигналы с выходов нечетных разрядов переносов сумматора 6, задержанные на регистрах 7 группы.

Сигналы с выходов суммы одноразрядных сумматоров 5 и 6 поступают на информационные входы коммутатора 8, который под действием СИ подключает указанные сигналы на выход 17 устройства, в первых и вторых половинах тактов. Таким образом, с выхода 17 устройства с удвоенной частотой следования синхроимпульсов СИ снимается последовательный код произведения перемножаемых чисел, причем в первых и вторых половинах тактов вырабатываются разряды произведения, имеющие весовые функции с четными и нечетными значениями k.

На временных диаграммах (фиг.2) показано, что всляд за разрядами 1,2,...,8 первого числа поступают без паузы разряды 1,2,...,8 второго числа и т.д. Управляющие сигналы обеспечивают формирование только конъюнкций сомножителей из пар смежных чисел потока. С выхода 17 устройства снимается непрерывная последовательность разрядов результатов аа« аэ; аъ- а4;.. , aw.

ормула изобретения 50

д5 сс

Устройство для умножения двоичных чисел, содержащее регистры множителя и множимого, первую и вторую группы элементов И, два одноразрядных сумматора, группу регистров и коммутатор, выход которого соединен с выходом устройства, тактовый вход которого соединен с входами сдвига реги0

0

стров множимого к множителя, входями записи регистров группы и управляющим входом коммутатора, первый и второй информационные входы которого соединены с выходамч суммы первого и второго одноразрядных сумматоров соответственно, вход сброса устройства соединен с входами сброса регистров группы и регистров множителя, информационный вход устройства соединен с информационным входом регистра множимого, входы элементов И первой к второй групп соединены с входами

5 с первого по восьмое слагаемых первого и с входами с первого по седьмое слагаемых второго одноразрядных сумматоров соответственно, выход первого разряда переноса второго одно0 разрядного сумматора соединен с входом девятого слагаемого первого одноразрядного сумматора, выходы третьего, второго и первого разрядов переноса первого одноразрядного сумматора и

5 выходы третьего и второго разрядов переноса второго одноразрядного сумматора соединены соответственно с входами с первого по пятый разрядов первого регистра группы, выход перво0 го разряда которого соединен с информационным входом второго регистра группы, выход которого соединен с входом восьмого слагаемого второго одноразрядного сумматора, входы девятого и десятого слагаемых которого соединены с выходами третьего и пятого разрядов первого регистра группы соответственно, выходы второго и четвертого разрядов которого соединены соответственно с входами десятого и одиннадцатого слагаемых первого одноразрядного сумматора, выход пятого разряда регистра множимого соединен с вторыми входами четвертых элемен5 тов И первой и второй групп, выход пятого.разряда регистра множителя соединен с первым входом пятого элемента И первой группы и вторым входом четвертого элемента И второй группы, отличающееся тем, что, с целью расширения функциональных возможностей sa счет вычисления ряда чисел аг а, aj/ аэ, aj а, ... ,am,-am (m - количество входных чисел), в не- го введены две группы элементов И-НЕ, третья и четвертая группы элементов И и регистр управления, информационный вход которого соединен с инверсным выходом четвертого разряда реги5

0

стра управления, прямой выход первого разряда которого соединен с первыми входами элементов И-НЕ первой группы, вторые входы первого, второго и тре- тЬего элементов И-НЕ первой группы соединены соответственно с выходами второго, третьего и четвертого разрядов регистра управления и первыми входами третьего, второго и первого элементов И-НЕ второй группы, первые входы элементов И третьей и четвертой групп соединены соответственно с выходами соответствующих разрядов регистров множимого и множителя, выходы элементов И-НЕ первой и второй групп соединены с вторыми входами соответствующих элементов И четвертой и третьей групп соответственно, кроме вторых входов первых элементов И третьей v четвертой групп, вторые входы пер- Еыех элементов И третьей и четвертой групп соединены с вторыми входами элементов И-НЕ второй группы и ин- ерсным выходом первого разряда ре- гистра управления, выходы с первого

по седьмой элементов И четвертой труп группы соединены соответственно с первыми входами с первого по четвертый и с шестого по восьмой элементов И первой группы, выходы с второго по седьмой элементов И третьей группы соединены соответственно с первыми входами с первого по третий и с пятого по седьмой элементов И второй группы, выходы с первого по седьмой элементов И третьей группы соединены соответственно с вторыми входами с восьмого по пятый и с третьего по первый элементов И первой группы, выг- ходы с второго по седьмой элементов И четвертой группы соединены соответственно с вторыми входами с седьмого по пятый и с третьего по первый элементов И второй группы, выход восьмого разряда регистра множимого соег динен с информационным входом регистра множителя, тактовый вход и вход сброса устройства соединены соответственно с входом сброса и входом сдвига регистра управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1988 |

|

SU1509877A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1765839A1 |

| Устройство для умножения двоичных чисел | 1987 |

|

SU1439579A1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Устройство для умножения двоичных чисел | 1988 |

|

SU1587498A1 |

| Устройство для умножения чисел с контролем | 1988 |

|

SU1621033A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для вычисления полиномов | 1987 |

|

SU1509878A1 |

| Вычислительная ячейка | 1985 |

|

SU1287145A1 |

| Устройство для умножения | 1989 |

|

SU1732341A1 |

Изобретение относится к вычислительной технике и может быть использовано в ЭВМ для выполнения арифметических операций. Цель изобретения - расширение функциональных возможностей за счет вычисления ряда чисел A1.A2, A2.A3, A3.A4,....,AM-1.AM. Новым в устройстве, содержащем регистры множимого 1 и множителя 2, две группы элементов И 3 и 4, два одноразрядных сумматора 5 и 6, группу регистров 7 и коммутатор 8, является введение двух групп элементов И-НЕ 9,1-9,3 и 10,1-10,3 и двух групп элементов И 11,1-11,7 и 12,1-12,7. Числа поступают на вход устройства непрерывным потоком. Группы элементов И 11 и 12 под действием сигналов управления с элементов И-НЕ 9,1-9,3 и 10,1-10,3 обеспечивают формирование только конъюнкций сомножителей из пар смежных чисел. Результат считывается с выхода устройства каждые полтакта. 2 ил.

| Устройство для умножения | 1984 |

|

SU1203512A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-30—Публикация

1988-05-30—Подача