1

Изобретение относится к вычислительной техникеИ может быть использовано, например, в управляющих вычислительных машинах в качестве программно-управляемого -канала обмена дискретной информацией между устройством Вычислителя и адресуемыми внешними источниками и при,емникамн цифровой информации.

Известны устройства для связи цифровой вычислительной машины с объектами, содержащие дешифратор адресов, выходы которого подключены к входам вентилей выборки, .выходы вентилей -соединены с входам1И соответствующих собирательных схем и с управляющими входами источников и ПрИ€МНИКОВ СИГналОВ, и эм(иттерные повтО:рители.

Предлагаемое устройство отличается тем, что в нем выходы источников сигналов через эмиттерные повторители поразрядно связаны с входами нриемников сигналов и с выходами соответствующих эмиттерных повторителей, включенных в одну из цепей обратной связи разрядного триггера, подключенного входом к выходной кодовой шине. Шина запроса подсоединена к линии связи через дополнительно введенный триггер, сбросовый вход которого подключен к шине ответа, а выход - к сбросовым входам разрядных триггеров. Это позволяет повысить надежность устройства в работе и расширить нагрузочную и собирательную способность линий связи.

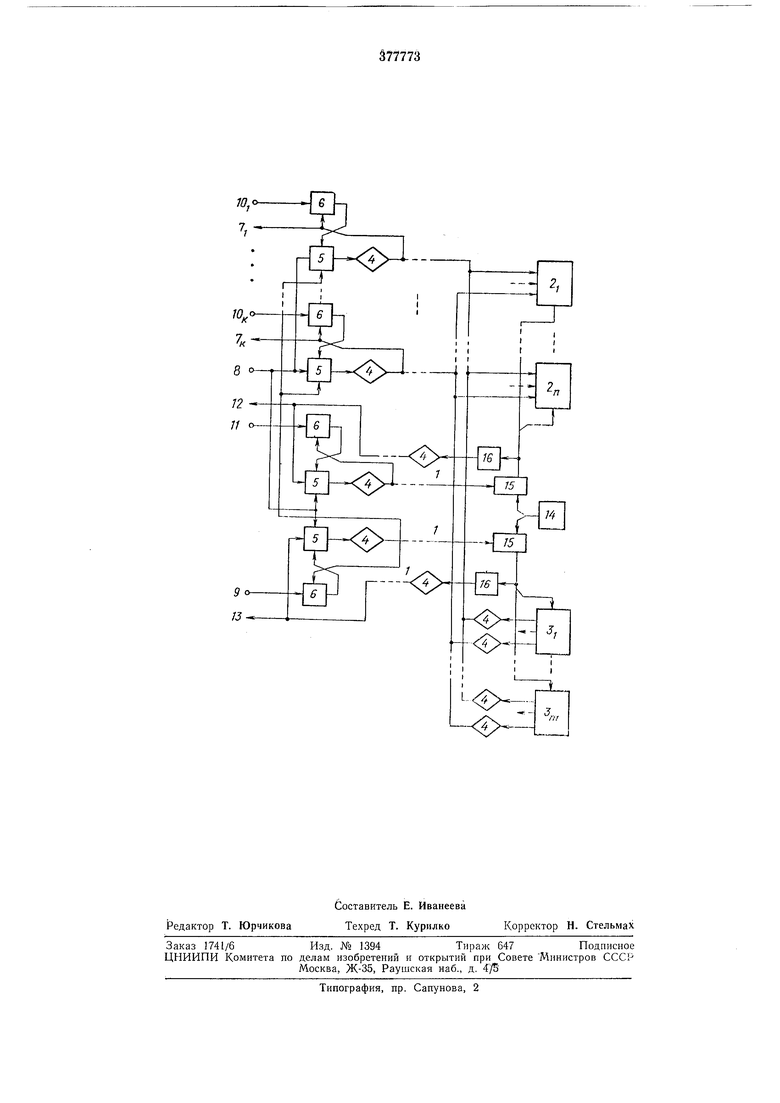

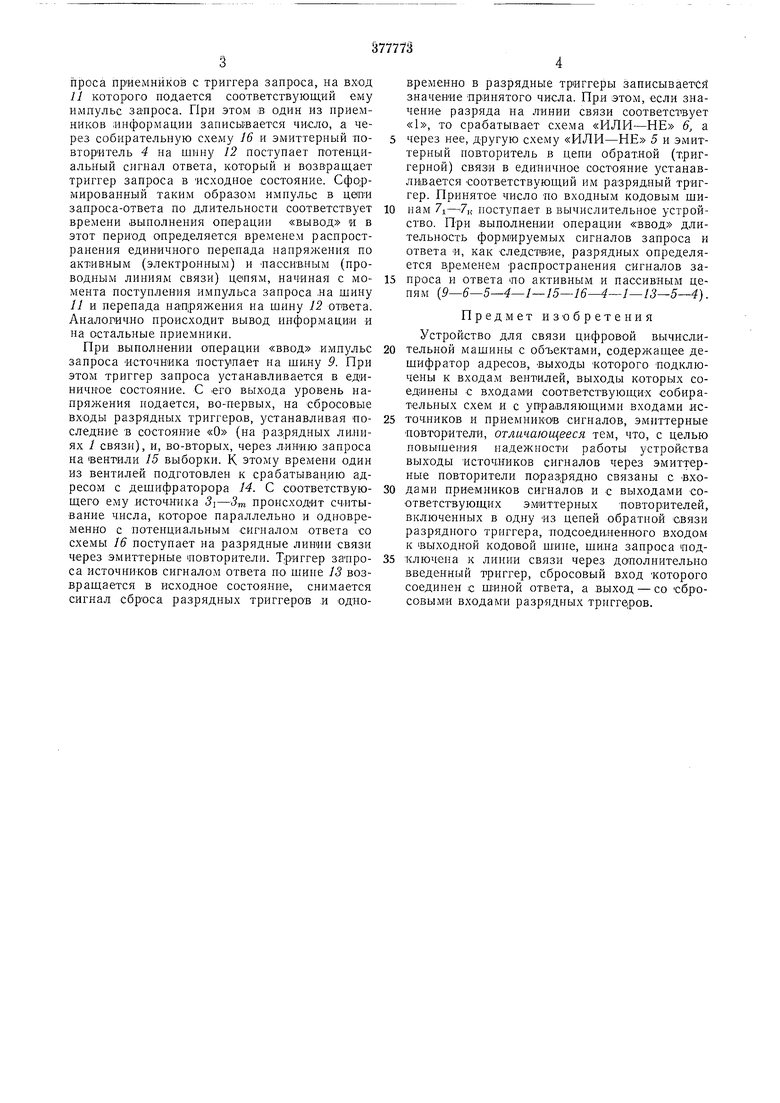

На чертеже показана функциональная схема предлагаемого устройства.

Устройство содержит дистанционные провод,ные линии / связи, прие.мники 2i-2п и источники параллельной цифровой информации, эмиттерные повторители 4, схемы 5 и 6, входные кодовые (разрядные) ишны 7)-7к, шину 8 сброса, шииу 9 запроса источников информации, выходные кодовые (разрядные) шины lOi-/f,;, шину 1/ запроса приемников информации, шины 12 п 13 ответов соответственно от приемников и источников информации, дешифраторов 14 адресов, вентили 15 выборки и собирательные схемы 16 ответов источников и приемников информации.

При выполнении операции «вывод число с

шин. lOi-WK вычислительного устройства записывается в триггеры (схемы 4-5-6) регистра, предварительно устаиавливаемого в исходное состояние сигналО М сброса с шины 8. По разрядным линиям / связи оно поступает

на входы всех приемников 2i-2„ информации. Адресом с дешифратора 14 (шины -и линии связи кода адреса на чертеже опущены) один из вентилей 15 подгото.влен к срабатыванию. Последнее происходит при иоступлеиии на его

управляющийВ.ход потенцнального сигнала запроса приемников с триггера запроса, на вход /) которого подается соответствующий ему импульс запроса. При этом iB один из приемников «информации записывается число, а через собирательную схему J6 и эмиттерный повторитель 4 на шину 12 поступает потенциальный сигнал ответа, который и возвращает триггер запроса в исходное состояние. Сформированный таким образом имнульс в цепи запроса-ответа по длительности соответствует времени выполнения операции «вывод и в этот период определяется временем распространения единичного переиада нанряжения по активным (электронным) и пассивным (проводным линиям связи) цепям, начиная с момента поступления импульса запроса ,на шину 11 и перепада напряжения на шину 12 ответа. Аналогично происходит вывод информации и на остальные приемники.

При выполнении операции «ввод импульс запроса источника иоступает на шину 9. При этом триггер запроса устанавливается в единичное состояние. С его выхода уровень напряжения подается, во-первых, на сбросовые входы разрядных триггеров, устанавливая последние Б состояние «О (на разрядных ли.ниях 1 связи), и, во-вторых, через линию запроса на вентили 15 выборки. К этому времени один из вентилей подготовлен к срабатыванию адресом с дешифраторора М. С соответствующего ему источника происходит считывание числа, которое параллельно и одновременно с потенциальным сигналом ответа со схемы 16 поступает на разрядные линии связи через эмиттерные повторители. Триггер запроса источников сигналом ответа по шине 13 возвращается в исходное состояние, снимается сигнал сброса разрядных триггеров и одновременно в разрядные триггеры записываетСй значение принятого числа. При этом, если значение разряда на линии связи соответствует «1, то срабатывает схема «ИЛИ-НЕ 6, а через нее, другую схему «ИЛИ-НЕ 5 и эмиттерный повторитель в цепи обратной (триггерной) связи в единичное состояние устанавли|вается соответствующий им разрядный триггер. Принятое число по входным кодовым щинам 7i-7к поступает в вычислительное устройство. При выполнении операции «ввод длительность формируемых сигналов запроса и ответа и, как следствие, разрядных определяется временем распространения сигналов запроса и ответа по активным и пассивным цепям (9 6-5-4-1-15-16 4-1-13-5-4).

Предмет изобретения

Устройство для связи цифровой вычислительной машины с объектами, содержащее дещифратор адресов, выходы которого -подключены к входам вентилей, выходы которых соединены с входами соответствующих собирательных схем и с управляющими входами источников и приемников сигналов, эмиттерные повторители, отличающееся тем, что, с целью повышения надежности работы устройства выходы источников сигналов через эмиттерные повторители поразрядно связаны с входа ми приемников сигналов и с выходами соответствующих эмиттерных повторителей, включенных в одну из цепей обратной связи разрядного триггера, подсоединенного входом к выходной кодовой щине, щина запроса иодключена к линии связи через дополнительно введенный триггер, сбросовый вход которого соединен с шиной ответа, а выход - со сбрОсовыми входами разрядных триггеров.

9о

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| УНИВЕРСАЛЬНАЯ ЦИФРОВАЯ УПРАВЛЯЮЩАЯ МАШИНА | 1965 |

|

SU170218A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА В ЧИСЛО-ИМПУЛЬСНЫЙ КОД | 1972 |

|

SU343264A1 |

| Устройство для обмена информацией между абонентами | 1986 |

|

SU1383376A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЕ — КОД С ЦИФРОВОЙ АВТОКОРРЕКЦИЕЙ НУЛЯ | 1967 |

|

SU196452A1 |

| Устройство для сопряжения канала ввода-вывода с внешними устройствами | 1980 |

|

SU955017A1 |

| Устройство для защиты от ошибок | 1972 |

|

SU503276A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НЕСАНКЦИОНИРОВАННОГО ДОСТУПА | 2002 |

|

RU2221270C2 |

| ПРИОРИТЕТНОЕ УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1970 |

|

SU281901A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

Авторы

Даты

1973-01-01—Публикация