Изобретение относится к цифровой вычислительной технике и, в частности, к организации структур цифровых вычислительных систем.

Известны приоритетные устройства для цифровой вычислительной системы, содержащие регистры, тр.иггеры, логические схемы совпадения, схемы «ИЛР1, дешифраторы я схемы задержки.

Известные приоритетные устройства не обеспечивают разрешение конфликтов при одновременной выработке нескольких сигналов ответа в один источник запроса, что ограничивает их применимость.

Предлагаемое л стройство отличается тем, что содержит Р приоритетных схем блоков оператив.НОЙ памяти (где Р - количество блоков памяти) и К логических схем, содержаш,их триггеры хранения сигналов готовности блоков оперативной памяти и ждущий мультивибратор формирования сигналов опроса триггеров храпения (где К - количество вычислителей в системе), причем первый выход каждого триггера хранения сигналов готовности подключен к первому входу первой группы схем совпадения, второй выход соеди.нен с первым входом второй группы схем совладения, второй вход крайних левых первой и второй групп схем совпадения подключен к ждущему мультивибратору формирования

сигналов опроса триггеров хранения, второй вход каждой первой ai второй групп схем совпадения (f-й при отсчете слева) по.дключен к выходу (i-1)-й второй группы схем совпадения, выходы первой группы схем совпадения подключены к первым входам третьей группы схем совпадения, вторые входы которых связаны с регистрами хранения старшей части адреса оперативной памяти, выходы

третьей группы схем совпадения присоединены к шине сигнала готовности блока оперативной памяти, выход крайней правой схемы совпадения из второй группы схем совпадения подключен ко входу запрета генерации ждущего мультивибратора, вход запуска которого соединен с выходом схемы задержки, вход схемы задержки связан с первой схемой «ИЛИ, входы которой соединены с шинами сигналов разрешения конфликтов, выход каждои схемы совпадения из первой группы схем совпадения связан со входом установки в ноль соответствующего триггера хранения.

Предлагаемое устройство отличается также тем, что в нем каждая приоритетная схема

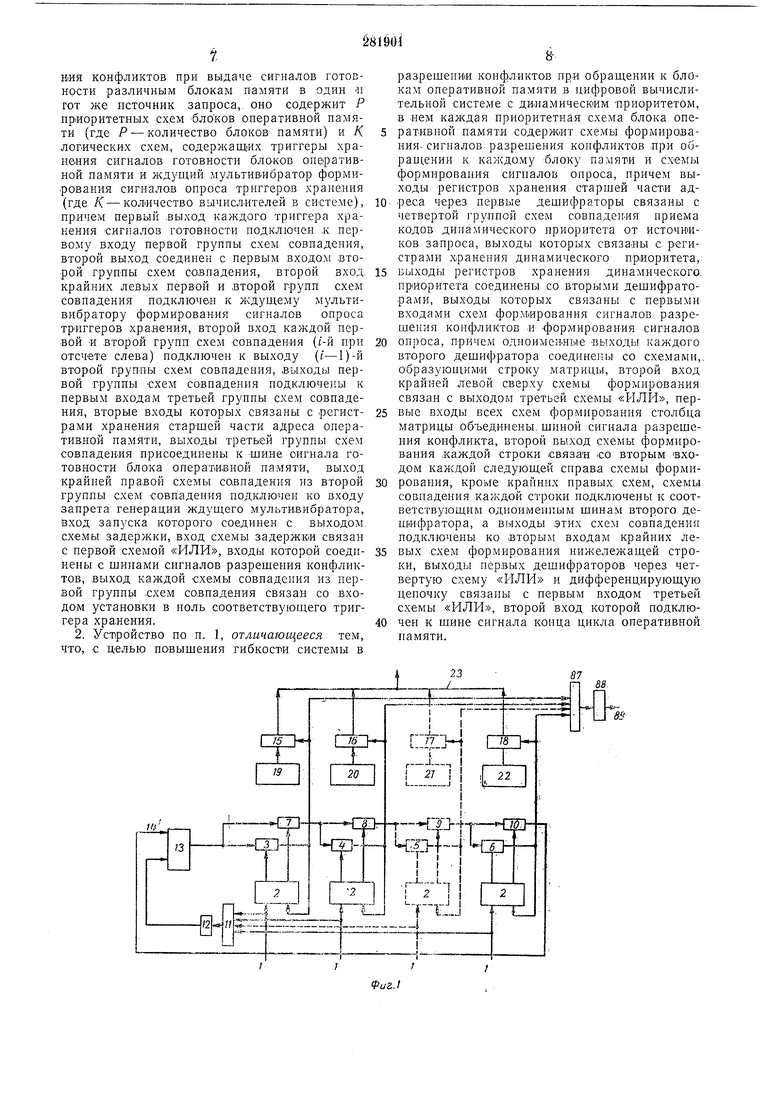

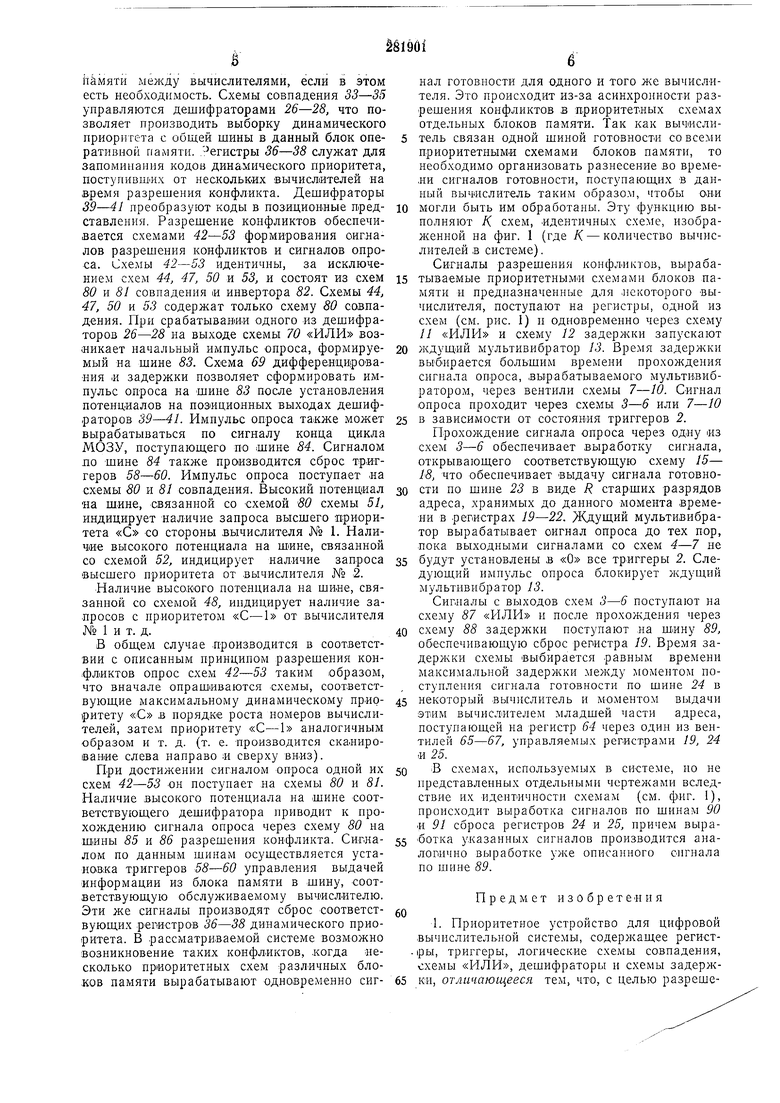

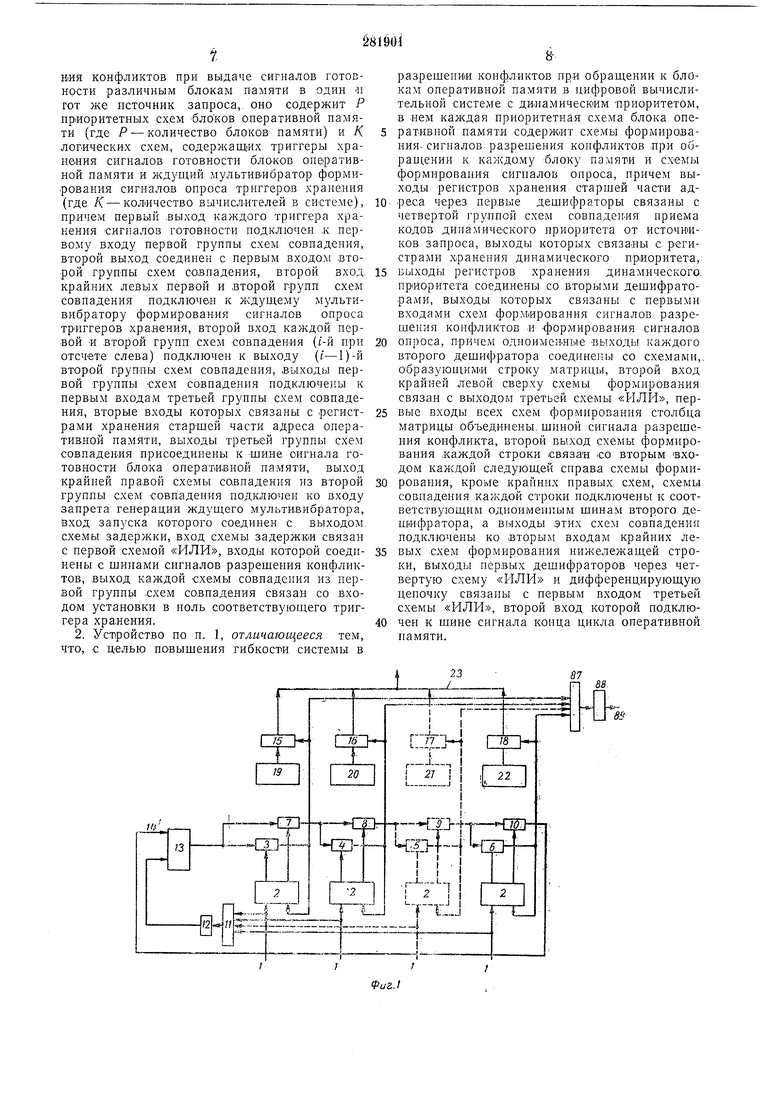

блока оперативной памяти содерл ит схемы формирования сигналов разрешения конфликтов при обращении .к каждому блоку памяти и схемы формирования сигналов опроса, причем выходы регистров храпения старшей ча3заны с четвертой группой схем совпадения Приема кодов динамического приоритета от источников запроса, выходы которых связаны € регистрами хранения динамического приоритета, выходы регистров хранения динамическо-5 го приоритета соединены со вторыми дешифраторами, выходы которых связаны с первыми входами схем формирования сигналов разрешения конфликтов и формирования сигналов опроса, причем одноименные выходы .каж-10 дого второго дешифратора соединены -со схемами, Образуюшими строку матрицы, второй вход крайней левой сверху схемы формирования связан с выходом третьей схевы «ИЛР1, первые входы всех схем формирования столб-15 ца матрицы объединены шиной сигнала разрешения конфликта, второй выход схемы формирования каждой строки связан со вторым входом каждой следующей справа схемы формирования, .кроме крайних правых схем,20 схемы совпадения каждой строки подключены к соответствующим одноименным щинам второго дешифратора, а выходы этих схем совпадения подключены ко вторым входам крайних левых схем формирования нижележащей25 строки, выходы первых дещифраторов через четвертую схему «ИЛИ и дифференцирующую цепочку связаны с первым входом третьей схемы «ИЛИ, второй вход которой подключен к щине сигнала конца цикла one-30 ративной памяти. Это позволяет разрещать конфликты при выдаче сигналов готовности различным блокам памяти в один и тот же источник запросов и увеличить гибкость в разрещеиии кон-35 фликтов при обращении к блокам оперативной памяти в цифровой вычислительной системе путем использования динамического приоритета. .На фиг. 1 представлена блок-схема приори-40 тетного устройства системы; на фиг. 2 - приоритетная схема блока оперативной памяти, являющаяся составной частью приоритетного устройства. Приоритетное устройство системы содержит45 приоритетные схемы А блоков оперативной памяти, выходы 1 которых связаны с триггерами 2 хранения сигналов готовности блоков оперативной памяти. Схемы 5 -5 совпадения служат для формирования сигналов разреше-50 ния выдачи старщих разрядов адреса, являющихся адресом данного блока памяти и поступающих на требуемый вычислитель для опознавания блока памяти, готового к обслуживанию вычислителя.55 Схемы 7-10 совпадения служат для формирования сигналов опроса триггеров 2. Каждый ВХ.ОД / связан со схемой 11 «ИЛИ, выход которой, задержанный схемой 12 задержки, запускает ждущий мультивибратор60 13. Схема 10 связана со входом 14 запрета генерации мультивибратора 13. Выходы схем 3-6 связаны со входами схем совпадения 15- 18, .которыеУправляют выдачей информации с регистров 19-22 старшей части адреса ин-65 4 формации, запрашиваемой вычислителем, в шину 23 готовности блока памяти, В состав приоритетной схемы Л блока оперативной памяти .входят регистры 19, 24 и 25 старшей части адреса, дешифраторы 26--28, регистр 29 маски, схемы совпадения 30-35, регистры 36-38 динамического приоритета, дешифраторы 39-41, схемы 42-53 формирования сигналов разрешения конфликтов и сигналов опроса, схемы 54-57 совладения цепи ускорения передачи сигналов опроса, триггеры 58-60, управляющие ветилями 61-63, регистр 64 младшей части адреса и вентили 65-67 управления приемом младшей части адреса из адресных магистралей, схему 68 «ИЛИ, дифференцирующую цепь 69 с задержкой « схему 70 «ИЛИ, а также вентили 71-73. Рассмотрим работу устройства, Обращение к блоку оперативной памяти со стороны вычислителя (не показанного на рисунках) начинается посылкой / -старших разрядов адреса по шинам, общим для всех блоков памяти, где / log9P, причем Р - количество блоков памяти в вычислительной системе. Шины 74 связаны с первым вычислителем, шины 75 - со вторым, шины 76-с й-м вычисл.ителем. В рассматриваемой системе с общим полем памяти используется так называемый «режим расслоения .памяти, при .котором информация с последовательными адресами записывается в разные блоки памяти. При этом предполагается, что вычислитель не иссылает запросы в блоки пал-тяти, уже занятые его обслуживанием. Запросы к некоторому блоку памяти могут одновременно поступать от разных вычислителей по щинам 74-76. R старщих разрядов адреса поступают на регистры 19, 24 и 25 через вентили 71-73. С помощью дешифраторов 26-28 устанавливается соответствие поступивщего адреса физическому номеру блока памяти, т. е. вьгбор блока памяти. Срабатывание дешифраторов 26-28 вызывает запирание вентилей 71-73 соответственно, что обеспечивает запоминание старших разрядов .на время разрещения конфликта. Через время, достаточное для срабатывания вентиля 71, регистра 19 и дещифратора 26 (вентиля 72, регистра 24 и дешифратора 27 по шинам 77-79 на схемы 31 - 33 совпадения от вычислителей, пославших запрос по щинам 74-76, посылаются коды динамического приоритета. Динамический приоритет определяет порядок доступа источников запроса к блокам памяти. Предпочтение отдается вычислителям с более высоким динамическим приор.итетом, а при совпадении приоритетов первым получает доступ вычислитель с меньшим порядковым номером. Регистр 29 маски в зависимости от его содержимого (1 пли О в разряде, соответствующем некоторому вычислителю) разрещает или запрещает передачу информации с щин 77-79 на схемы совпадения 33-35. Регистр маски позволяет производить разбиение общего поля памяти между вычислителями, если в этом есть необходимость. Схемы совпадения 33-55 управляются дешифраторами 26-28, что позволяет производить выборку динамического приоритета с общей шины в данный блок оперативной памяти, .гегистры 36-38 служат для запоминания кодов динамического приоритета, поступивших от нескольких вычислителей на время разрешения конфликта. Дешифраторы 39-4 преобразуют коды в позиционные представления. Разрешение конфликтов обеснечивается схемами 42-53 формирования сигналов разрешения конфликтов и сигналов опроса. Схемы 42-53 идентичны, за исключением схем 44, 47, 50 и 53, и состоят из схем 80 и 81 совпадения и инвертора 82. Схемы 44, 47, 50 и 53 содержат только схему 80 совпадения. При срабатывании одного из дешифраторов 26-28 на выходе схемы 70 «ИЛИ воз(ннкает начальный нмпульс опроса, формируемый на шине 83. Схема 69 дифференцирования и задержки нозволяет сформировать импульс опроса на шине 83 после установления потенциалов на позиционных выходах дешифраторов 39-41. Имнульс опроса также может вырабатываться по сигналу конца цикла МОЗУ, поступаюш,его по шине 84. Сигналом ло шине 84 также производится сброс триггеров 58-60. Импульс опроса поступает .на схемы 80 и 81 совпадения. Высокий потенциал на шине, связанной со схемой вО схемы 51, индицирует наличие запроса высшего приоритета «С СО стороны вычислителя № 1. Наличие высокого потенциала на шине, связанной со схемой 52, индицирует наличие запроса высшего нриоритета от вычислителя № 2. Наличие высокого потенциала на шиле, связанной со схемой 48, индицирует наличие запросов с приоритетом «С-1 от вычислителя № 1 и т. д. В общем случае производится в соответствии с описанным прннцином разрешения конфликтов онрос схем 42-53 таким образом, что вначале опрашиваются схемы, соответствующие максимальному динамическому приоритету «С .в порядке роста номеров вычислителей, затем приоритету «С-1 аналогичным образом и т. д. (т. е. производится ска.иирование слева направо и сверху вниз). Ири достижении сигналом опроса одной их схем 42-53 он поступает на схемы 80 н 81. Наличие высокого нотенциала на шине соответствующего дешифратора приводит к прохождению сигнала опроса через схему 80 на шины 85 и 86 разрешения конфликта. Сигналом по данным шинам осуществляется установ;ка триггеров 55-60 унравления выдачей информации из блока памяти в шину, соответствующую обслуживаемому вычислителю. Эти же сигналы производят сброс соответствующих регистров 56-55 динамического нриоритета. В рассматриваемой системе возможно возникиовение таких конфликтов, .когда несколько приоритетных схем различных блоков памяти вырабатывают одновременно сигнал готовности для одного и того же вычислителя. Это происходит из-за асинхронности разрешения конфликтов в приоритетных схемах отдельных блоков памяти. Так как вычислитель связан одной шиной готовности со всеми приоритетными схемами блоков памяти, то необходимо организовать разнесение во време.ни сигналов готовности, поступаюших в данный вычислитель таким образом, чтобы ойи могли быть им обработаны. Эту функцию выполняют К схем, идентичных схеме, изображенной на фиг. 1 (где К. - количество вычислителей в системе). Сигналы разрешения конфликтов, вырабатываемые приоритетным-и схемами блоков памяти н нредназначениые для некоторого вычислителя, поступают на регистры, одной из схем (см. рис. 1) и одновременно через схему 11 «ИЛИ и схему 12 задержки запускают ждущ-ий мультивибратор 13. Время задержки выбирается большим времени прохождения сигнала опроса, вырабатываемого мультивибратором, через вентили схемы 7-10. Сигнал опроса проходит через схемы 3-6 или 7-10 в зависимости от состояния триггеров 2. Прохождение сигнала опроса через одну «з схем 3-6 обеспечивает выработку сигнала, открываюш,его соответствуюш,ую схему 15- 18, что обеспечивает выдачу сигнала готовности по шине 23 в виде R старших разрядов адреса, хранимых до данного момента времени в регистрах 19-22. Ждущий мультивибратор вырабатывает сигнал опроса до тех пор, нока выходными сигналами со схем 4-7 не будут установлены в «О все триггеры 2. Следующий импульс опроса блокирует ждущий мультивибратор 13. Сигналы с выходов схем 3-6 поступают на схему 87 «ИЛИ и после прохождения через схему 88 задержки поступают на щину 89, обеспечивающую сброс регистра 19. Время задержки схемы выбирается равным временн максимальной задержки между моментом поступления сигнала готовности по шине 24 в некоторый вычислитель и моментом выдачи этим вычислителем младшей части адреса, поступающей на регистр 64 через один из вентилей 65-67, управляемых регистрами 19, 24 и 25. iB схемах, используемых в системе, но не представленных отдельными чертежами вследствие их идентичности схемам (см. фиг. 1), происходит выработка сигналов по шинам 90 и 91 сброса регистров 24 и 25, причем выра-ботка указанных сигналов производится аналогично выработке уже описанного сигнала по щине 89. Предмет изобретения 1. Приоритетное устройство для цифровой вычислительной системы, содержащее регистры, триггеры, логические схемы совпадения, схемы «ИЛИ, дешифраторы и схемы задержки, отличающееся тем, что, с целью разрешеиия конфликтов при выдаче сигналов готовности различным блокам памяти в один л гот же источник запроса, оно содержит Р приоритетных схем блоков оперативной памяти (где Р - количество блоков памяти) и /С 5 логических схем, содержащих триггеры хранения сигналов готовности блоков оперативной памяти и ждущий мультив ибратор формирования сигналов опроса триггеров хранения (где /V - количество вычислителей в системе), 10 причем первый .выход каждого триггера хранения -сигналов готовности подключен .к первому входу первой группы схем совпадения, второи выход соединен с первым входом второй группы схем совпадения, второй вход. 15 крайних левых первой и второй групп схем совпадения подключен к ждущему мультивибратору формирования сигналов опроса триггеров хранения, второй вход каждой первой и второй групп схем совпадения (f-й при отсчете слева) подключен к выходу (i-1)-й второй группы схем совпадения, выходы первой группы схем совна.дения подключе)Ы к первым входам третьей группы схем совпадения, вторые входы которых связаны с регист- 25 рами хранения старшей части адреса оперативной памяти, выходы третьей группы схем совпадения присоединены к шине сигнала готовности олока оперативной намяти, выход крайней правой схемы совпадения из второй ЗО группы схем совпадения подключен ко входу запрета генерации ждущего мультивибратора, вход запуска которого соедннен с выхо.дом, схемы задержки, вход схемы задерж.ки связан с первой схемой «ИЛИ, входы которой соеди- 35 нены с шинами сигналов разрещеиия конфликтов, выход каждой схемы совпадения из первой группы .схем совпадения связан со .входом установки в ноль соответствующего триггера хра.нения. 2. Устройство по п. 1, отличающееся тем, что, с целью повышения гибкости системы в 20 40 разрешепий конфликтов при обращении к блокам оперативной памяти в цифровой вычислительной системе с диламичесюим приоритетом, в .нем каждая приоритетная схема блока оперативной памяти содержат схемы формирования- сигналов разрешения конфликтов при обран,ении к каждому блоку памяти и схемы формирования сигналов опроса, причем выходы регистров хранения старщей части адреса через первые дешифраторы связаны с четвертой грунпой схем совпадения приема кодов динамического приоритета от источников запроса, выходы которых связаны с регистрами хранения динамического приоритета, выходы регистров хранения динамического. приоритета соединены со вторыми дешифраторами, выходы которых связаны с первыми входами схем формирования сигналов разрешения ко.нфликтов и формирования сигналов опроса, причем одноименные выходы каждого второго дешифратора соединены со схемами,, образуюнигми строку матрицы, второй вход крайней левой сверху схемы формирования связан с выходом третьей схемы «ИЛИ, первые входы всех схем формирования столбца матрицы объединены, шиной сигнала разрешения конфликта, второй выход схемы формирования .каждой строки связан iCO вторым входом каждой следующей справа схемы формирования, кроме крайних правых схем, схемы совпадения каждой строки нодключены к соответствующим одноименным шинам второго дешифратора, а выходы этих схем совнадения подключены ко вторым входам крайних левых схем формирования нижележащей строки, выходы первых дешифраторов через четвертую схему «ИЛИ и дифференцирующую цепочку связаны с первым входом третьей схемы «ИЛИ, второй вход которой подключей к шине сигнала конца цикла оперативной памяти. 5(5 itSI 51 tg Г.Ы J,.,, ,-I 43} 6u 1-I „

| название | год | авторы | номер документа |

|---|---|---|---|

| БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОИСГСО | 1970 |

|

SU287123A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1965 |

|

SU224159A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1989 |

|

SU1777145A2 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство для программного управления технологическим оборудованием | 1989 |

|

SU1714575A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1176340A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Устройство для сопряжения управляющей и управляемых вычислительных машин | 1988 |

|

SU1517033A1 |

Авторы

Даты

1970-01-01—Публикация