1

Изобретение относится к вычислительной технике, техиике связи и телеуправления, где ставятся задача помехоустойчивой передачи информации.

Иавестно декодирующее устройство, содержащее приемник двоичных сигналов, соединенный со схемой регистрацией, и схему обнаружения ошибок, ,в котором для повыщения достоверности работы для обнаружения ошибок используют избыточность групповых кодов. Однако повыщение достоверности принимаемой информации, особенно в системах с обратной связью, достигается ценой снижения Пропускной способности систем за счет повторных передач кодовых комбинаций, в которых обнаружены ошибки.

В ряде случаев для передачи большого объема информации по каналу со сравнительно ВЫСОКИМ относительным уровнем помех пропускная способность системы с обратной связью может оказаться недостаточной. Если требования по достоверности приема этой информации являются более низкими, чем может обеспечить система связи, то, с целью повышения пропускной способности системы связи, ломимо обнаруження большой части ошибок, целесообразно осуществлять исправление некоторых наиболее вероятных ошибок. Это приведет к уменьшению числа переспросов и ценой некоторого снижения достоверности привимаемой информации будет достигнуто увеличение пропускной способности системы связи. Путем изменения доли исправляемых ошибок ИЗ общего числа возможных ошибок в известной степени можно регулировать пропускную способность системы и достоверность п рини маемой и н фОр м аци и.

Цель изобретения - повышение достоверности работы устройства путем повышения про-пускной способности систем с обратной связью при использовании кодов с четным числом «единиц.

Цель достигается тем, что в предлагаемое устройство введены схема приема с нулевой

зоной, два регистра задержки, два счетчика четНОстн, две схемы «И и сумматор ПО модулю два, дричем выход приемника двоичных сигналов соединен со входом схемы приема с нулевой зоной, выход которой соединен со

входом .первого регистра задержки и со входом первого счетчика четности, выход схемы регистрации соединен со входом .второго регистра задержки и со входом второго счетчика четности, выходы обоих счетчиков четности соединены со входами нервой схемы «И, выХОД которой соеди.нен с первым входом второй схемы «И, второй вход которой соединен с выходом первого регистра задержки, выходы второго регистра задержки и второй схемы

«И соединены со входами сумматора по модулю два, 1ВЫХОД которого соединен со ,входом схемы обнаружения ошибок. Это позволяет исправлять некоторую часть ошибок, так как наряду с обычной регистрацией двоичных знаков фиксируются знаки, значение которых сомнительно (прием с двойной нулевой зоной)..

Если в принятой кодовой комбинации выполняется проверка на четность, то независимо от числа двоичных знаков, принятых в нулевой зоне, кодовая комбинация поступает на схему обнаружения ошибок без изменения. Если ,в принятой кодовой комбинации проверка на четность не выполняется и одновременно зафиксирован только один неуверенно принятый двоичный знак, то он инвертируется на противоположное значение. Если в принятой кодовой комбинации лроверка на четность не выполняется и одновременно зафиксировано нечетное число неуверенно нринятых двоичных гнакОВ, то эти знаки инвертируются на противоположное значение. Во .всех других случаях инвертирование двоичных знаков не происходит.

Таким образом происходит исправление или части одиночных или части нечетных наиболее вероятных ошибок.

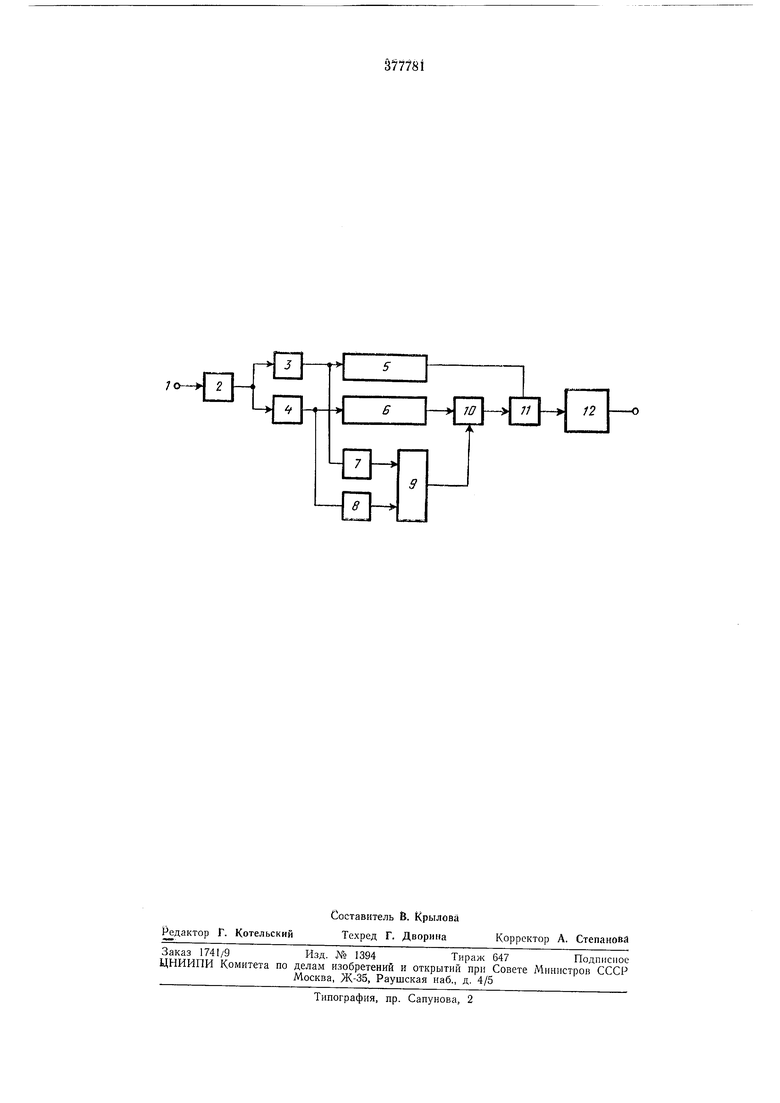

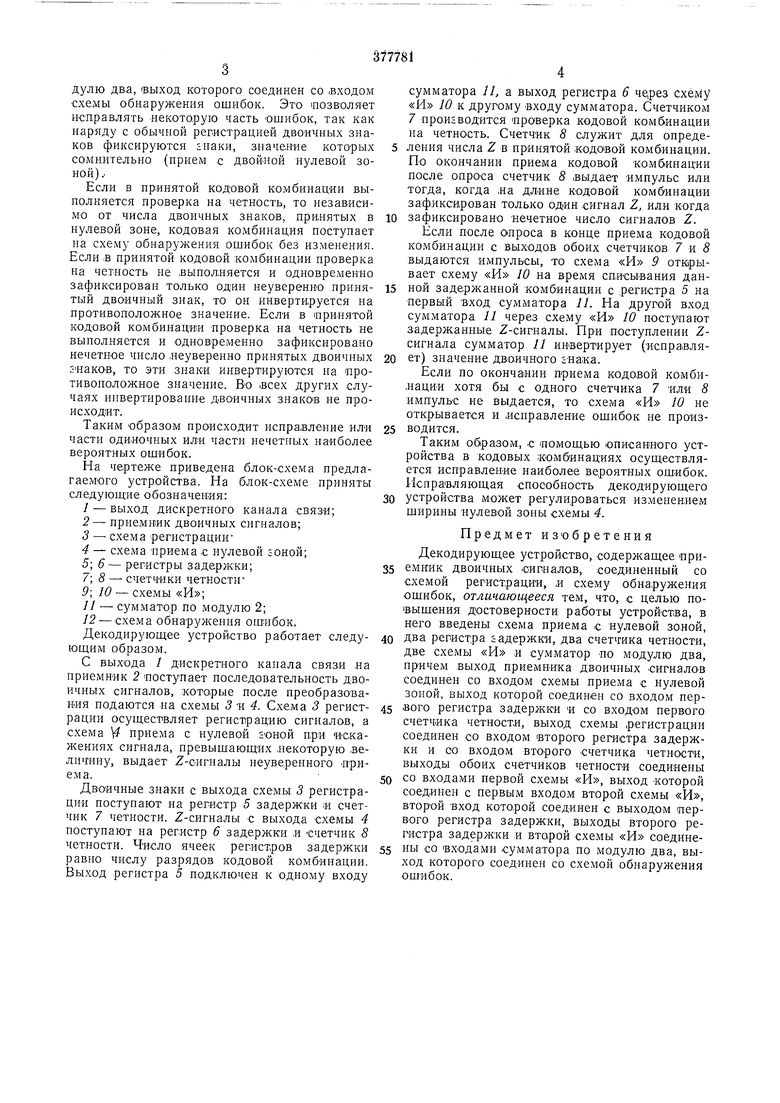

На чертеже приведена блок-схема предлагаемого устройства. На блок-схеме приняты следующие обозначения:

1 - выход дискретного канала связи;

2- приемник двоичиых сигналов;

3- схема регистрации

4- схема ирнема с нулевой зоной; 5; 6- регистры задержки;

7; 8 - счетчики четности9 10 - схемы

И - сумматор по модулю 2;

12 - схема обнаружения ошибок.

Декодирующее устройство работает следующим образом.

С выхода / дискретного канала связи на приемник 2 поступает последовательность двоичных сигналов, которые после преобразования подаются на схемы 3 и 4. Схема 3 регистрации осуществляет регистрацию сигналов, а схема 4 приема с нулевой Зоной при искажениях сигнала, превышающих некоторую величину, выдает Z-сигналы неуверенного приема.

Двоичные знаки с выхода схемы 3 регистрации поступают на регистр 5 задержки и счетчик 7 четности. Z-сигналы с выхода схемы 4 поступают на регистр 6 задержки ,и счетчик 5 четности. Число ячеек регистров задержки равно числу разрядов кодовой комбинации. Выход регистра 5 подключен к одному входу

сумматора 11, а выход регистра 6 че,рез схему «И 10 к другому входу сумматора. Счетчиком 7 производится проверка кодовой комбинации на четность. Счетчик 8 служит для определения числа Z в принятой кодовой комбинации. По окончании приема кодовой комбинации после опроса счетчик 8 выдает импульс или тогда, когда ,на длине кодовой комбинации заф.икси,рован только один сигнал Z, или когда

зафиксировано нечетное число сигналов Z.

Если после опроса в конце приема кодовой комбинации с выходов обоих счетчиков 7 и S выдаются импульсы, то схема «И 9 отк|рывает схему «И W на время списывания данной задержанной комбинации с регистра 5 на первый вход сумматора 11. На другой вход сумматора 11 через схему «И 10 поступают задержанные Z-сигналы. При поступлении Zсигнала сумматор 11 инвертирует (исправляет) значение двоичного знака.

Если по окончании приема кодовой комбинации хотя бы с одного счетчика 7 или 8 импульс не выдается, то схема «И W не открывается и исправление ошибок не производится.

Таким образом, с помощью описанного устройства в кодовых комбинациях осуществляется исправление наиболее вероятных ошибок. Исправляющая способность декодирующего

устройства может регулироваться изменением ширины нулевой зоны схемы 4.

Предмет изобретения

Декодирующее устройство, содержащее приемник двоичных сигналов, соединенный со схемой регистрации, и схему обнаружения ощибок, отличающееся тем, что, с целью повышения достоверности работы устройства, в него введены схема приема с нулевой зоной,

два регистра задержки, два счетчика четности, две схемы «И .и сумматор но модулю два, причем выход приемника двоичных сигналов соединен со входом схемы приема с нулевой зоной, выход которой соединен со входом первого регистра задержки и со входом первого счетчика четности, выход схемы регистрации соединен со входом второго регистра задержки и со входом второго счетчика четности, выходы обоих счетчиков четности соединены

со входами первой схемы «И, выход которой соединен с первым входом второй схемы «И, второй вход которой соединен с выходом первого регистра задержки, выходы второго регистра задержки и второй схемы «И соединены со входами сумматора по модулю два, выход которого соединен со схемой обнаружения ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема избыточной информации | 1981 |

|

SU1001147A1 |

| Устройство для приема одиночных команд | 1986 |

|

SU1350840A1 |

| УСТРОЙСТВО АДАПТИВНОЙ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2259638C1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНЫХ СООБЩЕНИЙ ПО КАНАЛАМ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2007 |

|

RU2391787C2 |

| УСТРОЙСТВО для ОЦЕНКИ ДОСТОВЕРНОСТИ БИНАРНЫХ СИГНАЛОВ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 1972 |

|

SU351332A1 |

| УСТРОЙСТВО для СОПРЯЖЕНИЯ | 1971 |

|

SU321839A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Устройство для исправления ошибок | 1988 |

|

SU1619408A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Устройство для приема избыточной информации | 1983 |

|

SU1107146A1 |

Авторы

Даты

1973-01-01—Публикация