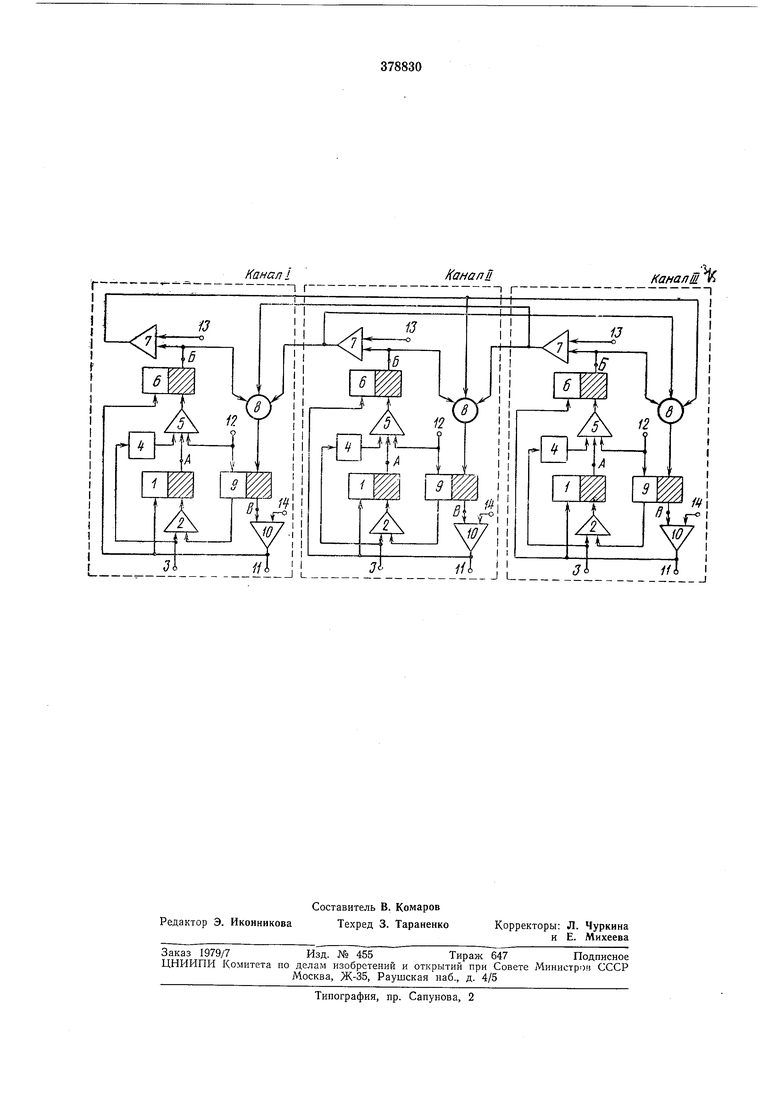

Изобретение относится к вычислительной технике и может быть использовано в резервированных дискретных устройствах. Известное устройство для синхронизации сигналов содержит триггер залиси, единичным входом соединенный с выходом входной схемы «И, первый вход которой соединен со входом устройства. Через инвертор триггер подключен к первому входу трехвходовой схемы «И, второй вход которой соединен с единичным выходом триггера записи, а выход- с единичным входом триггера хранения, одноименный выход, которого связан со входом двухвходовой схемы «И. При использовании в резервированных днекретных устройствах с несинхронным поступлением входных сигналов в различные каналы устройство обладает недостаточной надежностью. Целью изобретения является повышение надежности устройства. Для этого в каждый канал введены мажоритарный элемент триггер выдачи и выходная схема «И. Один вход мажоритарного элемента соединен с выходом триггера храчения своего канала, а другие - с выходами авухвходовых схем «И других каналоВ. Единичный вход триггера, выдачи соединен с выходом мажоритарного элемента, нулевой вход - с источником тактовых импуль,сов, а нулевой выход со вторым входом входной схемы «И. Выходная схема «И первым входом соединена с единичным выходом триггера выдачи, вторым - с источником тактовых импульсов, а выходом - с нулевыми входами триггеров записи и хранения. На чертеже представлена блок-схема предлагаемого устройства. В каждом канале устройства имеется триггер записи 1, единичный вход которого соединен с выходом схемы «И 2. К одному из входов этой схемы присоединен вход 3, подключенный через инвертор 4 к одному из входов трехвходовой схемы «И 5, второй вход которой соединен с единичным выходом триггера заниси /. Выход схемы «И 5 подключен к единичному входу триггера хранения 6, единичный выход которого подсоединен ко входу схемы «И 7 и к одному из входов мажоритарного элемента 8, который может быть схемой «два. из трех для трехканального дискретного устройства. Выход схемы «И 7 каждого канал подключен к соответствующим входам элемента 8 остальных каналов. Единичный вход триггера выдачи 9 соединен с выходом элемента 8, а единичный выход - с одним из входов схемы «И 10, выход которой соединен с нулевыми входами триггера / и б и выходом // устройств.а. Нулевой выход триггера 9 соединен со вторым входом схемы «И 2. Третий вход схемы «И 5 и нулевой вход триггера 9 подсоединены ко входу 12 тактового импульса, вторые входы схем «И 7 и «И 10 подключены соответственно ко входам 13 и 14 тактовых импуль- 5 сов. Устройство работает следующим образом. Исходное состояние триггеров 1, 6, 9 - нулевое. В каждом канале сигнал, поступающий на вход 3, проходя через схему «И 2, на Ю втором входе которой присутствует разрешающий потенциал с нулевого выхода триггера выдачи 9, устанавливает триггер записи / а состояние I. Потенциальный сигнал с единичного выхода триггера 1 поступает на один 15 из входов трехвходовой схемы «И 5, ко второму входу которой через инв-ертор 4 подключен вход 3, запрещающий срабатьгваиие схемы «И 5 при наличии входного сигнала. По окончании входного сигнала тактом переза- 20 писи, поступающим на вход 12, информация с триггера 1 переписывается, в триггер хранения 6, потенциал с единичного плеча которого поступает па один из входов мажоритарного элемента 5 и на вход схемы «И 7. 25 При поступлении тактового имлульса на вход 13 импульс с выхода схемы «И 7 поступает на соответствующие входы мажоритарных элементов 8 остальных ка.налов. При совпадении сигналов на двух из трех входах 30 элемента 8 на его выходе формируется сигнал, устанавливающий триггеры 9 во всех каналах в состояние I. Потенциал с единичного выхода триггера 9 поступает на один из входов схемы «И 10. Тактовый импульс, по- 35 ступающий на вход 14 схемы «И 10 выдеЛ1яет на выходе 11 синхронно во всех трех каналах импульсы, являющиеся выходными сигналами, которые в каждом канале производят сброс триггеров 1 v( 6. 40 Быстродействие схемы синхронизации определяется: частотными возможностями элементной базы, максимальной длительностью входных сигналов и периодом следования тактовой частоты. Для исключения последействия отказов в различных каналах и обеспечения их автономности, что повышает надежность устройства, мажоритарные элементы 8 по входам, соединенным с выходами схем «И 7 соседних каналов, могут содержать элементы гальванической развязки. Предмет изобретения Устройство для синхронизации сигналов, содержащее в каждом канале триггер записи, единичный вход которого соединен с выходом входной схемы «И, первый вход которой подключен через инвертор к первому входу трехвходовой схемы «И, второй вход которой соединен с единичным выходом триггера записи, а выход - с единичным входом триггера хранения, одноименный выход которого связан со входом двухвходовой схемы «И, отличающееся тем, что, с целью повышения надежности работы устройства, в нем в каждый канал введен мажоритарный элемент, один вход которого соединен с единичным выходом триггера хранения данного канала, а другие - с выходами двухвходовых схем «И других каналов, триггер выдачи, единичный вход которого соединен с выходом мажоритарного элемента, нулевой вход-с источником тактовых импульсов, а нулевой выход - со вторым входом в.ходной схемы «И, выходная схема «И, первый вход «оторой соединен с единичным выходом триггера выдачи, второй вход - с источником тактовых импульсов, а выход - с нулевыми входами триггеров записи и хранения.

Канал I

i

КанапЁ

Каналш

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации входных сигналов многоканальной дискретной системы | 1975 |

|

SU565294A1 |

| Трехканальное резервированноеуСТРОйСТВО для СиНХРОНизАции СигНАлОВ | 1979 |

|

SU822187A1 |

| Устройство для синхронизации сигналов | 1978 |

|

SU860042A1 |

| ВСЕСОЮЗНАЯ ПА:ГЕ11иЛ-Гсл,:^Л5НАЯ 6иблиотеиа_№_А____РЕЗЕРВ^ | 1970 |

|

SU282422A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ МИКРОПРОЦЕССОРНАЯ СИСТЕМА | 1987 |

|

SU1494761A1 |

| ТРЕХКАНАЛЬНЫЙ РЕЗЕРВИРОВАННЫЙ ГЕНЕРАТОР | 1988 |

|

SU1568771A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Трехканальный резервированныйРАСпРЕдЕлиТЕль иМпульСОВ | 1978 |

|

SU798848A1 |

| Резервированное устройство для синхронизации сигналов | 1974 |

|

SU520593A1 |

| Счетное устройство | 1986 |

|

SU1368981A1 |

.Л Т-ГТ I 1 1

Даты

1973-01-01—Публикация