1

Изобретение относится к цифровым устройствам для обработки данных и предназначено для корреляционного преобразования сигналов различного характера, в том числе и вибросейсмических.

Известен цифровой коррелятор последовательного действия, в котором в каждый момент времени вычисляет ся значение лишь одной ординаты корреляционной функции. Вычисленные значения ординат корреляционной функции последовательно.появляются на выходе коррелятора 1 .

Основным недостатком последовательного коррелятора является низкое быстродействие.

Наиболее близким к предлагаемому по своей технической сущности является последовательный коррелятор, содержащий блок аналого-цифрового преобразователя блока памяти опорного и сейсмического сигналов,блок умножения, интегратор, преобразователь цифровых отсчетов и дешифратор. Два последних блока используются для уменьшения разрядности отсчетов сейсмического сигнала.

После заполнения обоих запоминающих устройств (ем кость которых

определяется числом отсчетов N опорного сигнала) значения с их выходов поступают на блок умножения, затем частичные произведения поступают на интегратор, с выхода которого результат - одна ордината вычисленной корреляционной функции отсылается на регистрацию. Цикл вычисления одной точки при этом

10 равен интервалу квантования сейсмического сигнала 2 .

При большой длительности исследуе1 «лх сигналов (как это имеет место, например, в вибрационной

t5 сейсморазведке) основным препятствием на пути построения цифровых последовательных корреляторов является относительно низкое быстродействие блоков суммирования и умножения. Низкое быстродействие традиционных арифметических блоков объясняется тем, что результаты всех операций, в том числе и промежуточных, представляются в двоичном

25 позиционном коде. При этом у быстродействующего матричного перемножителя время, затрачиваемое на получение одного частного произведения, складывается из времени, необходи30 МОго на получение матрицы одноразрядных логических произведений, и времени, необходимого на преобразование этой матрицы в двоичный позиционный код (время распространения переносов).

У сумматора время, затрачиваемое на получение суммы двух слагаемых складывается из времени TQC , необходимого на получение одноразрядных значений суммы данного разряда и переноса е в следующий разряд, и времени Тр,- , необходимого на преобразование п одноразрядных значений суммы и переноса в двоичный позиционный код.

Для вычисления одной ординаты корреляционной функции по традиционной схеме необходимо затратить время .

T..-N.(..

).

ц(тпр.с.

Цель изобретения - увеличение быстродействия коррелятора.

Поставленная цель достигается .тем, что в цифровой коррелятор,содежащий аналого-цифровой преобразователь, первый и второй входы которог являются входами коррелятора, а первый и второй выходы подключены соответственно ко входам блоков памяти опорного и исследуемого сигналов, выхода которых соединены со входами соответствующих буферных блоков памяти, введены блок элементов И, блок счетчиков полох ительных значений, блок счетчиков отрицательных значений и блок .накопления, первый и второй выходы буферных блоков памяти подключены соответственно ко входам блока элементов И, первый и второй выходы которого подключены соответственно ко входам блоков счетчиков положительных и отрицательных значений, выходы которых соединены соответветственно с первы ,и вторым входами блока накопления.

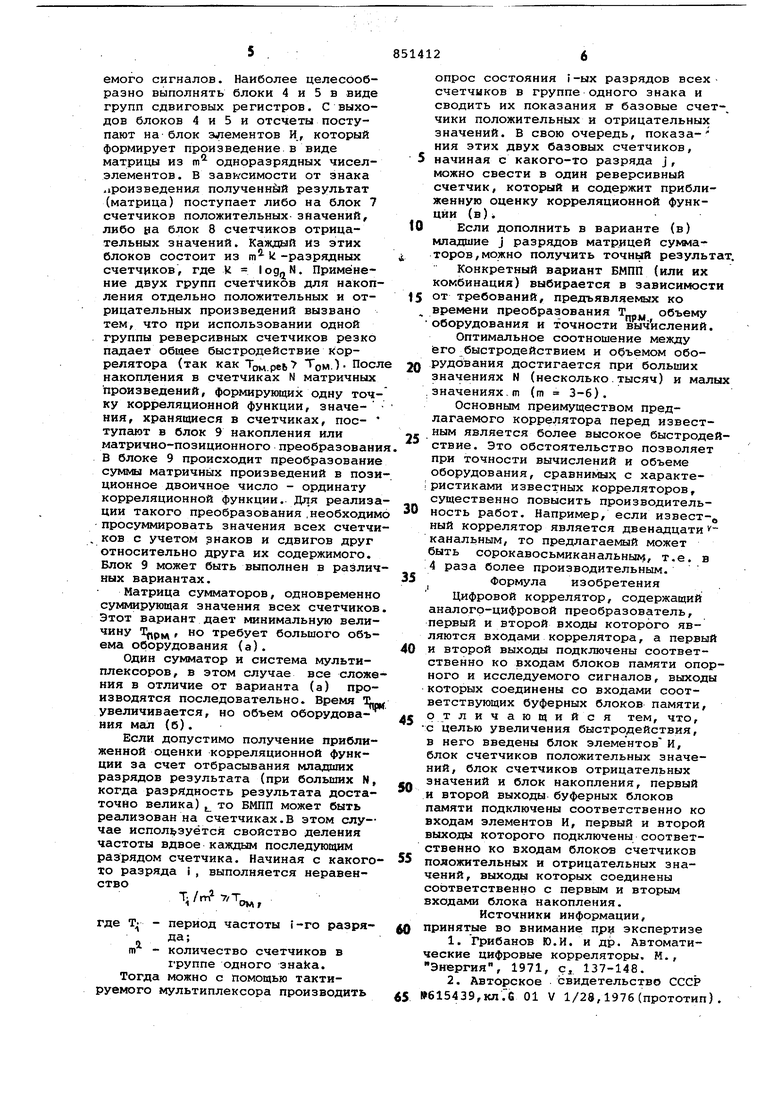

На чертеже представлена блок-схема предлагаемого коррелятора.

: Устройство содержит аналого-цифроврй преобразователь 1, блок 2 памяти опорного сигнала, блок 3 памяти исследуемого сигнала,блок 4 памяти опорного сигнала, буферный блок 5памяти исследуемого сигнала, блок б элементов И, блок 7 счетчиков положительных значений, блок 8 счетчиков отрицательных значений, блок 9 н&копления матрично-позиционйого преобразователя (для упрощения блок управления и его связи не показаны).

В качестве внутренних форматов коррелятора используются совокупности одноразрядных чисел, над которыми производится все внутренние операции. Произведение при этом эгщается как матрица с числом одноразрядных элементов равным m , где

m - разрядность сомножителей. Накопление частных произведений в матричном виде производится с помощью матриц двоичных счетчиков, причем каждый счетчик служит для накопления лишь одного элемента матрицы. 5 На один из входов матрицы элементов И подаются значения множимого, на второй - множителя, на третий - тактовый импульс. Выходы матрицы элементов И подключены ко входам счетчиков.

В этом случае при подаче одного тактового импульса (за время Тр„ равное периоду максимальной тйктовой частоты счетчиков) выполняется сразу парная операция умножение-сложение, результат

5 которой представлен в матричном виде. Каждая ордината корреляционной функции (в матричном виде) вычисляется за время , р&вное N Т..

Преобразование матричного резульQ тата в позиционный код необходимо произвести лишь один раз в конце цикла вычислений для данной точки. Тогда полное время вычисляется по формуле

4фМ ом прМ

Учитывая то, что

.у

.)

а также то, что

N -Т

приходим к выводу, что

к..т

При .больших значениях N (как, например, это имеет место в вибрационной сейсморазведке,, где N 400016000)

прм --Г(,„

и тогда можно считать, что

.

VM.

При такой организации вычислительного процесса внутреннее быстродействие коррелятора ограничивается, в основном, лишь предельными тактовыми частотами счетчиков и,

следовательно, значительно выше быстродействия известных корреляторов.

Устройство работает следующим образом.

Опорный и исследуемый сигналы поступают со входного блока аналогового преобразователя 1 соответственно в блок 2 памяти опорного сигнала и в блок 3 памяти исследуемого сигнала. Емкость обоих запоминающих устройств определяется количеством

отсчетов N опорного сигнала и разрядностью m входных данных. Для согласования по быстродействию между блоками 2 и 3 и блоком 6 матриц элементов И введены буферные блоки

памяти 4 и 5 для опорного и исследуемого сигналов. Наиболее целесообразно выполнять блоки 4 и 5 в виде групп сдвиговых регистров. С выходов блоков 4 и 5 и отсчеты поступают на блок элементов И, который формирует произведение в виде матрицы из т одноразрядных чиселэлементов . В зависимости от знака .1роизведения полученной результат (матрица) поступает либо на блок 7 счетчиков положительных значений, либо ва блок 8 счетчиков отрицательных значений. Каждый из этих блоков состоит из т kl -разрядных счетчиков, где К log,jN. Применение двух групп счетчиков для накоп ления отдельно положительных и отрицательных произведений вызвано тем, что при использовании одной группы реверсивных счетчиков резко падает общее быстродействие коррелятора (так как Т(реь TOM.)- Пос накопления в счетчиках N матричных произведений, формирующих одну точ ку корреляционной функции, значения, хранящиеся в счетчиках, поступают в блок 9 накопления или матрично-позиционного преобразован В блоке 9 происходит преобразовани суммы матричньгх произведений в поз ционное двоичное число - ординату корреляционной функции. Для реализ ции такого преобразования.необходим просуммировать значения всех счетч ков с учетом знаков и сдвигов друг относительно друга их содержимого. Блок 9 может быть выполнен в различ ных вариантах. Матрица сумматоров, одновременно суммирующая значения всех счетчиков Этот вариант дает минимальную величину Tflptft г но требует большого объема оборудования (а). Один сумматор и система мультиплексоров, в этом случае все сложе ния в отличие от варианта (а) производятся последовательно. Время 1 увеличивается, но объем оборудования мал (б). Если допустимо получение приближенной оценки корреляционной функции за счет отбрасывания младших разрядов результата (при больших N когда разрядность результата достаточно велика) то БМПП может быть реализован на счетчиках.В этом случае используется свойство деления частоты вдвое каждым последующим разрядом счетчика. Начиная с какого то разряда i, выполняется неравенствоТ./П.7.Т, где Т- - период частоты i-ro разряаm - количество счетчиков в группе одного 3Haka. Тогда июжно с помощью тактируемого мультиплексора производить опрос состояния i-ых разрядов всех счетчиков в группе одного знака и сводить их показания н базовые счет- чики положительных и отрицательных значений. В свою очередь, показания этих двух базовых счетчиков, начиная с какого-то разряда j, можно свести в один реверсивный счетчик, который и содержит приближенную оценку корреляционной функции (в) Если дополнить в варианте (в) младшие j разрядов матрицей сукматоров,можно получить точный результат. Конкретный вариант БМПП (или их комбинация) выбирается в зависимости от требований, предъявляемых ко времени преобразования Т объему оборудования и точности вычислений. Оптимальное соотношение между его быстродействием и объемом оборудования достигается при больших значениях N (несколько.тысяч) и малых значениях,m (m 3-6). Основным преимуществом предлагаемого коррелятора перед известным является более высокое быстродействие. Это обстоятельство позволяет при точности вычислений и объеме оборудования, сравнимых с характеристиками известных корреляторов, существенно повысить производительность работ. Например, если известный коррелятор является двенадцати канальным, то предлагаемый может быть сорокавосьмиканальным, т.е. в 4 раза более производительным. Формула изобретения Цифровой коррелятор, содержащий аналого-цифровой преобразователь, первый и второй входы которого являются входами коррелятора, а первый и второй выходы подключены соответственно ко входам блоков памяти опорного и исследуемого сигналов, выходы которых соединены со входами соответствующих буферных блоков памяти, отличающийся тем, что, с целью увеличения быстродействия, в него введены блок элементов И, блок счетчиков положительных значений, блок счетчиков отрицательных значений и блок накопления, первый и второй выходы буферных блоков памяти подключены соответственно ко входам элементов И, первый и второй выходы которого подключены соответственно ко входам блоков счетчиков положительных и отрицательных значений, выходы которых соединены соответственно с первым и вторым входами блока накопления. Источники информации, принятые во внимание пру экспертизе 1.Грибанов Ю.И. и др. Автоматические цифровые корреляторы, М., Энергия, 1971, с,, 137-148. 2.Авторское свидетельство СССР 615439,кл.С 01 V 1/28,1976 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1979 |

|

SU842768A1 |

| Цифровой коррелятор | 1980 |

|

SU903892A1 |

| Многоканальный коррелятор | 1974 |

|

SU552613A1 |

| Многоканальный цифровой коррелятор | 1974 |

|

SU478315A1 |

| Многоканальный цифровой коррелометр | 1982 |

|

SU1040492A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Коррелятор | 1976 |

|

SU696474A1 |

| Коррелометр | 1982 |

|

SU1026144A1 |

| КОРРЕЛЯТОР ДЛЯ ОПЕРАТИВНОГО АНАЛИЗА СЛУЧАЙНЫХ ПРОЦЕССОВ | 1970 |

|

SU264789A1 |

| ЦИФРОВОЙ КОРРЕЛЯТОР | 1992 |

|

RU2067316C1 |

Авторы

Даты

1981-07-30—Публикация

1979-10-23—Подача