Изобретение относится к области вычислительной техники.

Известны аналого-дискретные сумматоры, содержащие входной сумматор, источник эталонного сигнала, суммирующий блок, выполненный на аналоговом сумматоре, соединенном с пороговым элементом, цепи задержки и коммутирующие элементы.

Иредлол енное устройство отличается от известных тем, что оно содержит ряд суммирующих блоков, основные входы которых соединены с выходом входного сумматора, а информационные входь подключены к выхбду Источника эталонных сигналов, причем управляющий вход предыдущего суммирующего блока соединен через последовательно включенные цепь задержки и коммутируюпщй элемент с разрещаюн1,им входом последующего суммируюидего блока, а дискретный выход любого предыдущего суммирующего блока соединен с соответствующим входом этого же суммируюн1.его блока, с соответствующими входами всех предыдущих суммирующих блоков и соответствующими вычитающими входами входиого аналогового сумматора.

Кроме того, в каждый суммирующий блок введен аналоговый ключ, входы которого соедииены - один с управляющим выходом порогового элемента, а другой - с информационным входом суммирующего блока, а выход

аналогового ключа соединен с дискретным выходом суммирующего блока, разрещающий вход которого соединен с другим входом порогового элемента.

Это позволило увеличить суммарный уровень входного сигнала и расширить область применения устройства.

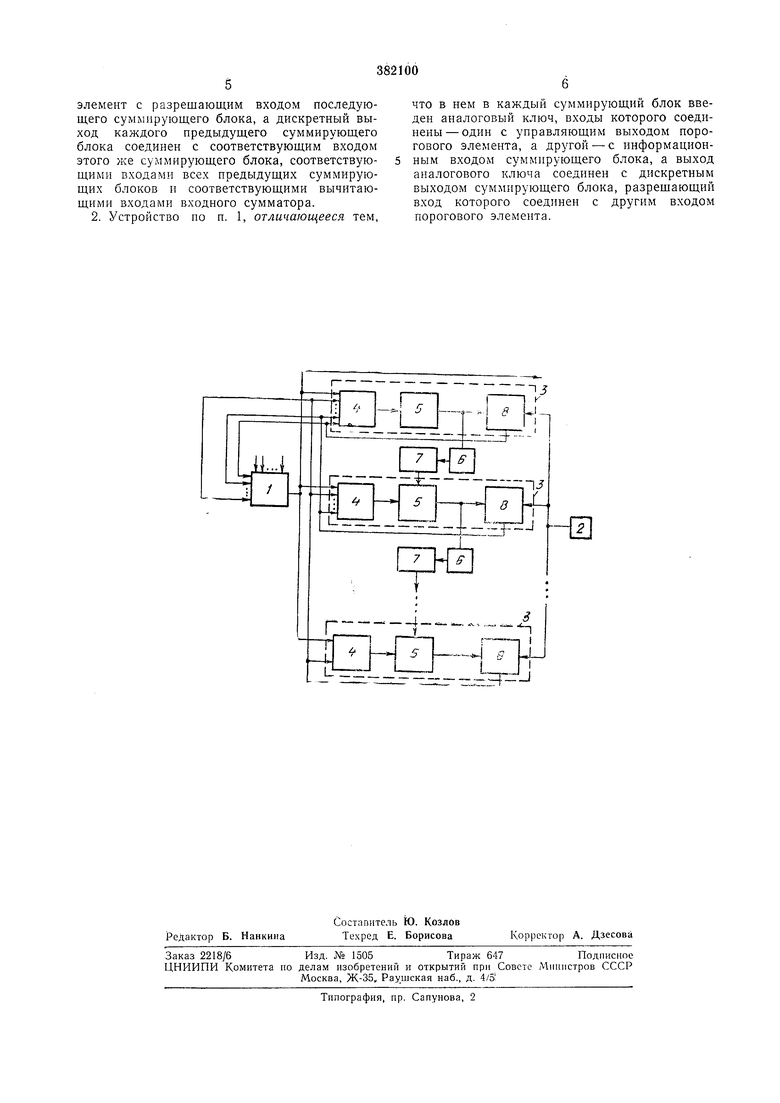

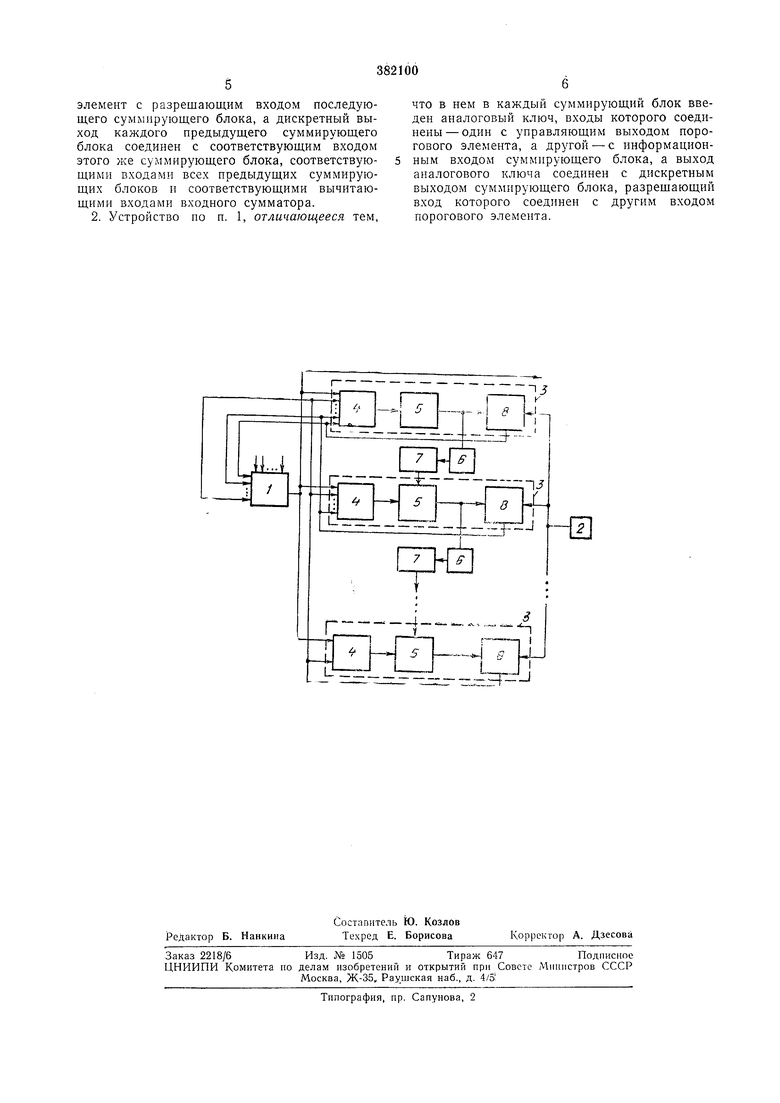

Блок-схема предлагаемого сумматора приведена на чертеже.

Устройство содержит входной сумматор /, источник 2 эталонного сигнала, суммирующий блок 3, выполнеппый па аналоговом сумматоре 4, соединенном с пороговым элементом 5. цепи задержки 6 и коммутирующие элементы 7, причем в каждый суммирующий блок 3 введен аналоговый ключ 8.

В устройстве входные, ВЫХОДИЕ Ш и промежуточные дискретные величины представляются уроппями (фиксироваппыми зпачеппями пекоторого параметра) аналогового сигнала так, что целочпслеппому зпачепию величины соответствует уровень сигпала

fy, A.:,

где ДО - велпчииа разпоса соседних уровней.

Апалого-дпскретпый сумматор реализует полученпе результата v суммирования / дпскретпых слагаемых (а, О, где ,2/)

модулю m | а; /п |, то есть

/

- 2(7 - k-ni,

2: / 1

где « определяется нз соотпошеиня

О - 0; - km, /«,

пли, применительно к прппятой аналоговой форме кодирования дискретных величин,- иолучепие дискретного уровня выходного сигнала

и. - la.; - Шт.

Аналого-дискретный сумматор работает следующим образом.

В исходном состоянии слагаемые на входы входного сумматора I не поступают (суммар;пый входной снгнал Et/i оказывается рав -1

ным нулю), вследствие чего па входы аналоговых сумматоров 4 с выхода входного аналогового сумматора 1 и далее на входы пороговых элементов 5 также поступает сигнал, равный пулю. Каждый пороговый элемент построен таким образом, что его выход возбуждается при достпженин и нревышенни С1Пналом на входе порогового элемепта уровня t7,u--А(7-т. Поэтому в исходном состояппп выходы всех пороговых элементов 5 не возбуждены, все аналоговые ключи 8 заперты по управляющему входу, и с их выходов спгпалы па входы сумматоров У и 4 не поступают. Один из пороговых элементов 5 (верхний на чертеже) подготовлен к работе. Условия, разрешающие работу последующих пороговых элементов, могут возпикнуть лишь при возбуждении выходов нредыдущих пороговых элементов (для прпведенпого чертежа - начиная сверху) после некоторой задержки, определяемой цепью задерл ки 6, в результате срабатывания коммутирующего элемента 7 (например, включающего напряженне, пптающее соответствуюпл,пй пороговый элемент 5).

Еслп суммарный входной снгнал Sfy,,.

Um, на выходе устройства устанавливается

.

сигнал суммы U,, 26,;, при этом ни один нз пороговых элементов 5 не срабатывает.

Если же суммарный входной сигнал II

и,и,п, причем (k- , kUm,

i li I

TO on передается на входы аналоговых сумматоров 4, и в устройстве начинается переходной режим, в процессе которого последовательно (по чертежу - начиная сверху) срабатывают пороговые элементы 5 (возбуждение выхода предыдущего порогового элемента через ннтервал времеЕП, определяемый цепью

задержки 6, создает условия, разрешающие работу последующего). При этом в соответствующей последовательности открываются аналоговые ключи 8 и эталонные сигналы с их выходов поступают на вычитающие входы входного сумматора /. Время цепи задержки 6 выбирается таким образом, что к моменту срабатывання очередного /-го порогового элемепта 5 эталонные сигналы, поступающие с выходов нредыдущих аналоговых ключей 8, оказываются учтениымп, п па выходе входного сумматора / (и далее на сходе ш-го порогового элемепта 5) устапавливается промежуточное зпачепне сигнала:

,,-(у-1)./;л 1 1

Падение уровня сигнала па выходе входного сумматора / не приводит, однако, к изменению входных сигналов предыдущих пороговых элемеитов 5, так как компеисируется соответствующим возрастапием уровней сигпалов па входах апалоговых сумматоров 4, связапных с выходами аналоговых ключей 8, открытых предыдущими норогов 1ми элементами 5.

После окопчаппя переходного режима суммарпый сигнал, подаваемый на вычитающие входы входного сумматора / с выходов аналоговых ключей., оказывается равным k Um, в результате чего на выходе устройства устапавливается результат:

и.и.,

Шт.

(-I

При этом (и 4-1) и пороговый элемент 5 оказывается подготовленным к работе, однако входной сигнал И т, поступающий через соответствующий аналоговый сумматор 4, пе приводит к его срабатыванию, а также к срабатыванию всех последующих пороговых элемептов 5.

Предмет изобретения

1. Апалого-дискретный сумматор, содержан;ий входиой сумматор, источник эталонного сигнала, суммирующий блок, выполненный на аналоговом сумматоре, соединенном с пороговым элемептом, цепн задержки и коммутирующие элементы, отличающийся тем, что, с целью увеличения суммарного уровня входного сигнала и расширения области применения устройства, оно содержит ряд суммирующих блоков, основные входы которых соединены с выходом входного сумматора, а ииформацпопные входы которых подключены к выходу источника эталонных сигналов, причем управляющий вход предыдущего суммирующего блока соединен через последовательно включепные цепь задержки и коммутирующий

элемент с разрешающим входом последующего суммирующего блока, а дискретный выход каждого предыдущего суммирующего блока соединен с соответствующим входом этого же суммирующего блока, соответствующими входами всех предыдущих суммирующих блоков и соответствующими вычитающими входами входного сумматора. 2. Устройство по п. 1, отличающееся тем.

что в нем в каждый суммирующий блок введен аналоговый ключ, входы которого соединены- один с управляющим выходом порогового элемента, а другой - с информационным входом суммирующего блока, а выход аналогового ключа соединен с дискретным выходом суммирующего блока, разрещающий вход которого соединен с другим входом порогового элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ДИСКРЕТНЫЙ CyjyiMATOP | 1971 |

|

SU296114A1 |

| УСТРОЙСТВО для НЕКОГЕРЕНТНОГО ПРИЕМА СЛОЖНЫХ СИГНАЛОВ | 1970 |

|

SU265975A1 |

| УСТРОЙСТВО ДИСКРЕТНОГО ДЕЙСТВИЯ ДЛЯ ФОРМИРОВАНИЯ ФУНКЦИОНАЛЬНЫХ ВРЕМЕННЫХ ЗАДЕРЖЕК ЭЛЕКТРИЧЕСКИХ СИГНАЛОВ | 1970 |

|

SU280062A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ ОПТИМАЛЬНЫЙ ФИЛЬТР | 1973 |

|

SU369693A1 |

| АДАПТИВНЫЙ КОРРЕКТОР ДЛЯ ДИСКРЕТНОГС КАНАЛА СВЯЗИФО!1Д mm | 1972 |

|

SU423254A1 |

| Устройство для управления режимом нагрева многозонной печи | 1983 |

|

SU1137452A1 |

| УСТРОЙСТВО ДЛЯ СЖАТИЯ И КОДИРОВАНИЯ АНАЛОГОВЫХ СООБЩЕНИЙ В СИСТЕМАХ С КОДОВО-ИМПУЛЬСНОЙ МОДУЛЯЦИЕЙ | 1973 |

|

SU409277A1 |

| Запоминающее устройство | 1980 |

|

SU926719A1 |

| Устройство для определения объема контролируемых параметров | 1984 |

|

SU1168903A1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА КОМБИНИРОВАННОГО РЕГУЛИРОВАНИЯ | 1989 |

|

RU2022313C1 |

Авторы

Даты

1973-01-01—Публикация