Предлагаемое изобретение относится к области вычислительной техники и может быть использовано при построении аналого-дискретных устройств.

Известен аналого-дискретный сумматор, Содержащий два сумматора аналоговых величин и пороговую схему. В нем выход первого сумматора аналоговых величин подключен к входу второго сумматора, выход которого, используемый как выход аналого-дискретного сумматора, подан на вход пороговой схемы, выход которой, в свою очередь, подключен к входу второго сумматора аналоговых величин.

Недостатком известного устройства является необходимость большого динамического Диапазона первого сумматора аналоговых веЛйчин. Он должен быть рассчитан на неискаженное воспроизведение максимальной суммы входных величин.

Вследствие этого на практике приходится либо применять в первом сумматоре более высоковольтные приборы и соответствующие источники питания, либо снижать масштаб воспроизведения величин. Это приводит в первом случае к усложнению конструкции, а во втором - к неудовлетворительному использованию динамического диапазона сумматора, т. е. к сокращению числа квантованных уровней.

В предлагаемом апалого-дискретном сумматоре вход пороговой схемы подключен к выходу второго сумматора аналоговых величин, ее выход подан на входы первого и второго сумматора, а выход первого сумматора аналоговых величин использован в качестве выхода аналого-дискретпого сумматора. С помощью цепи отрицательной обратной связи, возбул даемой при больших значениях суммы входных величин, обеспечивается уменьшение результирующего сигнала на входе первого сумматора.

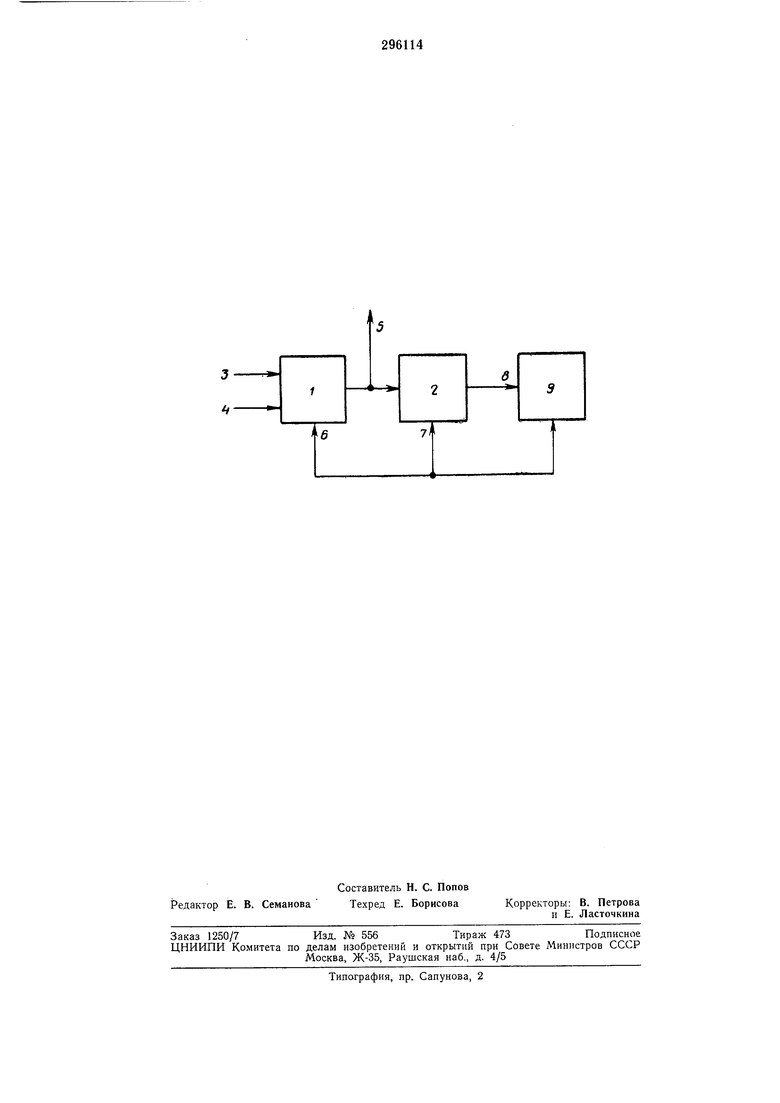

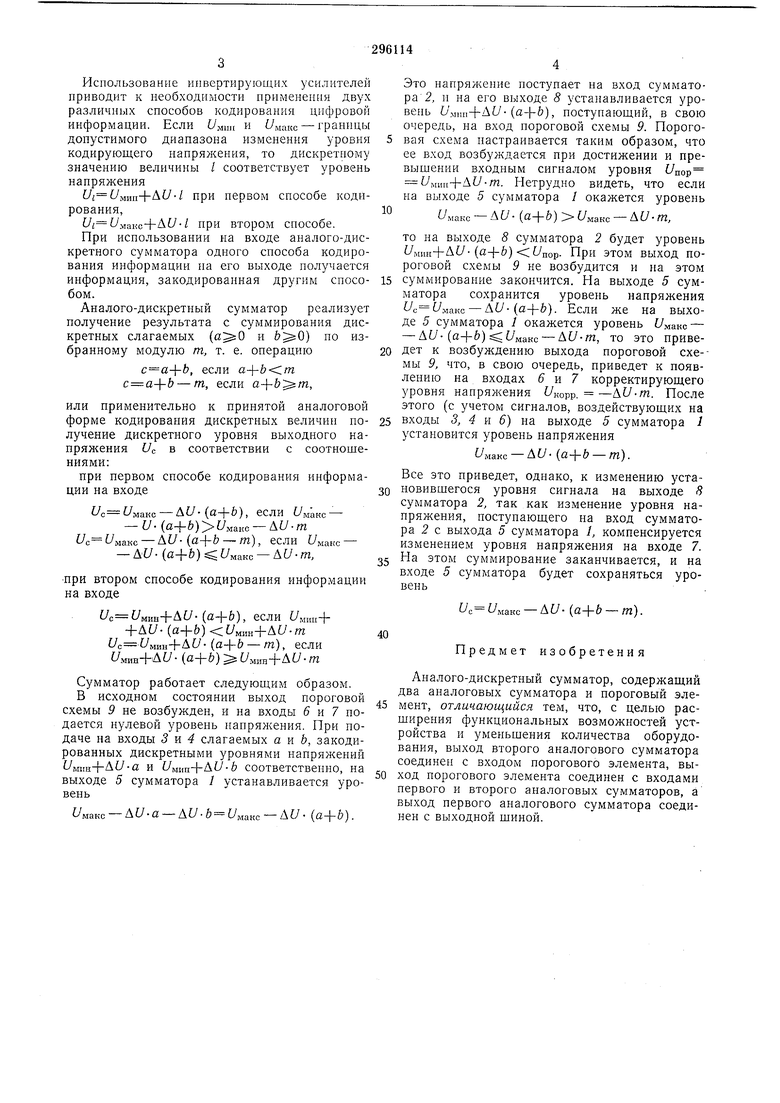

На чертеже представлена блок-схема предлагаемого аналого-дискретного сумматора.

Предлагаемое устройство содержит первый и второй сумматоры / и 2 аналоговых величин соответственно, входы 3 и 4 первого сумматора для подачи слагаемых, выход 5 первого сумматора аналоговых величин, являющийся выходом аналого-дискретного сумматора, дополнительпые входы 5 и 7 первого и второго сумматоров аналоговых величин соответственно, выход 8 второго сумматора и пороговую схему 9.

Принцип работы сумматора удобнее пояснить применительно к аналого-дпскретпому сумматору напряжений с сумматорами аналоговых величин, выполненными в виде однокаскадных (инвертирующих) усилителей с Использование инвертирующих усилителей приводит к необходимости применения двух различных способов кодирования цифровой информации. Если Umm и бмакс - грапицы допустимого диапазона изменения уровня кодирующего напряжения, то дискретному значению величины / соответствует уровень напряжения t i MHii+Af/-/ при нервом способе кодирования, и 1 и:, I при втором способе. При использовании на входе аналого-дискретного сумматора одного способа кодирования информации па его выходе получается информация, закодированная другим способом. Аналого-дискретный сумматор реализует получение результата с суммирования дискретных слагаемых ( и ) но избранному модулю т, т. е. операцию , если - т, если а-}-Ь т, или применительно к принятой аналоговой форме кодирования дискретных величин получение дискретного уровня выходного напряжения Uc в соответствии с соотношениями:при первом способе кодирования информации на входе f c t/MaKc (а+6), если С/макс - - t/.(a+6)t/MaKC -At/-m с Ьмакс-At/- (а + Ь -m), если /макс- - &и- (а+Ь) t/макс - Um, при втором способе кодирования информации на входе t/c i/MHH+AI/-(а+Ь), если (7мип+ +&U- (а+Ь) г;мнн+А 7-т UC UMHH+ U-( - т), если t/Mira+At/- (а+)/7мин+А /-т Сумматор работает следующим образом. В исходном состоянии выход пороговой схемы 9 не возбужден, и на входы 6 и 7 подается нулевой уровень напряжения. При подаче на входы 3 W. 4 слагаемых а и Ь, закодированных дискретными уровнями напряжений /м1ш+А(У-о; и f/Mira+At/-6 соответственно, на выходе 5 сумматора / устанавливается уровеньi/макс - Ua - At/. 6 t/макс - &U (й + Ь). Это напряжение поступает на вход сумматора 2, и на его выходе 8 устанавливается уровень умип+А /-(а+6), поступающий, в свою очередь, на вход пороговой схемы 9. Пороговая схема настраивается таким образом, что ее вход возбуждается при достижении и превышении входным сигналом уровня t/nop ыии+АУ-т. Нетрудно видеть, что если на выходе 5 сумматора / окажется уровень -At/- (a+&)f/MaKc -A6/-m, то на выходе 8 сумматора 2 будет уровень Ьмип+Аб-(а+6) Lnop. При этом выход пороговой схемы 9 не возбудится и на этом суммирование закончится. На выходе 5 сумматора сохранится уровень напряжения (с -Afy-(а+&). Если же на выходе 5 сумматора / окажется уровень i/макс - - Af/-(а+&) t/макс - А(7-т, то это приведет к возбуждению выхода пороговой схе-мы 9, что, в СБОЮ очередь, приведет к появлению на входах 6 и 7 корректирующего уровня напряжения t/корр. -At/-m. После этого (с учетом сигналов, воздействующих на входы 3, 4 и 6) на выходе 5 сумматора 1 установится уровень нанряжения макс -АС/-(a-f & -т). Все это приведет, однако, к изменению установивщегося уровня сигнала на выходе i9 сумматора 2, так как изменение уровня напряжения, постунающего на вход сумматора 2 с выхода 5 сумматора 1, компенсируется изменением уровня напряжения на входе 7. На этом суммирование заканчивается, и на входе 5 сумматора будет сохраняться уровень - AL- ( - m). Предмет изобретения Аналого-дискретный сумматор, содержащий два аналоговых сумматора и пороговый элемент, отличающийся тем, что, с целью расширения функциональных возможностей устройства и уменьщения количества оборудования, выход второго аналогового сумматора соединен с входом порогового элемента, выход порогового элемента соединен с входами первого и второго аналоговых сумматоров, а выход первого аналогового сумматора соединен с выходной шиной.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ДИСКРЕТНЫЙ СУММАТОР | 1973 |

|

SU382100A1 |

| Прибор для измерения частотных характеристик | 1986 |

|

SU1335935A1 |

| Демодулятор взаимоортогональных синусоидальных сигналов с фазоразностной модуляцией | 1985 |

|

SU1277423A1 |

| Цифровой согласованный фильтр | 1980 |

|

SU944077A1 |

| Устройство для контроля параметров | 1986 |

|

SU1339502A1 |

| Устройство для разделения направлений передачи в дуплексных системах связи | 1986 |

|

SU1390803A1 |

| Устройство для измерения активного сопротивления | 1990 |

|

SU1798733A1 |

| Перестраиваемый демодулятор дискретных сигналов | 1986 |

|

SU1401637A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ОПТИМАЛЬНОГО ИЗМЕРЕНИЯ ФАЗЫ СИГНАЛА | 1972 |

|

SU412565A1 |

| Устройство для вычисления взвешенного временного ряда | 1976 |

|

SU636620A1 |

Даты

1971-01-01—Публикация