,1

Изобретение отиосится к вычислительной технике и может быть иснользовано при построении вычислительных устройств, работающих в десятичной системе счисления и использующих фазоимпульсное представление десятичных чисел.

Известно десятичное устройство умножения, работающее нри фазоимпульсном представлении десятичных чисел (операндов), содержащее триггеры, линии задержки, логические элементы.

Это устройство содержит сложные матрицы произведений и нереносов. Кроме того, в нем используют промежуточные преобразователи фазоимпульсных кодов в пространственноимпульсные и обратно, что также усложняет устройство.

Цель изобретения - реализация умножения чисел, представленных фазоимпульсными кодами, без промежуточного их преобразования упрощение устройства и повышение его надежности.

Поставленная цель достигается тем,.что устройство содержит перестраиваемый многоустойчивый фазоимпульсный элемент с коммутатором числа его устойчивых состояний, фазоимпульсные многоустойчивые счетные и запоминающие элементы, связи между которыми обеспечивают формирование сигналов произведения и переноса.

2

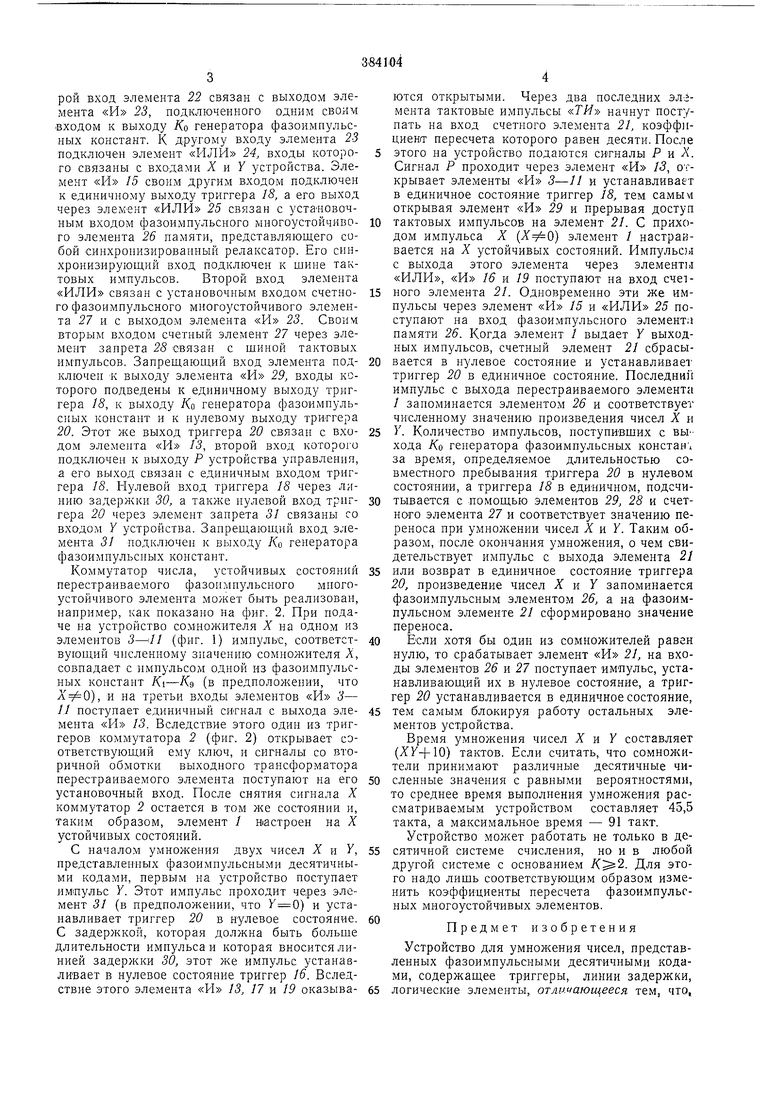

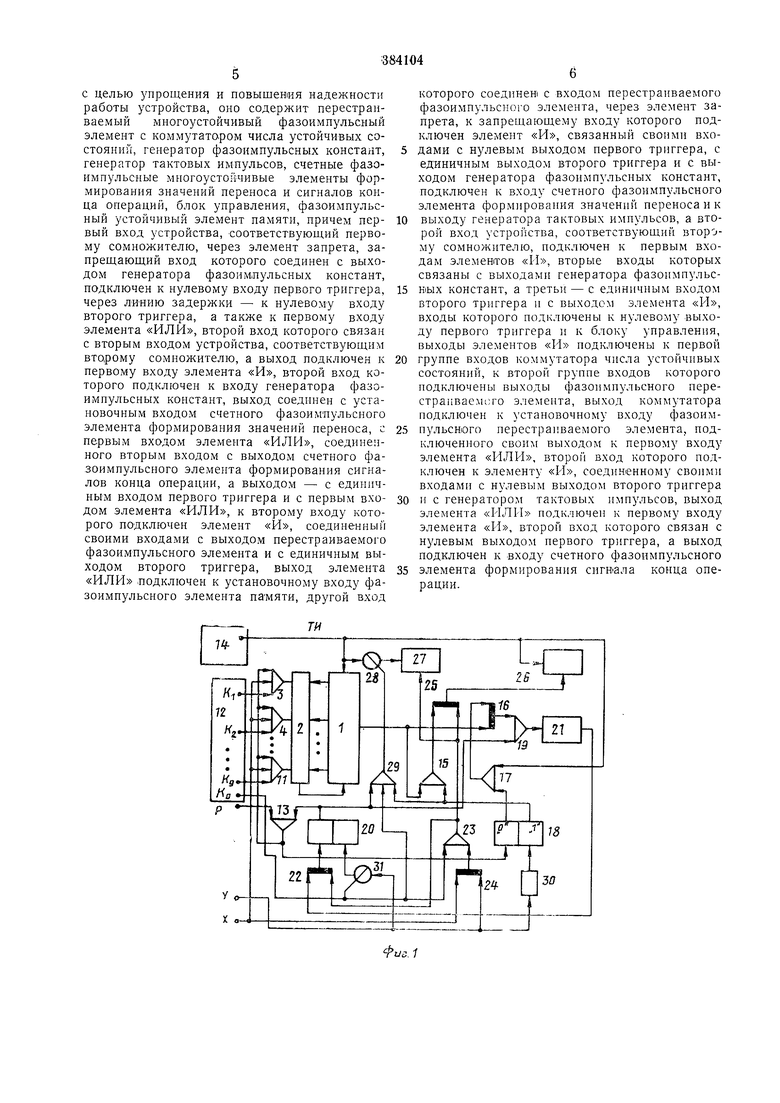

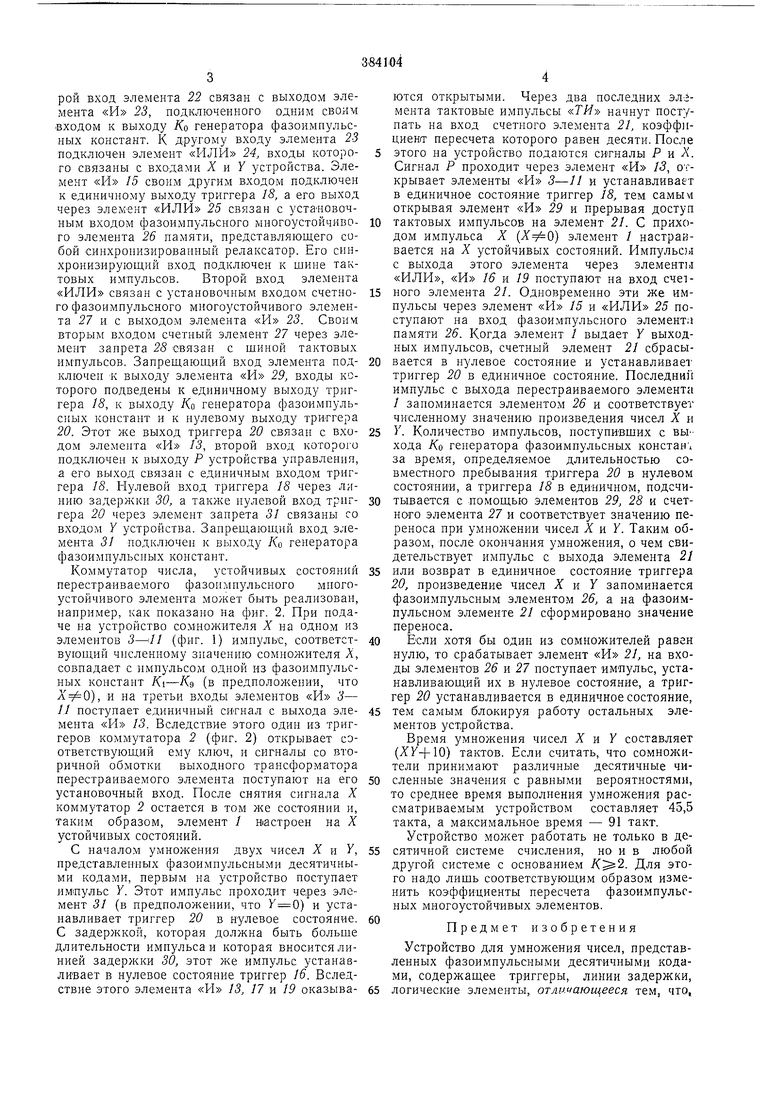

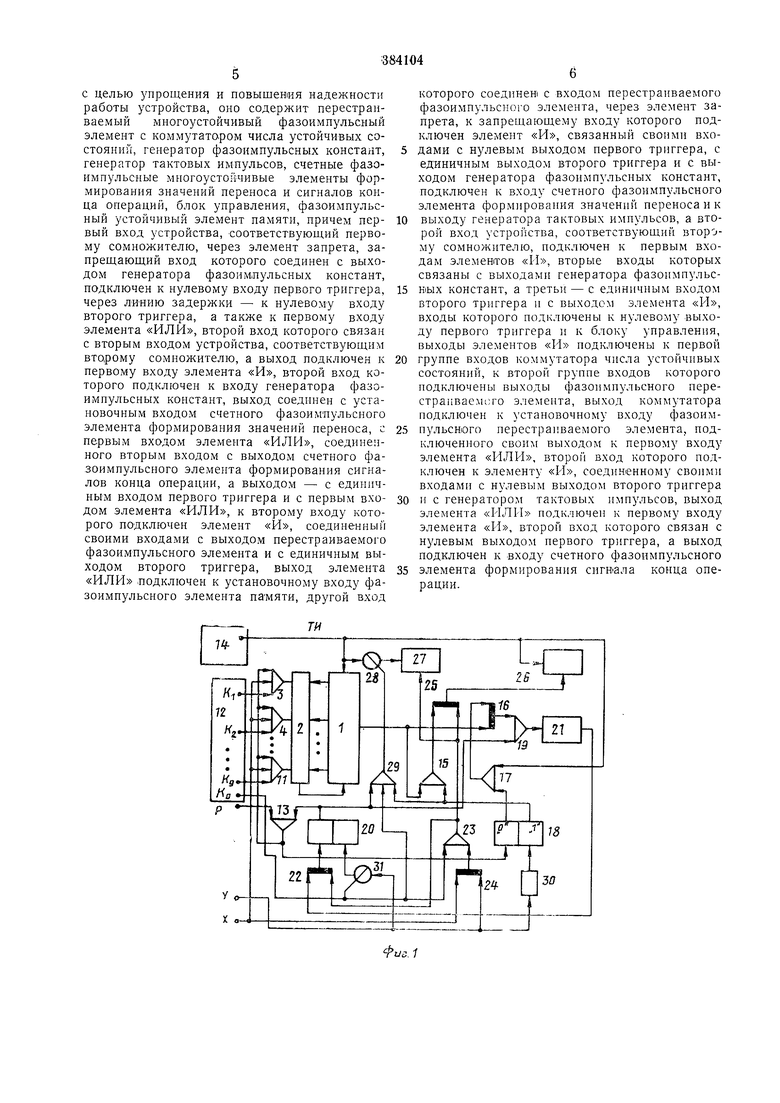

На фиг. 1 изображена функциональная схима устройства; на фиг. 2 - функциональная схема коммутатора числа устойчивых состояний перестраиваемого фазопмпульсного многоустойчнвого элемента.

Множительное устройство (фиг. 1) содержит перестраиваемый фазоимнульсный многоустойчивый элемент /. Выходы этого элемента подключе}П)1 к коммутатору 2 числа устойчивных состояни. Со второй группой входов коммутатора 2 соединены выходы девяти эле Ментов «И 3-//, входы которых подключеН1Ы к выходам Ki, К,---, Kg генератора 12 фазоимпульсны.х констант, к выходу элемента «И 13 и к входу А устройства. Выход коммутатора 2 соединен с установочным входом перестранваемого элемента /, связанного своим другим входом с шиной тактовых импульсов генератора 14. Выход элемента / соединен

с входами элементов «И 15 и «ИЛИ 16. К другому входу элемента 16 подключен выход элемента «II /7, соединенного своими входами с нулевым выходом триггера 18 и с шиной тактовых импульсов. Выход схемы 16

подключен к входу элемента «И 19, вторым своим входом связанного с нулевым выходом триггера 20. Выход элемента 19 подключен к входу счетиого фазоймнульоюго элемента 21, выход которого через элемент «ИЛИ 22 подключей к единичному входу триггера 20. Второй вход элемента 22 связан с выходом элемента «И 23, подключенного одним своим входом к выходу Ко генератора фазоимпульсных констант. К другому входу элемента 23 подключен элемент «ИЛИ 24, входы которого связаны с входами X и Y устройства. Элемент «И 15 своим другим входом подключен к единичному выходу триггера 18, а его выход через элемент «ИЛИ 25 связан с уста-новочиым входом фазоимпульсного многоустойчивого элемента 26 памяти, представляющего собой синхронизированный релаксатор. Его синхронизирующий вход подключен к щине тактовых импульсов. Второй вход элемента «ИЛИ связан с установочным входом счетного фазоимпульсного многоустойчивого элемента 27 и с выходом элемента «И 23. Своим вторым входом счетный элемент 27 через элемент запрета 28 связан с щиной тактовых импульсов. Запрещающий вход элемента подключен К выходу элемента «И 29, входы которого подведены к единичному выходу триггера 18, к выходу Ко генератора фазоимиульсных констант н к нулевому выходу триггера 20. Этот же выход триггера 20 связан с входом элемента «И 13, второй вход которого подключен к выходу Р устройства управления, а его выход связан с единичным входом триггера 18. Нулевой вход триггера /8 через линию задержки 30, а также нулевой вход триггера 20 через элемент запрета 31 связаны со входом Y устройства. Запрещающий вход элемента 31 подключен к выходу Ко генератора фазоимнульсиых констант.

Коммутатор числа, устойчивых состояний перестраиваемого фазоимиульсного многоустойчивого элемента может быть реализован, например, как показано на фиг. 2. При подаче на устройство сомножителя X на одном из элементов (фиг. 1) импульс, соответствующий численному значению сомножителя X, совпадает с импульсом одной из фазоимпульсных констант Ki-Kg (в предположении, что ), и на третьи входы элементов «И // поступает единичный сигнал с выхода элемента «И 13. Вследствие этого один из триггеров коммутатора 2 (фиг. 2) открывает соответствующий ему ключ, и сигналы со вторичной обмотки выходного трансформатора перестраиваемого элемента поступают на его установочный вход. После снятия сигнала X коммутатор 2 остается в том же состоянии и, таким образом, элемент / настроен на X устойчивых состояний.

С началом умножения двух чисел X и У, представленных фазоимпульсными десятичными кодами, первым на устройство поступает импульс У. Этот импульс проходит через элемент 31 (в предположении, что ) и устанавливает триггер 20 в нулевое состояние. С задержкой, которая должна быть больще длительности импульса и которая вносится линией задержки 30, этот же импульс устанавливает в нулевое состояние триггер 16. Вследствие этого элемента «И 13, 17 и 19 оказываются открытыми. Через два последних элемента тактовые импульсы «ГЯ начнут поступать на вход счетного элемента 21, коэффициенгг пересчета которого равен десяти. После этого на устройство подаются сигналы Р н X. Сигнал Р проходит через элемент «И 13, открывает элементы «И 3-11 и устанавливает в единичное состояние триггер 18, тем самый открывая элемент «И 29 и прерывая доступ

тактовых импульсов на элемент 21. С приходом импульса X () элемент / настраивается на X устойчивых состояний. Импульол с выхода этого элемента через элементы «ИЛИ, «И 16 и 19 поступают на вход счетного элемента 21. Одновременно эти же импульсы через элемент «И 15 и «ИЛИ 25 поступают на вход фазоимпульсного элемента памяти 26. Когда элемент / выдает У выходных импульсов, счетный элемент 21 сбрасывается в нулевое состояние и устанавливает триггер 20 в единичное состояние. Последнн импульс с выхода перестраиваемого элемента / запоминается элементом 26 и соответствует численному значению произведения чисел X и

У. Количество импульсов, поступивщих с выхода Ко генератора фазоимпульсных констант за время, определяемое длительностью совместного пребывания триггера 20 в нулевом состоянии, а триггера 18 в единичном, подсчитывается с помощью элементов 29, 28 и счетного элемента 27 и соответствует значению переноса при умножении чисел X к Y. Таким образом, после окончания умножения, о чем свидетельствует импульс с выхода элемента 21

или возврат в единичное состояние триггера 20, произведение чисел X и Y запоминается фазоимпульсным элементом 26, а на фазоимпульсном элементе 21 сформировано значение переноса.

Если хотя бы один из сомножителей равен нулю, то срабатывает элемент «И 21, на входы элементов 26 и 27 поступает импульс, устанавливающий их в нулевое состояние, а триггер 20 устанавливается в единичное состояние,

тем самым блокируя работу остальных элементов устройства.

Вре.мя умножения чисел X и У составляет (ХУ+10) тактов. Если считать, что сомножители принимают различные десятичные численные значения с равными вероятностями, то среднее время выполнения умножения рассматриваемым устройством составляет 45,5 такта, а максимальное время - 91 такт. Устройство может работать не только в десятичной системе счисления, но и в любой другой системе с основание.м . Для этого надо лищь соответствующим образом изменить коэффициенты пересчета фазоимпульсных многоустойчивых элементов.

п

Предмет изобретения

Устройство для умножения чисел, представленных фазоимпульсными десятичными кодами, содержащее триггеры, линии задержки, логические элементы, отличающееся тем, что,

с целью упрощения и повышения надежности работы устройства, оно содержит перестраиваемый многоустойчивый фазоимпульсный элемент с коммутатором числа устойчивых состояний, генератор фазоимпульсных констант, генератор тактовых импульсов, счетные фазоимпульсные многоустойчивые элементы формирования значений переноса и сигналов конца операций, блок управления, фазоимпульсный устойчивый элемент памяти, причем первый вход устройства, соответствующий первому сомножителю, через элемент запрета, запрещающий вход которого соединен с выходом генератора фазоимлульсных констант, подключен к нулевому входу первого триггера, через линию задержки - к нулевому входу второго триггера, а также к первому входу элемента «ИЛИ, второй вход которого связан с вторым входом устройства, соответствующим второму сомножителю, а выход подключен к первому входу элемента «И, второй вход которого подключен к входу генератора фазоимпульсных констант, выход соединен с установочным входом счетного фазой мпульсного элемента формирования значений переноса, с первым входом элемента «ИЛИ, соединенного вторым входом с выходом счетного фазоимпульсного элемента формирования сигналов конца операции, а выходом - с единичным входом первого триггера и с первым входом элемента «ИЛИ, к второму входу которого подключен элемент «И, соединенный своими входами с выходом перестраиваемого фазоимпульсного элемента и с единичным выходом второго триггера, выход элемента «ИЛИ подключен к установочному входу фазоимпульсного элемента памяти, другой вход

которого соединен с входом перестраиваемого фазоимпульсного элемента, через элемент запрета, к запрещающему входу которого подключен элемент «И, связанный своими входами с нулевым выходом первого триггера, с единичным выходом второго триггера и с выходом генератора фазоимпульсных констант, подключен к входу счетного фазоимпульсного элемента формирования значений переноса и к

выходу генератора тактовых импульсов, а второй вход устройства, соответствующий второму сомножителю, подключен к первым входам элемевтов «И, вторые входы которых связаны с выходами генератора фазоимпульсных констант, а третьи - с единичным входом второго триггера н с выходом элемента «И, входы которого подключены к нулевому выходу первого триггера и к блоку управления, выходы элементов «И подключены к первой

группе входов коммутатора числа устойчивых состояний, к второй группе входов которого подключены выходы фазоимпульсного перестрапваемсго элемента, выход коммутатора подключен к установочному входу фазоимпульсного иерестраиваемого элемента, подключенного своим выходом к первому входу элемента «ИЛИ, второй вход которого подключен к элементу «И, соединенному своими входами с нулевым выходом второго триггера

и с генератором тактовых импульсов, выход элемента «ИЛИ подключен к первому входу элемента «И, второй вход которого связан с нулевым выходом нервого Tpiirrepa, а выход подключен к входу счетного фазоимпульсного

элемента формирования сигвала конца операции.

fpvz 2

Выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел, представленных фазо-импульсными кодами | 1972 |

|

SU439807A1 |

| УСТРОЙСТВО для УСТАНОВКИ ЗАПЯТОЙ СУММИРУЮЩЕЙ КЛАВИШНОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1973 |

|

SU367419A1 |

| Устройство для преобразования кодов | 1974 |

|

SU556429A1 |

| РЕВЕРСИВНЫЙ СЧЕТЧИК | 1973 |

|

SU362490A1 |

| СЧЕТЧИК С ПРЕДВАРИТЕЛЬНОЙ УСТАНОВКОЙ | 1971 |

|

SU322855A1 |

| Перестраиваемый фазоимпульсный многоустойчивый блок | 1974 |

|

SU511589A1 |

| Цифровой вторичный индикатор времени | 1977 |

|

SU708291A1 |

| Перестраиваемый фазо-импульсный многоустойчивый элемент | 1974 |

|

SU546937A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

Авторы

Даты

1973-01-01—Публикация