1

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в цифровых вычислительных машинах.

Известно устройство для умножения чисел, иредставлеииых фазо-и; ;пульсными кодами, содержащее перестраи.заемый фазо-импульсный элемент с коммутатором числа устойчивых состояний, счетные фазо-импульсиые многоустойчивые элементы, фазо-импульсный многоустойчивый элемент памяти, двоичные триггеры, ли.иин задержки, логические схемы «И, «ИЛИ, «Запрет. Иеремножеиие двух десятичных чисел в этом устройстве происходит путем пастройки иерестраиваемого элемента на число устойчивых состояний, равное одному из сомножителей, и путем фиксирования числа срабатывани этого элемента, которое равно значению другого сомножителя. Произведение ири этом формируется на фазо-имнульсиом М1;огоустойчивол1 элементе памяти, а неренос -- на счетном фазо-им пул ьсном многоустойчивом элеме1гге.

Однако известное устройство сравннтель110 сложно, что обуславливается иснользоваиием фазо-импульсного элемента памяти для запоминания произведения чисел.

Цель изобретения --- упрон1ение устройства.

Для достижения этого первый вход устройства соединен с импульсным входом задержки, второй вход устройства соединен со вторым входом первой схемы «:ИЛР1 и со входами группы вентилей, третий вход устройства соединен с запрещающим входом первой схемы «Запрет и со входами первой и второй схем «И,четвертый вход устройства соединен со входом третьей схемы «И, выход которой соед.инеи со вторыми входами группы вентилей и со входом установки «единицы первого триггера, вход установки «нуля этого триггера соединен с выходом линии задержки, единичный выход первого триггера соединен со вторым входом второй схемы «li, а нулевой выход этого триггера соединен со входом четвертой схемы «И, выход которой соединен с первым входом второй схемы «ИЛИ, а второй вход второй схемы «ИЛИ соединен с выходом перестраиваемого фазо-нмпульсного многоустойчивого элемента, выход BTopoii схемы -ИЛИ соединен со входолг нятой схемы , в)1ход которой связан со входом счетного фазэ-импульсного элемента окончання операции., а выход этого элемента соединен со входом коммутатора устойч1 вых состояний и со входом третьей схемы «ИЛ1Ь, второй вход первой схемы «И соединен с выходом первой схемы «ИЛИ, а выход первой схемы «И соединен со вторым входом третьей схемы «И.ДИ и со входом

фазо-импульсиого элемента переноса, второй вход которого соединен с выходом второй схемы «Запрет, выход третьей схемы «ИЛИ соедпнен со входом установки «единицы второго триггера, выход первой схемы «Запрет соединен со входом установки «нуля второго триггера, нулевой выход этого триггера соединен со вторыми входами третьей и пятой схем «И и с третьим входом второй схемы «И, выход второй схемы «И соединен с запрещающим входом второй схемы «Запрет, пятый вход устройства соединен со вторым входом перестраиваемого фазо-импульсного элемента, с импульсным входом второй схемы «Запрет и со вторым входом четвертой схемы «И, третьи входы группы вентилей являются входами устройства.

Это позволяет упростить устройство.

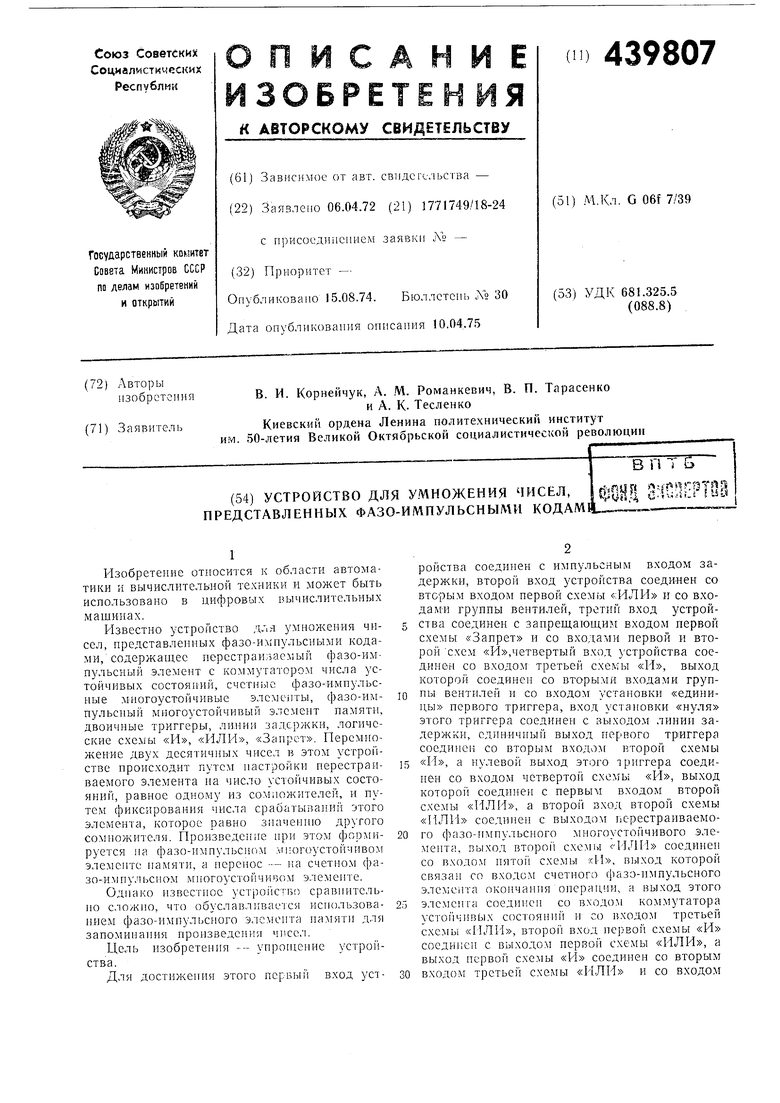

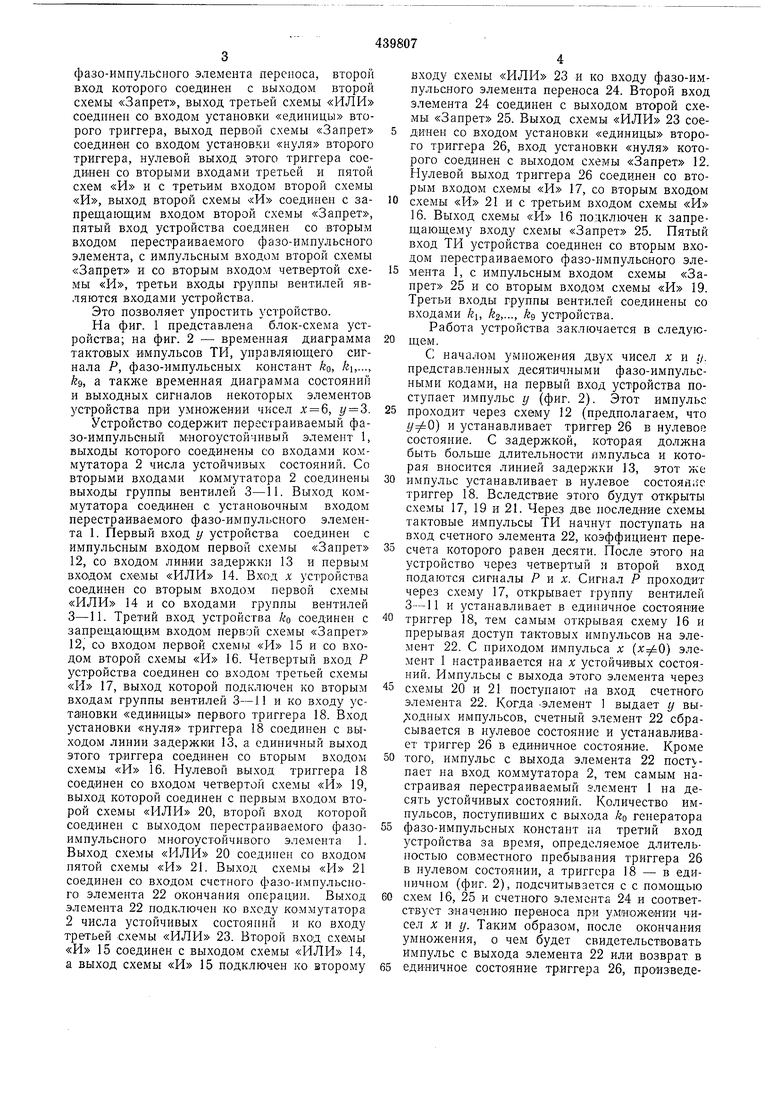

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - временная диаграмма тактовых импульсов ТИ, управляющего сигнала Р, фазо-импульсных констант /го, ki,..., kg, а также временная диаграмма состояний и выходных сигналов некоторых элементов устройства при умножении чисел х 6, г/ 3.

Устройство содержит перестраиваемый фазо-импульсный МНогоустойчнвый элемент 1, выходы которого соединены со входами коммутатора 2 числа устойчивых состояний. Со вторыми входами коммутатора 2 соединены выходы группы вентилей 3-И. Выход коммутатора соединен с установочным входом перестраиваемого фазо-импульсного элемента 1. Первый вход у устройства соединен с импульсным входом первой схемы «Запрет 12, со входом линии задержки 13 и первым входОМ схбмы «ИЛИ 14. Вход х устройства соединен со вторым входом первой схемы «ИЛИ 14 и со входами группы вентилей 3-11. Третий вход устройства ko соединен с запрещающим входом первой схемы «Запрет 12, со входом первой схемы «И 15 и со входом второй схемы «И 16. Четвертый вход Р устройства соединен со входом третьей схемы «И 17, выход которой подключен ко вторым входам группы вентилей 3-11 и ко входу установки «едиН(Ицы первого триггера 18. Вход установки «нуля триггера 18 соединен с выходом линии задержк и 13, а единичный выход этого триггера соединен со вторым входом схемы «И 16. Нулевой выход триггера 18 соединен со входом четвертой схемы «И 19, выход которой соединен с первым входом второй схемы «ИЛИ 20, второй вход которой соединен с выходом перестраиваемого фазоимпульсного многоустойчивого элемента 1. Выход схемы «ИЛИ 20 соединен со входом пятой схемы «И 21. Выход схемы «И 21 соединен со входом счетного фазо-нмпульсного элемента 22 окончания операции. Выход элемента 22 подключен ко входу коммутатора 2 числа устойчивых состояний и ко входу третьей схемы «ИЛИ 23. Второй вход схемы «И 15 соединен с выходом схемы «ИЛИ 14, а выход схемы «И 15 подключен ко второму

входу схемы «ИЛИ 23 и ко входу фазо-импульсного элемента переноса 24. Второй вход элемента 24 соединен с выходом второй схемы «Запрет 25. Выход схемы «ИЛИ 23 соединен со входом установки «единицы второго триггера 26, вход установки «нуля которого соединен с выходом схемы «Запрет 12. Нулевой выход триггера 26 соединен со вторым входом схемы «И 17, со вторым входом

схемы «И 21 и с третьим входом схемы «И 16. Выход схемы «И 16 подключен к запрещающему входу схемы «Запрет 25. Пятый вход ТИ устройства соединен со вторым входом перестраиваемого фазо-нмпульсного элемента 1, с импульсным входом схемы «Запрет 25 и со вторым входом схемы «И 19. Третьи входы группы вентилей соединены со входами k-i, kz,..., kg устройства.

Работа устройства заключается в следующем.

с; началом умножения двух чисел х и //. представленных десятичными фазо-импульсными кодами, на первый вход устройства поступает импульс у (фиг. 2). Этот импульс

проходит через схему 12 (предполагаем, что ) и устанавливает триггер 26 в нулевое состояние. С задержкой, которая должна быть больше длительности импульса и которая вносится линией задержки 13, этот же импульс устанавливает в нулевое состояяле триггер 18. Вследствие этого будут открыты схемы 17, 19 и 21. Через две носледние схемы тактовые импульсы ТИ начнут поступать на вход счетного элемента 22, коэффициент пересчета которого равен десяти. После этого на устройство через четвертый и второй вход подаются сигналы Р и х. Сигнал Р проходит через схему 17, открывает группу вентилей 3-11 и устанавливает в единичное состояние триггер 18, тем самым открывая схему 16 и прерывая доступ тактовых импульсов на элемент 22. С приходом импульса х () элемент 1 настраивается на х устойчивых состояний. Импульсы с выхода этого элемента через

схемы 20 и 21 ноступают на вход счетного элемента 22. Когда -элемент 1 выдает у вы;ходных импульсов, счетный элемент 22 сбрасывается в нулевое состояние и устанавливает триггер 26 в единичное состояние. Кроме

того, импульс с выхода элемента 22 поступает на вход коммутатора 2, тем самым настраивая перестраиваемый элемент 1 на десять устойчивых состояний. Количество импульсов, поступивших с выхода ko генератора

фазо-импульсных констант на третий вход Зстройства за время, определяемое длительностью совместного пребывания триггера 26 в нулевом состоянии, а триггера 18 - в единичном (фиг. 2), подсчитывается с с помощью

схем 16, 25 и счетного элемента 24 и соответствует значению переноса при умиож&нии чисел X и у. Таким образом, после окончания умножения, о чем будет свидетельствовать импульс с выхода элемента 22 или возврат в

единичное состояние триггера 26, произведение чисел хну запомнится элементом 1, а на элементе 24 будет сформировано зиачение переноса.

Если хотя бы один из сомножителей равен нулю, то сработает схема 15, на вход элемента 24 поступит импульс, устанавливающий его в нулевое состояние, а триггер 26 установится в единичное состояние, тем самым блокируя работу остальных элементов устройства.

Описанное устройство может работать не только в десятичной системе счисления, но и в любой другой системе с основанием . Для этого надо лишь соответствующим образом изменить коэффициенты пересчета элементов 24 и 22.

Предмет изобретения

Устройство для умножения чисел, представленных фазо-нмпульсными кодами, содержащее два триггера, два счетных фазоимпульсных многоустойчивых элемента, логические схемы «И, «ИЛИ, «Запрет, линии задержки, перестраиваемый фазо-импульсный многоустойчивый элемент, выходы которого соединены со входами коммутатора числа устойчивых состояний, выход которого соединен с установочным входом перестраиваемого фазо-импульсного многоустойчивого элемента, отличающееся тем, что, с целью упрощения устройства, первый вход устройства соединен с импульсным входом задержки, второй вход устройства соединен со вторым входом первой схемы «ИЛИ и со входами группы вентилей, третий вход устройства соединен с запрещающим входом первой схемы «Запрет и со входами первой и второй схем «И, четвертый вход устройства соединен со входом

третьей схемы «И, выход которой соединен со вторыми входами группы вентилей и со входом установки «единицы первого триггера, вход установки «нуля этого триггера соединен с выходом линии задержки, единичный выход первого триггера соединен со вторым входом второй схемы «И, а нулевой выход этого триггера соединен со входом четвертой схемы «И, выход которой соединен с первым

входом второй схемы «ИЛИ, а второй вход второй схемы «ИЛИ соединен с выходом перестраиваемого фазо-импульсного многоустойчивого элемента, выход второй схемы «ИЛИ соединен со входом пятой схемы «И,

выход которой связан со входом счетного фазо-импульсного элемента окончания операции, а выход этого элемента соединен со входом коммутатора устойчивых состояний и со входом третьей схемы «ИЛИ, второй вход

первой схемы «И соединен с выходом первой схемы «ИЛИ, а выход первой схемы «И соединен со вторым входом третьей схемы «ИЛИ и со входом фазо-импульсного элемента переноса, второй вход которого соединей с выходом второй схемы «Запрет, выход третьей схемы «ИЛИ соединен со входом установки «единицы второго триггера, выход первой схемы «Запрет соединен со входом установки «нуля второго триггера, нулевой

выход этого триггера соединен со вторыми входами третьей и пятой схем «И и с третьим входом второй схемы «И, выход второй схемы «И соединен с запрещающим входом второй схемы «Запрет, пятый вход устройства соединен со вторым входом перестраиваемого фазо-импульсного элемента, с импульсным входом второй схемы «Запрет и со вторым входам четвертой схемы «И, третьи входы группы вентилей являются входами устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧИСЕЛ, НРЕДСТАВЛЕННЫХ ФАЗОИМПУЛЬСНЫМИ ДЕСЯТИЧНЫМИ КОДАМИ | 1973 |

|

SU384104A1 |

| Реверсивный счетчик импульсов | 1972 |

|

SU437231A1 |

| Квадратор | 1976 |

|

SU574728A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Устройство для преобразования кодов | 1974 |

|

SU556429A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| УСТРОЙСТВО для УСТАНОВКИ ЗАПЯТОЙ СУММИРУЮЩЕЙ КЛАВИШНОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1973 |

|

SU367419A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СЧЕТЧИКОМ ИМПУЛЬСОВ | 1968 |

|

SU208339A1 |

| Устройство для автоматического контроля генератора случайных чисел | 1982 |

|

SU1038942A1 |

Авторы

Даты

1974-08-15—Публикация

1972-04-06—Подача