1

Изобретение относится к области вычислительной техники и может быть использовано в цифровых вычислительных и измерительных устройствах.

Известен реверсивный счетчик на основе десятичного регистра, который содержит десятичный регистр на фазоимпульсных многоустойчивых элементах, десятичный фазоимпульсный сумматор, коммутатор разрядов, генератор констант, генератор тактовых импульсов, синхронизатор, триггеры и логические элементы.

Однако быстродействие известного счетчика относительно невысоко, так как его скорость

счета импульсов составляет имп/сек, где

20«

/ - частота тактовых импульсов; п - количество десятичных разрядов в регистре.

Целью изобретения является повышение быстродействия счетчика.

Поставленная цель достигается тем, что в счетчик дополнительно введены схемы «И и управляющий автомат, причем выход суммы сумматора через первую схему «И, второй вход которой соединен с первым выходом управляющего автомата, подсоединен ко входу регистра и ко второй и третьей схемам «И, вторые входы которых соединены с единичным и нулевым выводами триггера, нулевой вход

которого подключен к выходу переноса сумматора, причем выход второй схемы «И соединен со входом установки в исходное положение коммутатора разрядов и со вторым входом управляющего автомата, а выход третьей схемы «И соединен с единичным входом триггера, со входом сдвига коммутатора разрядов и через схему «ИЛИ, второй вход которой подсоединен ко входной клемме счетчика, с первым в.ходом управляющего автомата, третий вход которого соединен со входом сумматора и с выходом четвертой схемы «И, входы которой подключены к выходу регистра и ко второму выходу управляющего автомата. Входы сложения и вычитания сумматора соединены со входными клеммами.

Быстродействие описываемого ниже счетчика определяется выражениями:

Юл + 1

/

имп1сек

в режиме сложения. 10«+9 имп/сек

в режиме вычитания.

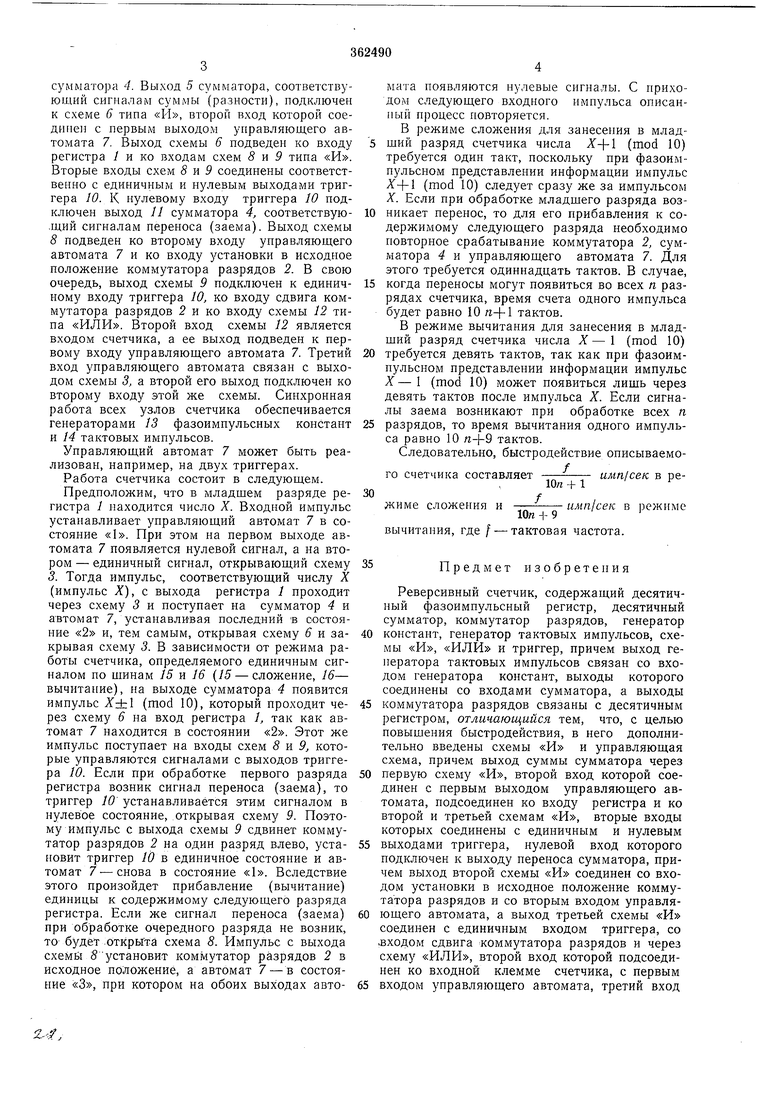

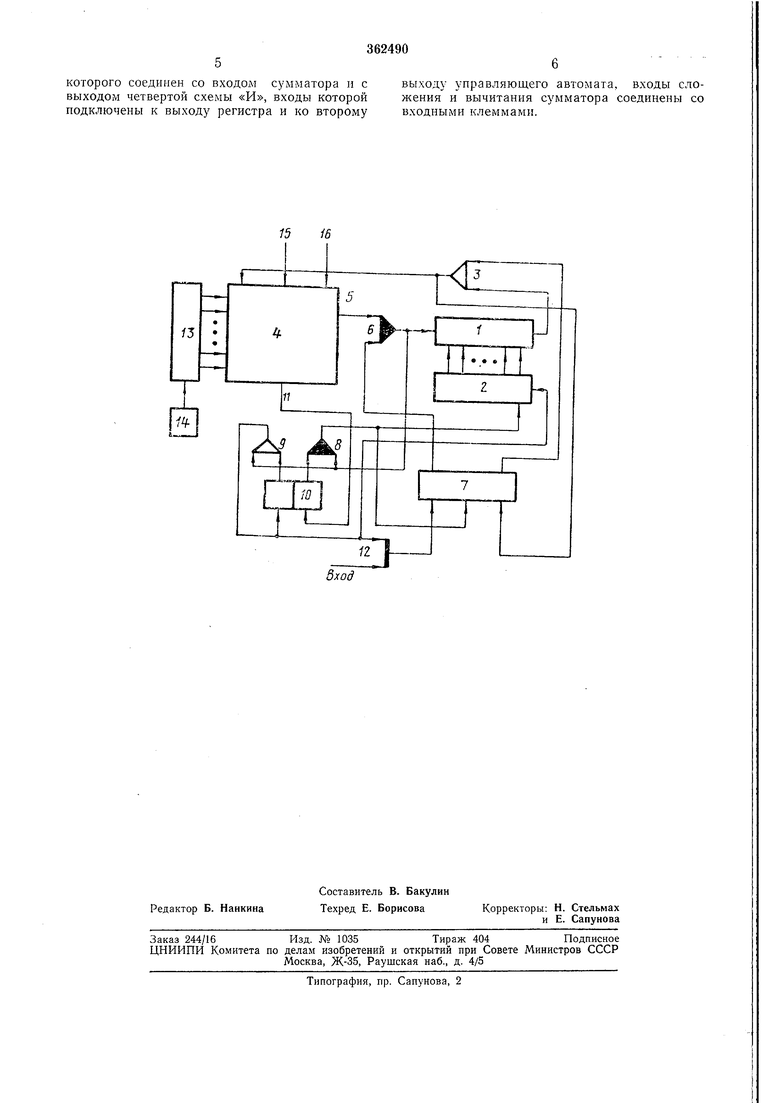

На чертеже изображена схема предлагаемого реверсивного счетчика.

Счетчик состоит из десятичного фазоимпульсного регистра 1, управляемого коммутатором разрядов 2. Выход регистра соединен со входом схемы 3 типа «И, выход которой подведен ко входу десятичного фазоимпульсного

сумыато эа 4. Выход 5 сумматора, соответствующий сигналам суммы (разности), подключен к схеме 6 типа «И, второй вход которой соедипеп с первым выходом управляющего автомата 7. Выход схемы 6 подведен ко входу регистра / и ко входам схем 8 и 9 типа «И. Вторые входы схем 5 и 9 соединены соответственно с единичным и нулевым выходами триггера 10. К пулевому входу триггера 10 подключен выход 11 сумматора 4, соответствующий сигналам переноса (заема). Выход схемы 8 подведен ко второму входу управляющего автомата 7 и ко входу установки в исходное положение коммутатора разрядов 2. В свою очередь, выход схемы 9 подключен к единичному входу триггера 10, ко входу сдвига коммутатора разрядов 2 и ко входу схемы 12 типа «ИЛИ. Второй вход схемы 12 является входом счетчика, а ее выход подведен к первому входу управляющего автомата 7. Третий вход управляющего автомата связан с выходом схемы 3, а второй его выход подключен ко второму входу этой же схемы. Синхронная работа всех узлов счетчика обеспечивается генераторами 13 фазоимнульсных констант и 14 тактовых импульсов.

Управляющий автомат 7 может быть реализован, например, на двух триггерах.

Работа счетчика состоит в следующем.

Предположим, что в младщем разряде регистра 1 паходится число X. Входной импульс устанавливает управляющий автомат 7 в состояние «1. При этом на первом выходе автомата 7 появляется нулевой сигнал, а на втором - единичный сигнал, открывающий схему 3. Тогда импульс, соответствующий числу X (импульс X), с выхода регистра 1 проходит через схему 3 и поступает на сумматор 4 и автомат 7, устанавливая последний в состояние «2 и, тем самым, открывая схему 6 и закрывая схему 3. В зависимости от режима работы счетчика, определяемого единичным сигналом по щинам 15 и 16 (15 - сложение, 16- вычитание), на выходе сумматора -i появится импульс Х± (mod 10), который проходит через схему 6 на вход регистра /, так как автомат 7 находится в состоянии «2. Этот же импульс поступает на входы схем 8 и 9, которые управляются сигналами с выходов триггера 10. Если при обработке первого разряда регистра возник сигнал переноса (заема), то триггер 10 устанавливается этим сигналом в пулевое состояние, открывая схему 9. Поэтому импульс с выхода схемы 9 сдвинет коммутатор разрядов 2 на один разряд влево, установит триггер 10 в единичное состояние и автомат 7--снова в состояние «1. Вследствие этого произойдет прибавление (вычитание) единицы к содержимому следующего разряда регистра. Если же сигнал переноса (заема) при обработке очередного разряда не возник, то будет открыта схема 8. Импульс с выхода схемь 8установит коммутатор разрядов 2 в исходное положение, а автомат 7 - в состояние «3, при котором на обоих выходах автомата появляются нулевые сигналы. С приходом следующего входного импульса описанный процесс повторяется.

В режиме сложения для занесения в младщий разряд счетчика числа (mod 10) требуется один такт, поскольку при фазоимпульсном представлении информации импульс Х+1 (mod 10) следует сразу же за импульсом X. Если при обработке младщего разряда возникает перенос, то для его прибавления к содержимому следующего разряда необходимо повторное срабатывание коммутатора 2, сумматора 4 и управляющего автомата 7. Для этого требуется одиннадцать тактов. В случае,

когда переносы могут появиться во всех п разрядах счетчика, время счета одного импульса будет равно 10 n-f-l тактов.

В режиме вычитания для занесения в младщий разряд счетчика числа X-1 (mod 10)

требуется девять тактов, так как при фазоимпульсном представлении информации импульс X- 1 (mod 10) может появиться лишь через девять тактов после импульса X. Если сигналы заема возникают при обработке всех п

разрядов, то время вычитания одного импульса равно 10 тактов. Следовательно, быстродействие описываемоимп/сек в рего счетчика составляет

10/г + 1

/

имп/сек в |зежнме

жиме сложения и

10« + 9

вычитания, где / - тактовая частота.

Предмет изобретения

Реверсивный счетчик, содержащий десятичный фазоимпульсный регистр, десятичный сумматор, коммутатор разрядов, генератор

констант, генератор тактовых импульсов, схемы «И, «ИЛИ и триггер, причем выход генератора тактовых импульсов связан со входом генератора констант, выходы которого соединены со входами сумматора, а выходы

коммутатора разрядов связаны с десятичным регистром, отличающийся тем, что, с целью повыщения быстродействия, в него дополнительно введены схемы «И и управляющая схема, причем выход суммы сумматора через

первую схему «И, второй вход которой соединен с первым выходом управляющего автомата, подсоединен ко входу регистра и ко второй и третьей схемам «И, вторые входы которых соединены с единичным и нулевым

выходами триггера, нулевой вход которого подключен к выходу нереноса сумматора, причем выход второй схемы «И соединен со входом установки в исходное положение коммутатора разрядов и со вторым входом управляющего автомата, а выход третьей схемы «И соединен с единичным входом триггера, со входом сдвига коммутатора разрядов и через схему «ИЛР1, второй вход которой подсоединен ко входной клемме счетчика, с первым

входом управляющего автомата, третий вход

которого соединен со входом сумматора и с выходом четвертой схемы «И, входы которой подключены к выходу регистра и ко второму

выходу управляющего автомата, входы сложения и вычитания сумматора соединены со входными клеммами.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Устройство для деления п-разрядных десятичных чисел | 1976 |

|

SU742933A1 |

| Устройство для деления | 1980 |

|

SU949653A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Десятичный сумматор | 1973 |

|

SU491947A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1554143A1 |

| Устройство для вычисления среднеквадратического отклонения | 1974 |

|

SU518777A1 |

| Преобразователь двоично-десятичного кода в последовательный двоичный код | 1974 |

|

SU543934A1 |

| Устройство для формирования импульсов | 1985 |

|

SU1285574A1 |

/5 /6

ёход

Авторы

Даты

1973-01-01—Публикация