1

Изобретение относится к автоматике и вычислительной технике, в частности к области управления запоминающими устройствами.

Известен коммутатор, содержащий два ряда сердечников с тактовыми обмотками, обмотками записи, основными и дополнительными распределительными обмотками, два формирователя тока такта, формирователь адресного тока считывания и записи.

Цель изобретения - повышение надежности устройства. Достигается она тем, что в предлагаемый коммутатор введены конденсатор, резистор и импульсный трансформатор с двумя первичными и двумя вторичными обмотками, первичные обмотки которого подключены к выходам формирователей тока и к тактовым обмоткам сердечников коммутатора соответственно первого и второго тактов, вторичные обмотки объединены и подключены к выходу формирователя адресного тока и к общим точкам дополнительных распределительных обмоток соответственно первого и второго тактов; параллельно одной из первичных обмоток импульсного трансформатора подключены последовательно соединенные конденсатор и резистор; дополнительные распределительные обмотки через диоды и адресные шины накопителя подключены к формирователю адресного тока, а основные распределительные обмотки, через диоды подведены к источнику питания.

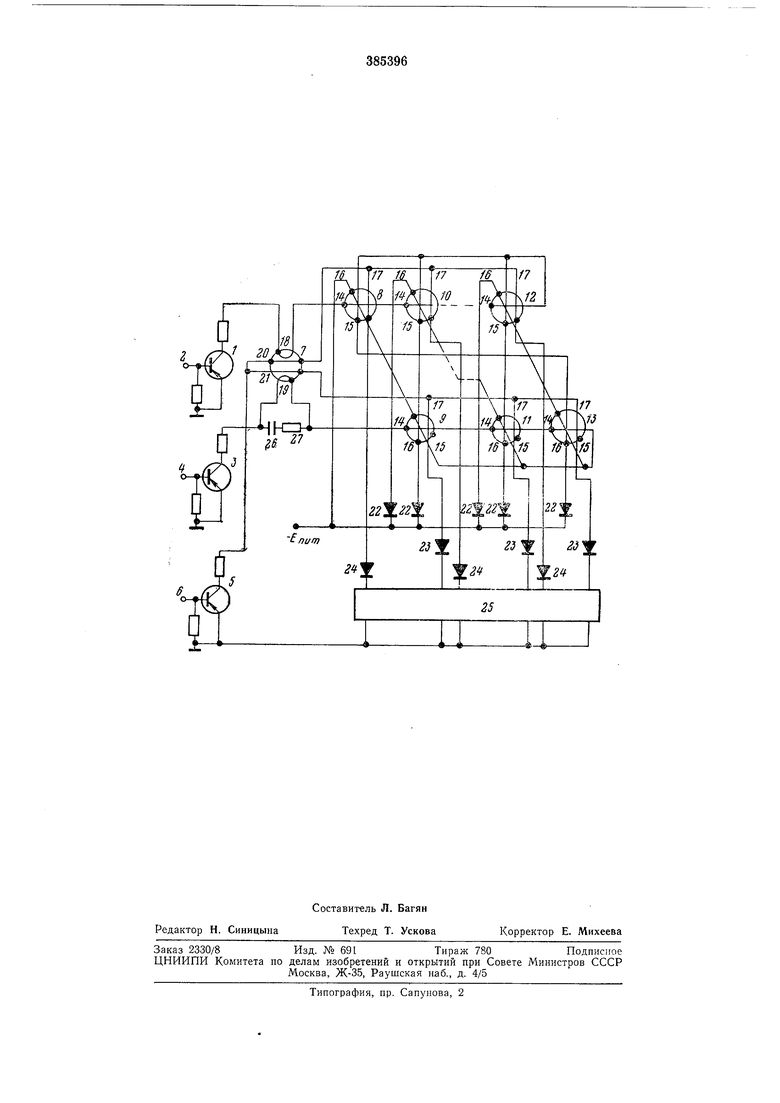

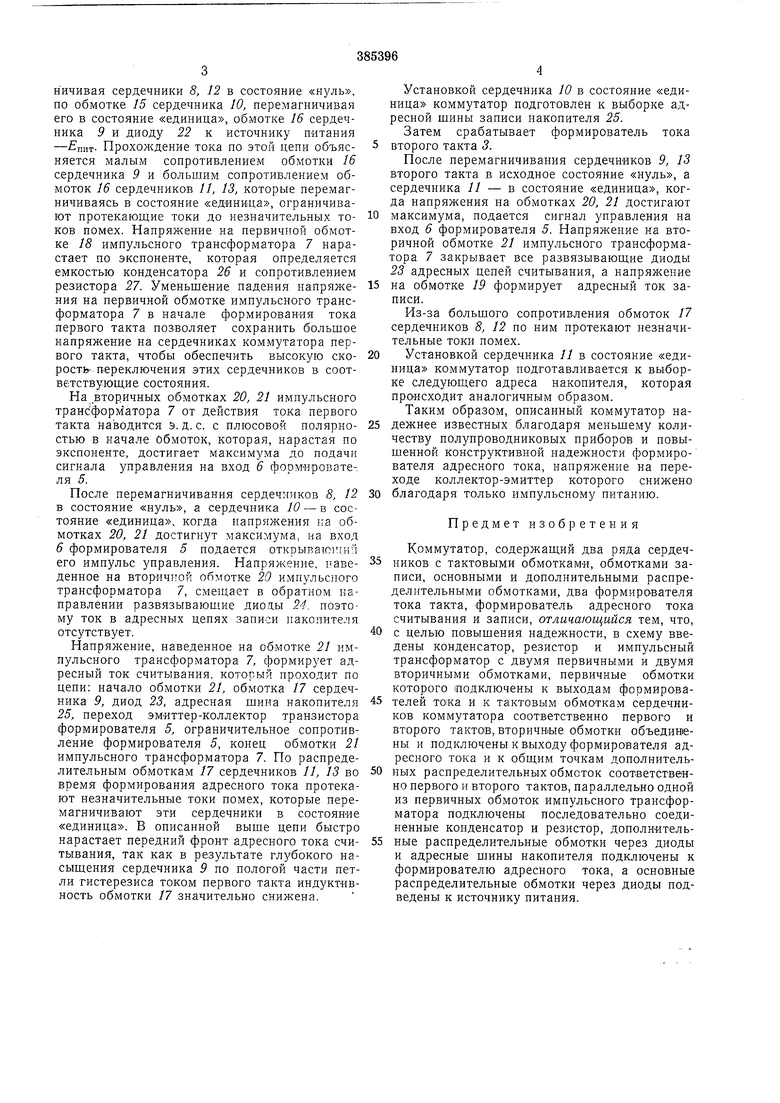

На чертеже представлена прицнипиальная схема устройства.

Коммутатор содержит формирователь тока первого такта / со входом 2, формирователь

тока второго такта 3 со входом 4, формирователь адресного тока считывания и записи 5 со входом 6, импульсный трансформатор 7, сердечники 8-13 с прямоугольной петлей гистерезиса первого и второго тактов, тактовые

обмотки 14, обмотки записи 15, основные распределительные обмотки 16, дополнительные распределительные обмотки /7, первичные обмотки 18, 19 и вторичные обмотки 20, 21 импульсного трасформатора 7, развязывающие

диоды тактовых и адресных цепей считывания и записи соответственно, накопитель 25, конденсатор 26 и регистр 27.

Перед началом работы по общей обмотке первоначальной установки сердечников коммутатора (на чертеже не показана) пропускается импульс тока, устанавливающий, например, сердечник 9 в состояние «единица, а остальные сердечники 8, 10-13 в состояние «нуль. Условимся, что ток, входящий в начало обмотки, отмеченной на чертеже точкой, устанавливает сердечник в состояние «нуль. Когда на вход 2 поступает сигнал управления, срабатывает формирователь 1, импульс тока которого проходит по первичной обмотке 18 импульсного трансформатора 7, тактовой обмотке 14 сердечников 8, 10, 12, перемагничивая сердечники 8, 12 в состояние «нуль, по обмотке 15 сердечника 10, неремагничивая его в состояние «единица, обмотке 16 сердечника 9 и диоду 22 к источнику питания Прохоладение тока по этой цепи объясняется малым сопротивлением обмотки 16 сердечника 9 и большим сопротивлением обмоток 16 сердечников 11, 13, которые перемагничиваясь в состояние «единица, ограничивают протекающие токи до незначительных токов помех. Напряжение на первичной обмотке 18 импульсного трансформатора 7 нарастает по экспоненте, которая определяется емкостью конденсатора 26 и сопротивлением резистора 27. Уменьшение падения напряжения на первичной обмотке импульсного трансформатора 7 в начале формирования тока первого такта позволяет сохранить больщое напряжение на сердечниках коммутатора первого такта, чтобы обеспечить высокую скорость-переключения этих сердечников в соответствующие состояния. На вторичных обмотках 20, 21 импульсного трансформатора 7 от действия тока первого такта наводится э. д. с. с плюсовой полярностью в начале обмоток, которая, нарастая по экспоненте, достигает максимума до подачи сигнала управления на вход 6 формироватеПосле перемагничивания сердечников 3, 12 в состояние «нуль, а сердечника 10 - в состояние «единица, когда напряжения i;a обмотках 20, 21 достигнут максимума, на вход 6 формирователя 5 подается открываю } ; его импульс управления. Напряжение, ваведенное на вторичной обмотке 20 импульсного трансформатора 7, в обратном направлении развязывающие диоды 24. поэтому ток в адресных цепях записи накопителя отсутствует. Напряжение, наведенное на обмотке 21 импульсного трансформатора 7, формирует адресный ток считывания, который проходит по цепи: начало обмотки 21, обмотка 17 сердечника 9, диод 23, адресная шина накопителя 25, переход эмиттер-коллектор транзистора формирователя 5, ограничительное сопротивление формирователя 5, коиец обмотки 21 импульсного трансформатора 7. По распределительным обмоткам 17 сердечников 11, 13 во время формирования адресного тока протекают незначительные токи помех, которые перемагничивают эти сердечники в состояние «единица. В описанной выще цепи быстро нарастает передний фронт адресного тока считывания, так как в результате глубокого насыщеиия сердечника 9 по пологой части петли гистерезиса током первого такта индуктивность обмотки 17 значительно снижена. Установкой сердечника 10 в состояние «единица коммутатор подготовлен к выборке адресной шины записи накопителя 25. Затем срабатывает формирователь тока второго такта 3. После перемагничивания сердечников 9, 13 второго такта в исходное состояние «нуль, а сердечника 11 - в состояние «единица, когда напряжения иа обмотках 20, 21 достигают максимума, подается сигнал управления на вход 6 формирователя 5. Напряжение на вторичной обмотке 21 импульсного трансформаора 7 закрывает все развязывающие диоды 23 адресных цепей считывания, а напряжение на обмотке 19 формирует адресный ток записи. Из-за большого сопротивления обмоток 17 сердечников 8, 12 по ним протекают незначительные токи помех. Установкой сердечника 11 в состояние «единица коммутатор подготавливается к выборке следующего адреса накопителя, которая происходит аналогичным образом. Таким образом, описанный коммутатор надежнее известных благодаря меньщему количеству полупроводниковых приборов и повышенной конструктивной надежности формирователя адресного тока, напряжение на переходе коллектор-эмиттер которого снижено благодаря только импульсному питанию, Предмет изобретения Коммутатор, содержащий два ряда сердечников с тактовыми обмотками, обмотками записи, основными и дополнительными распределительными обмотками, два формирователя тока такта, формирователь адресного тока считывания и записи, отличающийся тем, что, с целью повышения надежности, в схему введены конденсатор, резистор и импульсный трансформатор с двумя первичными и двумя вторичными обмотками, первичные обмотки которого оодключены к выходам формирователей тока и к тактовым обмоткам сердечников коммутатора соответственно первого и второго тактов, вторичные обмотки объединены и подключены к выходу формирователя адресного тока и к общим точкам дополнительных распределительных обмоток соответственно первого и второго тактов, параллельно одной из первичных обмоток импульсного трансформатора подключены последовательно соединенные конденсатор и резистор, дополнительные распределительные обмотки через диоды и адресные шины накопителя подключены к формирователю адресного тока, а основные распределительные обмотки через диоды подведены к источнику питания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ЗАПОМИНАЮЩИЛ1 БЛОКОМ | 1971 |

|

SU318991A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЗАПОМИНАЮЩИМ БЛОКОМ | 1973 |

|

SU386441A1 |

| УСТРОЙСТВО для УПРАВЛЕНИЯ ЗАПОЛ\ИНАЮЩИМБЛОКОМ | 1970 |

|

SU272372A1 |

| МАТРИЧНОЕ ФЕРРИТ-ДИОДНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU395899A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ НАКОПИТЕЛЕМ | 1972 |

|

SU433540A1 |

| ВЫЧИСЛИТЕЛЬНО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU393741A1 |

| Запоминающее устройство | 1980 |

|

SU940235A1 |

| ПРОГРАММНОЕ УСТРОЙСТВО | 1972 |

|

SU338890A1 |

| Устройство для управления накопителем | 1979 |

|

SU773737A1 |

| ИМПУЛЬСНЫЙ ТВЕРДОТЕЛЬНЫЙ МОДУЛЯТОР | 2010 |

|

RU2408135C1 |

Даты

1973-01-01—Публикация