1

Изобретение относится к области автоматики и телеметрических измерений и предназначено для выделения заданного импульса из, кодовой последовательности импульсов, имеющих заданную скважность.

Известны дешифраторы кодовых импульсных последовательностей, выпол-ненные на элементах задержки (выполняющих в том числе функции распределителя) и схемах совпадения.

Предложенное устройство отличается тем, что выходы диодной матрицы через первую схему сборки соединены с прямым входом второго элемента запрета, выход которого соединен со входом второй схемы сборки, выходы элементов задержки соединены с управляющими входами диодной матрицы, выход схемы совпадения соедиден со входом второй схемы сборки, выход которой соединен со сбросовым входом счетчика.

Это позволяет повысить номехоустойчивость дещифрирования импульсных последовательностей.

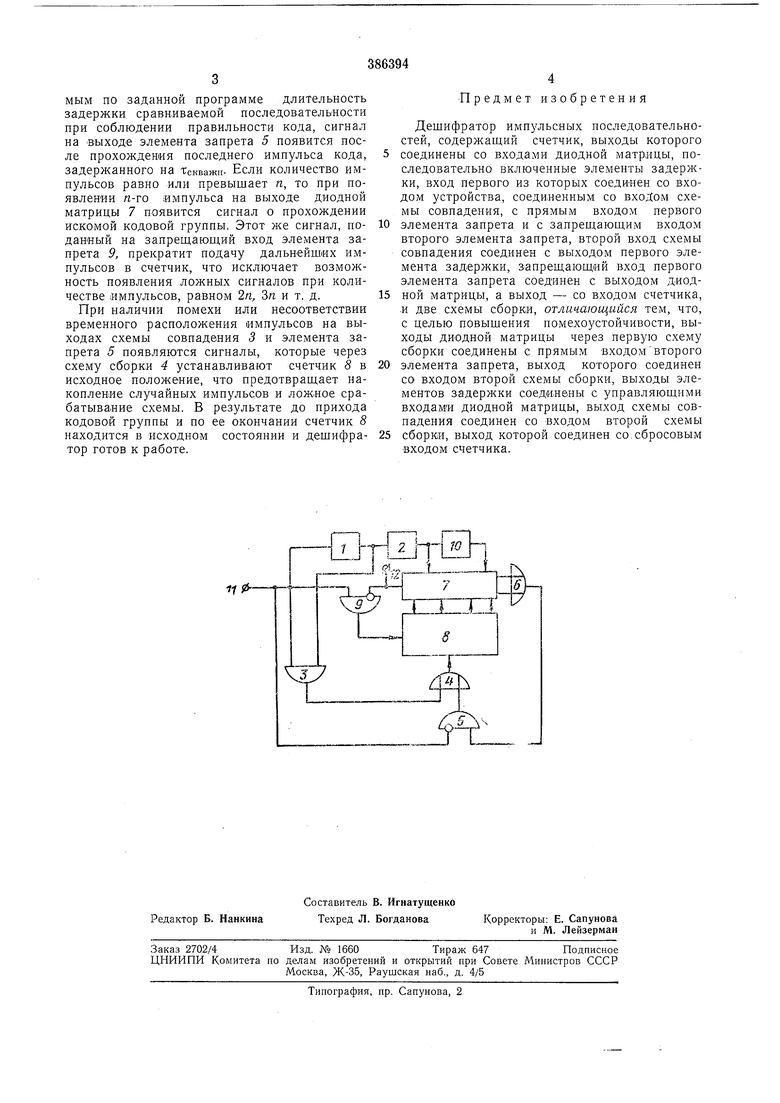

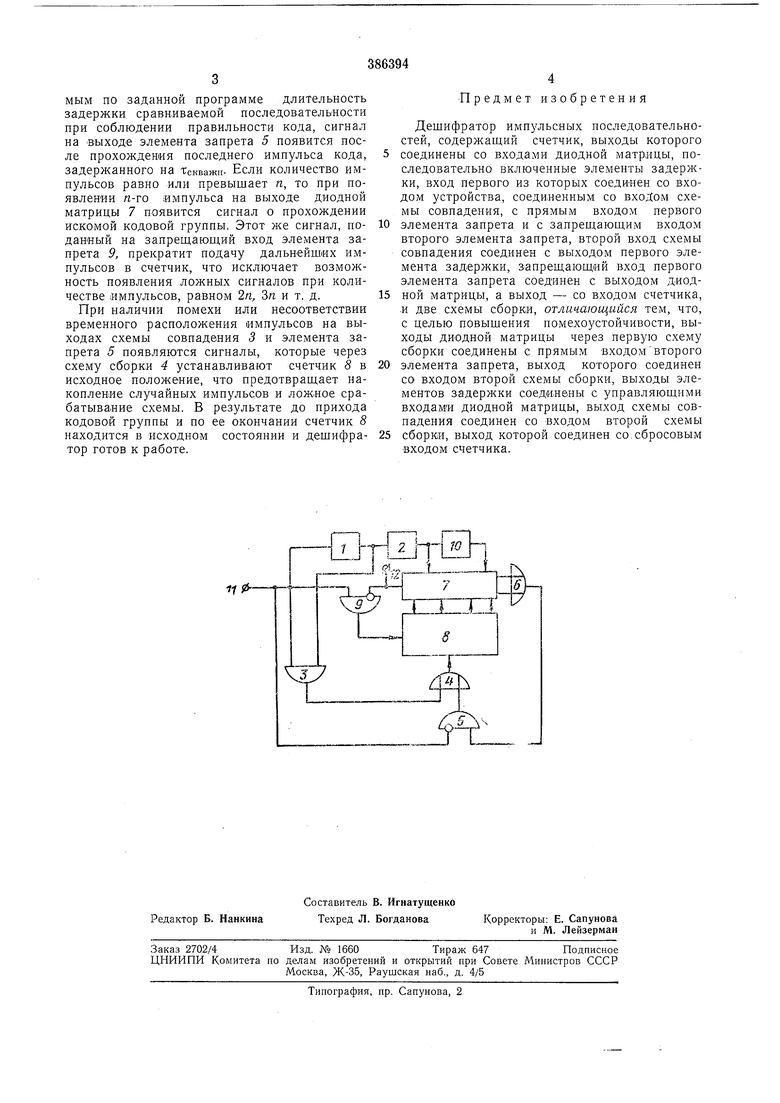

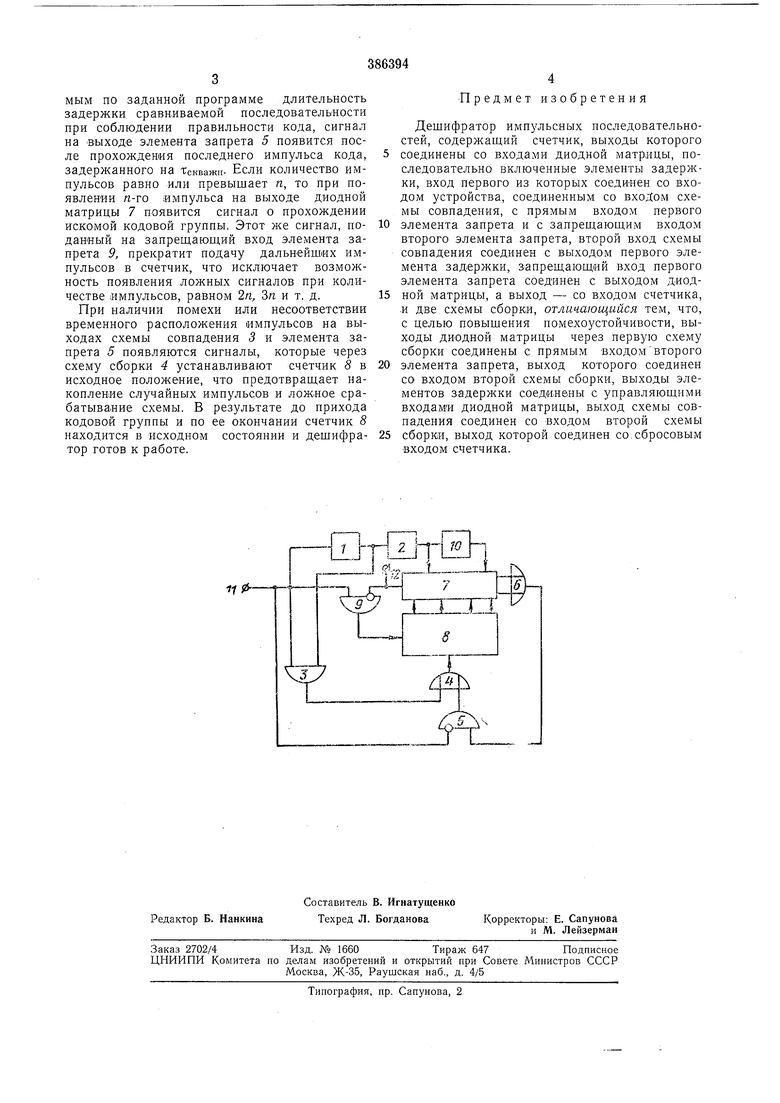

Схема устройства изображена на чертеже. Устройство содержит элемент задержки / ча время .мп, элемент задержки 2 на время Т2 Тскпаж(г, схему совнадения 3, схему сборки 4, элемент запрета 5, схему сборки 6, диодную матрицу 7, счетчик 8, элемент запрета 9, элемент задержки 10, вход 11 и выход 2.

Устройство работает следующим образом.

Перед приходом очередной импульсной последовательности (кодовой группы) счетчик 8 установлен в «О сигналом окончания предыдущей группы, элемент запрета 9 открыт по прямому входу, на выходе схемы сборки 6 сигнал отсутствует.

При поступлении на вход 11 кодовой группы происходят следующие операции: импульсы кодовой последовательности проходят через элемент запрета 9 в счетчик 8 и записывают в нем задними фронтами число прошедших импульсов. В то же время схема совпадения 5 сравнивает прямую последовательность импульсов с задержанной на Т| Гимп. Если импульсы по длительности не превышают заданной и следуют со скважностью, не меньшей заданной, то на выходе схемы совнадения 5 сигнал не возникает. Элемент запрета 5 сравнивает обратную последовательность с последовательностью, задержанной на величину, равную периоду следования импульсов, причем для дешифровки неравномерного кода, по мере записи числа импульсов счетчик 8 переключает строчки диодной мат рицы 7, подключенные к схеме сборки 6 и элементам задержки 2 и 10, изменяя тем самым по заданной программе длительность задержки сравн.иваемой последовательности при соблюдении правильности кода, сигнал на выходе элемента запрета 5 появится после прохождения последнего импульса кода, задержанного на Тскважп- Если количество импульсов равно или превышает п, то при появлении п-го импульса на выходе диодной матрицы 7 появится сигнал о прохождении искомой кодовой группы. Этот же сигнал, поданный на запрещающий вход элемента запрета 9, прекратит подачу дальнейших импульсов в счетчик, что исключает возможность появления ложных сигналов при количестве импульсов, равном 2п, Зп и т. д.

При наличии помехи или несоответствии временного расположения импульсов на выходах схемы совпадения 3 и элемента запрета 5 появляются сигналы, которые через схему сборки 4 устанавливают счетчик 8 в исходное положение, что предотвращает накопление случайных импульсов и лож.ное срабатывание схемы. В результате до прихода кодовой группы и по ее окончании счетчик 8 находится в исходном состоянии и дешифратор готов к работе.

Предмет изобретения

Дешифратор импульсных последовательностей, содержащий счетчик, выходы которого

соединены со входами диодной матрицы, последовательно включенные элементы задержки, вход первого из которых соединен со входом устройства, соединенным со входом схемы совпадения, с прямым входом первого

элемента запрета и с запрещающим входом второго элемента запрета, второй вход схемы совпадения соединен с выходом первого элемента задержки, запрещающий вход первого элемента запрета соединен с выходом диодной матрицы, а выход - со входом счетчика, и две схемы сборки, отличающийся тем, что, с целью повышения помехоустойчивости, выходы диодной матрицы через первую схему сборки соединены с прямым входомвторого

элемента запрета, выход которого соединен со входом второй схемы сборки, выходы элементов задержки соединены с управляющими входами диодной матрицы, выход схемы совпадения соединен со входом второй схемы

сборки, выход которой соединен со.сбросовым входом счетчика.

Г

..J ;.,1L, Г

L-j, VI SЛ

Авторы

Даты

1973-01-01—Публикация