Изобретение относится к области электроизмерительной техники, автоматики и телемеханики и может быть использовано в качестве устройства, совмещающего в себе функции регистра памяти и распределителя импульсов в цифровых автоматических приборах и кодирующих преобразователях, работающих по методу поразрядного взвещивания.

В известпых цифровых автоматических приборах и кодирующих преобразователях распределение импульсов и промежуточное запоминание осуществляются двумя самостоятельными однофункциональными устройствами - распределителем импульсов и регистром. Распределители импульсов выполняются обычно на основе различных схем счетчиков или на основе комбинации счетчиков и дещифраторов.

При реализации последнего варианта заметно сокращается число разрядов счетчика, а следовательно, и число активных элементов (транзисторов), упрощается схема и повыщается надежность расиределительного устройства.

Дальнейшим щагом к упрощению распределительного устройства и частичной передаче его функции распределения импульсов регистру является изобретение по авт. св. № 216130.

В этом изобретенпп распределитель импульсов имеет число разрядов (триггеров), равное числу декад регистра и осуществляет подекадное распределение импульсов, внутрпдекадпое же распределение импульсов выполняется регистром, что значительно упрощает распределительное устройство. Кроме того, в этом изобретении сделана попытка npeBpanteния регистра в многофункциональное устройство, осуществляющее, кроме промежуточного запоминания, также частичное распределение импульсов. Но поскольку регистр выполняет лищь частичное распределенпе импульсов (внутри декады), то он не является полностью

5 независимым устройством и его функционирование невозможно без распределителя, хотя и упрощенного. Наличие же в приборе пли в кодирующем преобразователе двух устройств - распределителя импульсов и регистра - приводит к значительным схемным усложнениям п детальной избыточности. Наличие же активных элементов (транзисторов) в распределптеле импульсов снижает его надежность и помехоустойчпвость, а следова5 тельно, п всего прибора в целом.

Целью изобретения является унрощение устройства (устранение распределителя) и повыщение его надежности. Эта цель достигается соответствующим

костных ключей) и введением в регистр диодных схем «ИЛИ. Один из двух иотепциальных входов схемы совпадеиия, отиосящейся к единичному входу каждого триггера, кроме первого, через разделительный диод иодсоедннен к диодной схеме «ИЛИ, один из входов которой соединяется с единичным выходом данного триггера, а второй - с выходом диодной схемы «ИЛИ последующего триггера. Другой потенциальный вход схемы Совпадения, стоящей на единичном входе каждого триггера, соединен с нулевым выходом предыдущего триггера, а импульсный вход - с шиной тактовых импульсов.

Цеиочка, сформированная последовательным соединением диодных схем «ИЛИ, может: служить одновременно цепью сброса триггеров регистра в исходное состояние.

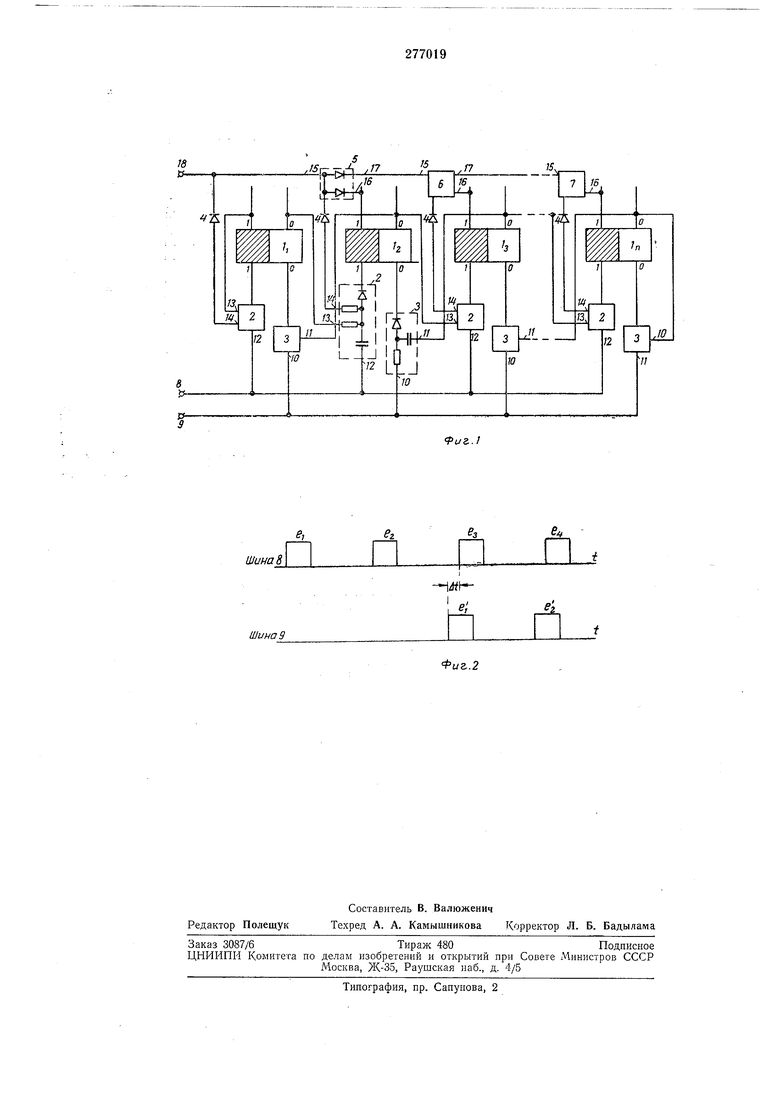

Иа фиг. 1 приведена блок-схема одной декады регистра; па фиг. 2 - временная днаг. рамма импульсов на щпне тактовых имиульсов и перекомпенсации.

- Описываемый регистр может состоять из ,п-го числа триггеров (в данном случае п 4, что составляет декаду регистра) и включает в себя триггеры 1... 1„ со схемами совпадения 2 на их единичных входах «1 и схемами совпадения 8 на нулевых входах «О, разделительные диоды 4, диодные схемы 5 и 7 «ИЛИ, шины 8 тактовых импульсов п шины 9 перекомпенсации.

Потенциальиые входы 10 схем совнаденпя 5 триггеров /1... 7з и импульсный вход 11 схемы 3 совпадения триггера /„ подсоединены к шипе 9 перекомиенсадпп. Импульсный вход// схем совпадения 3 нодключен к выходу «О того триггера, который следует за триггером, имеющим данную схему совнадения на его входе «О. Такое включение схем 3 совпадения обеспечивает сброс предыдущего триггера после срабатывания последующего при наличии разрешающего потенциала па щппе 9 перекомиенсацпп. Потенциальный вход 10 схемы 5 совпадения триггера /„ соединен с выходом «О своего триггера.

Схемы 2 совпадения, отосящиеся к входам «1 триггеров, своими импульсными входами 12 подсоединены к щине 8 тактовых имиульсов. Потенциальный вход 13 схем 2 совпадения соединен с выходом «О того триггера, который предществует триггеру, имеющему данную схему совнадения на его входе «1, а потепцпальный вход 13 схемы 2 совпадения триггера Л нодсоединен к выходу «1 своего триггера. Другой потенциальиый вход 14 схемы 2 совпадения триггеров /з / л через разделительный диод 4 соединен с выходом 15 соответствующей диодной схемы 5, 6 и 7 «Р1ЛИ, один из входов которой соединен с выходом «1 триггера, имеющего на своем входе «Ь данную схему 2 совпадения, а другой вход соединен с выходом 15 диодной схемы «ИЛИ, относящейся к последующему триггеру.

Исключеиие составляет потенциальный вход 14 схемы 2 совпадеппя триггера /ь который через 4 соедипеп с выходом 15 дподпой схемы 5 «ИЛИ триггера /9. Разделительный диод 4 препятствует появлению отрицательного потенциала с выхода «О предшествующего триггера (связь через элементы схемы 2 совнадения) на выходе 15 диодной схемы «ИЛРЬ, относящейся к последующему триггеру.

Один пз входов 16 диодных схем 5-7 «ИЛИ соединен с выходом «1 соответствующего триггера /2.-/з и /„, а другой вход/7 каждой диодной схемы «ИЛИ - с выходом 15 иоследующей диодной схемы «ИЛИ. В результате образуется цепь последовательно соедииенных диодных схем «ИЛИ. Эта цепь обеспечивает иодачу запрещенного отрпцательного потенциала с выхода «I каждого

последующего триггера, после его опрокидывания, на потепцпальный вход 14 схемы 2 совпадения этого триггера п схем 2 совпадения предыдущих триггеров, которые были сброшены в исходное состояние (дважды оирокипуты). Кроме того, цепь диодных схем 5- 7 «ИЛИ прп подключении в клемме 18 пулевого потенциала может пграть роль цепи сброса триггеров в исходное положение. Предлагаемый регистр работает следующим образом.

В исходном положенпп все триггеры li... 1„ находятся в таком состоянии, что на их выходе «О находится отрицательный потенциал. Этот занрещающий потенциал с выхода «О

каждого предыдущего триггера подается на потенциальный вход 13 схемы 2 совпадения последующего триггера. На потепциальпый же вход 13 схемы 2 совпадения триггера /i заводится нулевой (разрешающий) потенциал

с выхода «1 своего триггера. На другом потенциальном входе 14 схем 2 совпадения также находится разрещающий потенциал.

Предположим, что регистр должен запомнить величину, равную пяти условным единицам (у. е.), набранную по двоичпо-десятичному коду 4221.

Первый имиульс на щине 8 тактовых импульсов (па фиг. 2 он условно обозначен е) поступает на вход 12 схемы 2 совпадения

триггера /i, дифференцируется и опрокидывает триггер. Поскольку включеппе триггера /1 соответствует запоминанию «4, то на шине 9 нерекомпенсации не появляется разрешающий потенциал п триггер /i остается включенным. С выхода «1 триггера /i на вход 13 его схемы 2 совпадения нодается запрещающпй потепциал, а с выхода «О на потенциальный вход 13 схемы совпадения последующего триггера /2 - разрешающей иотенциал. В результате вторым импульсом на шине 8 ((2 на фиг. 2) триггер /2 будет опрокинут и с его выхода «1 через вход 16 диодпой схемы 5 «ИЛИ и разделительпый диод 4 будет подан запрещающий потенциал на вход 14 разрешающий потенциал на вход 13 схемы 2 совпадения триггера /зВключение триггера 1 соответствует запоминанию двух у. е., а суммариый результат иосле включения триггеров 1 и /а составит 4 + 2 6 у. е., что иревышает заданную величину в пять у. е. и указывает на необходимость возврата триггера /а в исходное положение. Для этого на шипу 9 перекомиенсации подается положительный пмпульс (е па фиг. 2), который попадает на потенциальный вход 10 схем 3 совпадения и подготавливает триггер /2 к иовторпому срабатыванню. Это нроисходит в момент включения триггера /и от импульса (е на фиг. 2), который сдвинут на время А относительно е/, благодаря воздействию с его выхода «О положительного перепада напряжения на импульсный вход 11 схемы 3 совнадепия триггера Iz- После включения триггера /з с его выхода «1 подается запрещающий потенциал на вход 14 его схемы 2 совпадения через вход 16 диодиой схемы 6 «ИЛИ и разделительный диод 4, и па вход 14 схемы 2 совпадения триггера /а - через вход 16 диодиой схемы 6 «ИЛИ, выход 15 которой соединен со входом 17 предыдущей диодной схемы 5 «ИЛИ, и разделительный диод 4. Срабатывание триггера 1, так же как и триггера h, соответствует заноминапию двух у. е., следовательпо, он должен быть возвращен в исходное состояние. Это произойдет в момеит оирокидывания последующего триггера /„ от воздействия положительного импульса (ei на фиг. 2) с шины 8 тактовых импульсов. Предварительно на шине 9 с оиереженнем на время М появляется импульс , что подготавливает повторное срабатывание триггера /3. После опрокидр шания триггера 1 „ сего выхода «1, заирещающий потенциал поступает на вход 14 его схемы 2 совпадения через диодную схему «ИЛИ 7 и диод 4, и на вход 14 схем совпадения 2 триггеров УЗ и /а соответственно через диодные схемы 7 и 6 «ИЛИ и разделительный диод 4 и диодные схемы «ИЛИ 5-7 и диод 4. Кроме того, носле срабатывания триггера/„ накладывается запрет па поступление положительных импульсов на шину 8. Запрет накладывается с помощью вспомогательного триггера (не ноказан), который срабатывает под воздействием положительного перепада иапряжения, снимаемого с выхода «О триггера /„. Триггер /„, включение которого соответствует запомннанпю одной у. е., не возвращается в нсходное состояние (на щине 9 не появляется полол ительный импульс), поскольку включением триггеров /„ м 1 выполпеио условие заиомипаппя пяти у. е. но коду 4221. При запоминании четырех у. е. триггер /„ возвратился бы в исходное состоянне под воздействием положительного имнульса с щины 9 па импульсный вход 11 его схемы 3 совпадения, на потенцпальном входе 10 которого присутствует разрешающий потенциал. Триггеры регистра прпводятся в исходное положение путем подачи имнульса сброса на клемму 18, который через цепочку диодных схем 5-7 «МЛИ воздействует на выход «1 триггеров /г, /з и /„. Триггер 1 сбрасывается обычным способом. Предмет изобретения Регистр цифрового автоматического прибора с поразрядным взвешиванием, выполиеипый на п трпггерах со схемами совпадения на их входах и и.меющий шииы тактовых импульсов и перекомпенсации, отличающийся тем, что, с целью упрощеиия устройства и новышения его надежности, он содержит (я-1) диодиых схем «ИЛИ, прпчем один из двух потеициальпых входов схемы совпадения, относящийся к единичному входу каждого триггера, кроме первого, через разделительный диод соединен с выходом диодиой схемы «ИЛИ, один вход которой соединен с единичиым выходом данного триггера, другой - с выходом диодной схемы «ИЛИ, относящейся к последующему трнггеру, другой нотенциальпый вход схемы совиадения соединен с нулевым выходом предыдущего триггера, а ее импульсный вход - с щиной тактовых импульсов.

- 1/«К

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1967 |

|

SU216130A1 |

| ЦИФРОВОЙ ВОЛЬТМЕТР | 1970 |

|

SU288138A1 |

| Распределитель на транзисторах | 1973 |

|

SU504302A1 |

| РАСПРЕДЕЛИТЕЛЬ—СЧЕТЧИК | 1972 |

|

SU332577A1 |

| Устройство для деления чисел,представленных в число-импульсной форме | 1973 |

|

SU474005A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1969 |

|

SU241123A1 |

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ ЧИСЕЛ В КОДЕ С ПОСТОЯННЫМ ЧИСЛОМ «ЕДИНИЦ» | 1969 |

|

SU241110A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОГО КОДА В УНИТАРНЫЙ КОД | 1971 |

|

SU432487A1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА | 1973 |

|

SU389548A1 |

Даты

1970-01-01—Публикация