S

(Л

й

о

ел

оо ел

Изобретение относится к импульсной технике и может быть использовано при построении автономных формирователей больших временных интервалов в вычислительных устройствах, работаюплих в реальном масштабе времени.

Цель изобретения - повышение точности формирования интервалов времени.

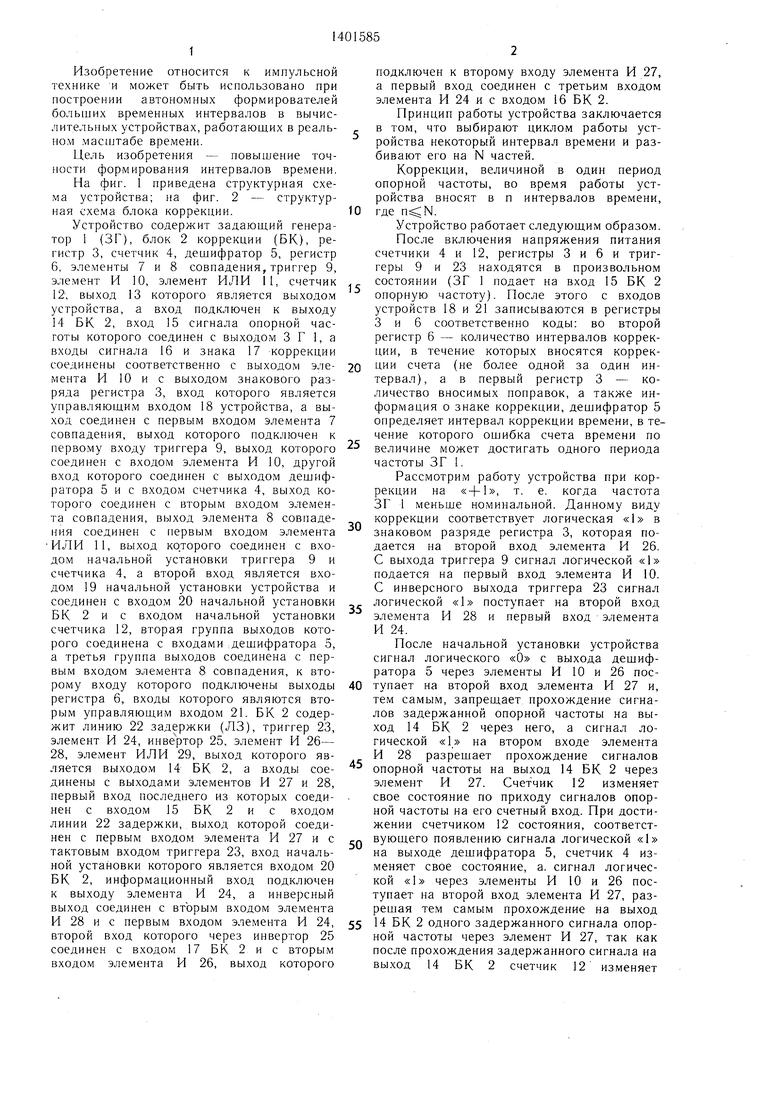

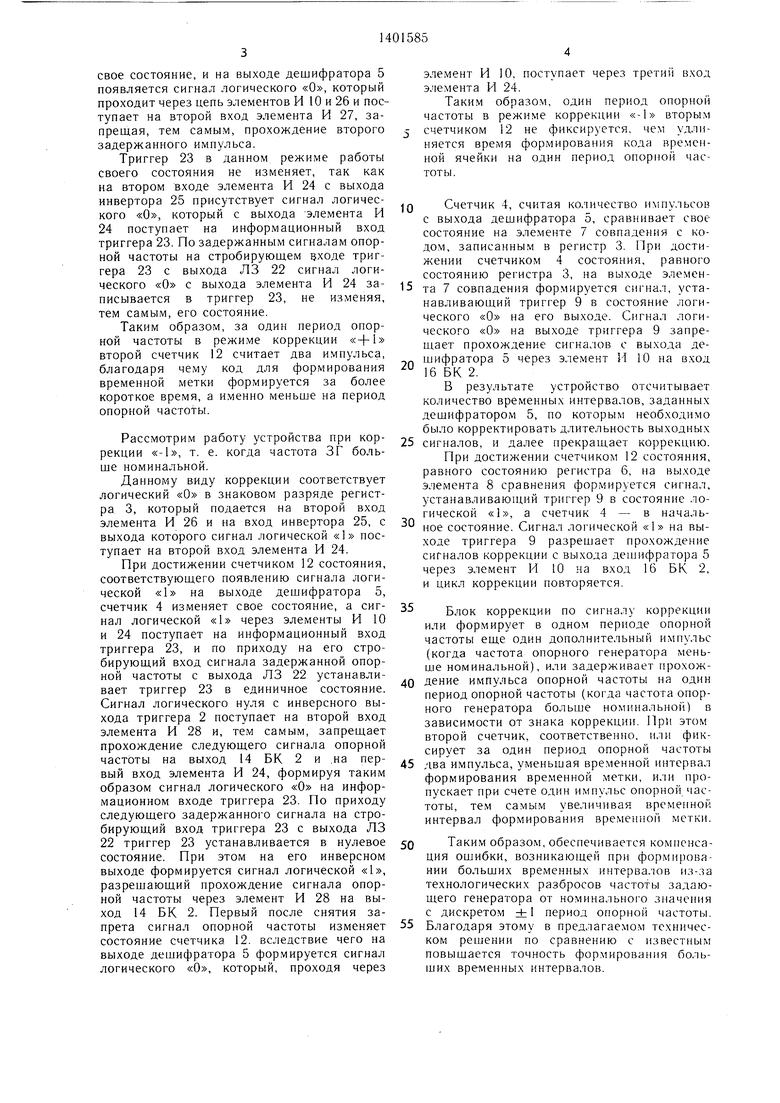

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - структурная схема блока коррекции.

Устройство содержит задаюш.ий генератор 1 (ЗГ), блок 2 коррекции (БК), регистр 3, счетчик 4, дешифратор 5, регистр 6, элементы 7 и 8 совпадения, триггер 9, элемент И 10, элемент ИЛИ 11, счетчик 12, выход 13 которого является выходом устройства, а вход подключен к выходу 14 БК 2, вход 15 сигнала опорной час- готы которого соединен с выходом 3 Г 1, а входы сигнала 16 и знака 17 коррекции соединены соответственно с выходом эле- мента И 10 и с выходом знакового разряда регистра 3, вход которого является управляющим входом 18 устройства, а выход соединен с первым входом элемента 7 совпадения, выход которого подключен к первому входу триггера 9, выход которого соединен с входом элемента И 10, другой вход которого соединен с выходом дешифратора 5 и с входом счетчика 4, выход которого соединен с вторым входом элемента совпадения, выход элемента 8 совпадения соединен с первым входом элемента ИЛИ 11, выход которого соединен с входом начальной установки триггера 9 и счетчика 4, а второй вход является входом 19 начальной установки устройства и соединен с входом 20 начальной установки БК 2 и с входом начальной установки счетчика 12, вторая группа выходов которого соединена с входами ;Дешифратора 5, а третья группа выходов соединена с первым входом элемента 8 совпадения, к второму входу которого подключены выходы регистра 6, входы которого являются вторым управляющим входом 21. БК 2 содержит линию 22 задержки (ЛЗ), триггер 23, элемент И 24, инве ртор 25, элемент И 26- 28, элемент ИЛИ 29, выход которого является выходом 14 БК 2, а входы сое- лТинены с выхода.ми элементов И 27 к 28, первый вход последнего из которых соединен с входом 15 БК 2 и с входом линии 22 задержки, выход которой соединен с первым входом элемента И 27 и с тактовым входом триггера 23, вход начальной установки которого является входом 20 БК 2, информационный вход подключен к выходу элемента И 24, а инверсный выход соединен с вторым входом элемента И 28 и с первым входом элемента И 24, второй вход которого через инвертор 25 соединен с входом 17 БК 2 и с вторым входом элемента И 26, выход которого

5

5

0

0 0 5

0

5

5

0

подключен к второму входу элемента И 27, а первый вход соединен с третьим входом элемента И 24 и с входом 16 БК 2.

Принцип работы устройства заключается в том, что выбирают циклом работы устройства некоторый интервал времени и разбивают его на N частей.

Коррекции, величиной в один период опорной частоты, во время работы устройства вносят в п интервалов времени, где .

Устройство работает следующим образо.м.

После включения напряжения питания счетчики 4 и 12, регистры 3 и 6 и триггеры 9 и 23 находятся в произвольном состоянии (ЗГ 1 подает на вход 15 БК 2 опорную частоту). После этого с входов устройств 18 и 21 записываются в регистры 3 и 6 соответственно коды: во второй регистр 6 - количество интервалов коррекции, в течение которых вносятся коррекции счета (не более одной за один интервал), а в первый регистр 3 - количество вносимых поправок, а также информация о знаке коррекции, дешифратор 5 определяет интервал коррекции времени, в течение которого ошибка счета времени по величине может достигать одного периода частоты ЗГ 1.

Рассмотрим работу устройства при коррекции на «-|-1, т. е. когда частота ЗГ 1 меньше номинальной. Данному виду коррекции соответствует логическая «1 в знаковом разряде регистра 3, которая подается на второй вход элемента И 26. С выхода триггера 9 сигнал логической «1 подается на первый вход элемента И 10. С инверсного выхода триггера 23 сигнал логической «1 поступает на второй вход элемента И 28 и первый вход элемента И 24.

После начальной установки устройства сигнал логического «О с выхода дешифратора 5 через элементы И 10 и 26 поступает на второй вход элемента И 27 и, тем самым, запрещает прохождение сигналов задержанной опорной частоты на выход 14 БК 2 через него, а сигнал логической «1 на втором входе элемента И 28 разрешает прохождение сигналов опорной частоты на выход 14 БК 2 через элемент И 27. Счетчик 12 изменяет свое состояние по приходу сигналов опорной частоты на его счетный вход. При достижении счетчиком 12 состояния, соответствующего появлению сигнала логической «1 на выходе дешифратора 5, счетчик 4 изменяет свое состояние, а. сигнал логической «1 через элементы И 10 и 26 поступает на второй вход элемента И 27, разрешая тем самым прохождение на выход 14 БК 2 одного задержанного сигнала опорной частоты через элемент И 27, так как после прохождения задержанного сигнала на выход 14 БК 2 счетчик 12 изменяет

свое состояние, и на выходе дешифратора 5 появляется сигнал логического «О, который проходит через цепь элементов И 10 и 26 и поступает на второй вход элемента И 27, запрещая, тем самым, прохождение второго задержанного импульса.

Триггер 23 в данном режиме работы своего состояния не изменяет, так как на втором входе элемента И 24 с выхода инвертора 25 присутствует сигнал логического «О, который с выхода элемента И 24 поступает на информационный вход триггера 23. По задержанным сигналам опорной частоты на стробирующем дходе триггера 23 с выхода ЛЗ 22 сигнал логического «О с выхода элемента И 24 записывается в триггер 23, не изменяя, тем самым, его состояние.

Таким образом, за один период опорной частоты в режиме коррекции «-(-1 второй счетчик 12 считает два импульса, благодаря чему код для формирования временной метки формируется за более короткое время, а именно меньше на период опорной частоты.

Рассмотрим работу устройства при коррекции «-1, т. е. когда частота ЗГ больше номинальной.

Данному виду коррекции соответствует логический «О в знаковом разряде регистра 3, который подается на второй вход элемента И 26 и на вход инвертора 25, с выхода которого сигнал логической «1 поступает на второй вход элемента И 24.

При достижении счетчиком 12 состояния, соответствуюшего появлению сигнала логической «1 на выходе дешифратора 5, счетчик 4 изменяет свое состояние, а сигнал логической «1 через элементы И 10 и 24 поступает на информационный вход триггера 23, и по приходу на его стро- бируюш,ий вход сигнала задержанной опорной частоты с выхода ЛЗ 22 устанавливает триггер 23 в единичное состояние. Сигнал логического нуля с инверсного выхода триггера 2 поступает на второй вход элемента И 28 и, тем самым, запрещает прохождение следующего сигнала опорной частоты на выход 14 БК 2 и .на первый вход элемента И 24, формируя таким образом сигнал логического «О на информационном входе триггера 23. По приходу следующего задержанного сигнала на стро- бирующий вход триггера 23 с выхода ЛЗ 22 триггер 23 устанавливается в нулевое состояние. При этом на его инверсном выходе формируется сигнал логической «1, разрешающий прохождение сигнала опорной частоты через элемент И 28 на выход 14 БК 2. Первый после снятия запрета сигнал опорной частоты изменяет состояние счетчика 12. вследствие чего на выходе дешифратора 5 формируется сигнал логического «О, который, проходя через

элемент И 10, поступает через третий вход элемента И 24.

Таким образом, один период опорной частоты в режиме коррекции «-1 вторым 5 счетчиком 12 не фиксируется, чем удлиняется время формирования кода временной ячейки на один период опорной частоты.

0 Счетчик 4, считая количество импульсов с выхода дешифратора 5, сравнивает свое состояние на элементе 7 совпадения с кодом, записанным в регистр 3. При достижении счетчиком 4 состояния, равного состоянию регистра 3, на выходе элемен5 та 7 совпадения формируется си1 нал, уста- навливаюший триггер 9 в состояние логического «О на его выходе. Сигнал логического «О на выходе триггера 9 запрещает прохождение сигналов с выхода де„ шифратора 5 через элемент И 10 на вход

16 БК 2.

В результате устройство отсчитывает количество временных интервалов, заданных дешифратором 5, по которым необходимо было корректировать длительность выходных

5 сигналов, и далее прекращает коррекцию. При достижении счетчиком 12 состояния, равного состоянию регистра 6, на выходе элемента 8 сравнения формируется сигнал, устанавливающий триггер 9 в состояние логической «1, а счетчик 4 - в началь- ное состояние. Сигнал логической «1 на выходе триггера 9 разрешает про.хождение сигналов коррекции с выхода дешифратора 5 через элемент И 10 на вход 16 БК 2, и цикл коррекции повторяется.

5 Блок коррекции по сигналу коррекции или формирует в одном периоде опорной частоты еще один дополнительный импульс (когда частота опорного генератора меньше номинальной), или задерживает прохож0 дение импульса опорной частоты на один период опорной частоты (когда частота опорного генератора больше номинальной) в зависимости от знака коррекции. При этом второй счетчик, соответственно, или фиксирует за один период опорной частоты

5 два импульса, уменьшая временной интервал формирования временной метки, или пропускает при счете один импульс опорной частоты, тем самым увеличивая временной интервал формирования временной метки.

0 Таким образом, обеспечивается компенсация ошибки, возникающей при формировании больщих временных интервалов из-за технологических разбросов частоты задающего генератора от номинального значения с дискретом ±1 период опорной частоты.

5 Благодаря этому в предлагаемом техническом решении по сравнению с известным повышается точность формирования больших временных интервалов.

Формула изобретения

1. Устройство формирования временных интервалов, содержащее задающий генератор, первый счетчик, первый блок совпаде- ния, триггер, первый регистр, вход которого является первым управляющим входом устройства, отличающееся тем, что, с целью повыщения точности формирования интервалов времени, в него введены блок коррекции, второй регистр, дещифратор, второй блок совпадения, элемент ИЛИ, элемент И, второй счетчик, первый выход старшего разряда которого является выходом устройства, а счетный вход подключен к выходу блока коррекции, вход сигнала опорной частоты которого соединен с выходом задающего генератора, а вход сигнала коррекции и вход знака коррекции блока коррекции соединены соответственно с выходом элемента И и выходом знакового разряда первого регистра, выход которого соединен с первым входом первого блока совпадения, выход которого соединен с первым входом триггера, выход которого соединен с первым входом элемента И, второй вход которого соединен с выходом дешифратора и со счетным входом первого счетчика, выход которого подключен к второму входу первого блока совнадения, выход второго блока совпадения соединен с первым входом элемента ИЛИ, выход которого соединен с вторым входом триггера и с входом начальной установки первого счетчика, а второй вход является

0

5

0

входом начальной установки устройства и соединен с выходом начальной установки блока коррекции и второго счетчика, выходы младщих разрядов которого подключены к входу дешифратора, а выходы старших разрядов соединены с первым входом второго элемента совпадения, второй вход которого соединен с выходом второго регистра, вход которого является вторым управляющим входом устройства.

2. Устройство по п. 1, отличающееся тем, что блок коррекции содержит четыре элемента И, элемент ИЛИ, элемент НЕ, триггер и линию задержки, вход которой соединен с входом сигнала опорной частоты блока коррекции и первым входом четвертого элемента И, выход которого соединен с первым входом элемента ИЛИ, а второй вход - с первым входом первого элемента И и с инверсным выходом D-триггера, вход установки которого соединен с входом начальной установки блока коррекции, С-вход - с выходом линии задержки и первым входом третьего элемента И, а D-вход - с выходом первого элемента И, второй вход которого через элемент НЕ соединен с входом знака коррекции и вторым входом второго элемента И, а третий вход - с входом сигнала коррекции и первым входом второго элемента И, выход которого соединен со вторым входом третьего элемента И, выход которого соединен с вторым входом элемента ИЛИ, выход которого является выходом блока коррекции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции шкалы времени | 1985 |

|

SU1247828A2 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Устройство для приема частотно-фазовых сигналов | 1987 |

|

SU1543563A1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Резервированное устройство для синхронизации | 1984 |

|

SU1195489A1 |

| Устройство управления режимом работы синхрогенератора | 1985 |

|

SU1322504A1 |

| Устройство для контроля времени работы машин | 1981 |

|

SU949672A2 |

| Устройство для управления перемоточным станком | 1982 |

|

SU1087594A1 |

| Комбинированное устройство временной задержки и формирования импульсов | 1987 |

|

SU1443151A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

Изобретение может быть использовано при построении автономных формирователей больших временных интервалов в вычислительных устройствах. Цель изобретения - повышение точности формирования интервалов времени. Устройство содержит задаюший генератор 1, регистр 3, счетчик 4, блок 7 совпадения и триггер 9. Введение блока 2 коррекции, дешифратора 5, регистра 6, блока 8 совпадения, элемента И 10, элемента ИЛИ 11, счетчика 12 и образование новых функцио- нальных связей обеспечивают компенсацию ошибки, возникаюш,ей при формировании больших временных интервалов из-за технических разбросов частоты задающего генератора I от номинального значения с дискретом ±1 период опорной частоты. В описании приведен пример реализации блока 2 коррекции. 1 з.п. ф-лы, 2 ил.

| Устройство формирования времен-НыХ иНТЕРВАлОВ | 1979 |

|

SU824417A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство формирования временных интервалов | 1976 |

|

SU577509A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-06-07—Публикация

1986-08-11—Подача