1

Изобретение относится к области автоматики и вычислительной техники.

Известны автоматические следящие делители периодов следования импульсных сигналов, содержащие входной управляющий триггер, схему «ИЛИ и опорный импульсный генератор, подключенный к входам двух каналов обработки информации. Каждый из каналов содержит последовательно соединенные схему совпадания, счетчик-делитель, счетчикизмеритель и схему сравнения, соединенную со схемой «ИЛИ и входом соответствующего следящего счетчика-делителя, подключенного к другому входу схемы сравнения и выходу установленной в другом канале схемы совпадения. Сбросовый вход последней соединен с одним из выходов входного управляющего триггера и сбросовыми входами соответствующего счетчика-делителя и счетчика-измерителя.

Предлагаемый делитель отличается от известных тем, что, в целях повышения точности работы, в него введен блок коррекции остатка, входы которого соединены со вторыми выходами счетчиков-делителей, выходом схемы «ИЛИ и выходами входного управляющего триггера.

Блок коррекции остатка содержит две входные, дополнительную и промежуточную схемы совпадения, входной, выходной и общий

сумматоры, дешифратор числа, дешифратор и счетчик числа циркуляции, дешифратор и счетчик порядкового номера, матричный определитель задержки, управляющий триггер

и элемент задержки. Причем выходы входных схем совпадения через общий сумматор подключены к дешифратору числа, основные выходы которого соединены с первой группой входов матричного определителя задержки, а

управляющий выход - с одним из входов дополнительной схемы совпадения и входом управляющего триггера. Второй вход последнего соединен с выходом матричного определителя задержки и одним из входов выходного

сумматора. Выход схемы «ИЛИ подключен через дополнительную схему совпадения к другому входу выходного сумматора и одновременно соединен с входом управляющего триггера, входом счетчика порядкового номера, -сбросовым входом счетчика числа циркуляцией и входом входного сумматора, соединенного выходом через элемент задержки с входом промежуточной схемы совпадения, другой вход которой подключен к выходу управляющего триггера, а выход соединен с другим входом входного сумматора и входом счетчика числа циркуляции. Последний через дешифратор числа циркуляции подключен ко второй группе входов матричного определителя задержки, третья группа входов которого

присоединена через дешифратор гоорядкового номера к выходу счетчика порядкового номера. Счетчик порядкового номера соединен сбросовым входом с входом входного управляющего триггера и входом делителя.

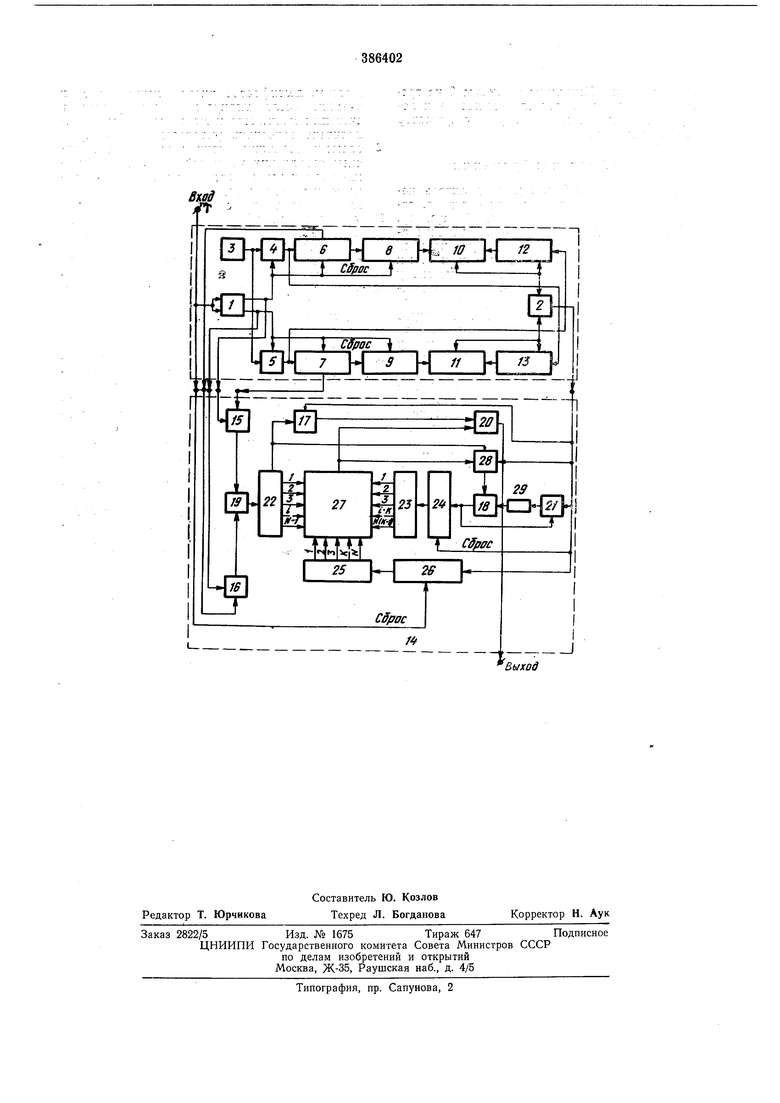

На чертеже показана блок-схема предлагаемого делителя.

Делитель содержит входной управляющий триггер 1, схему «ИЛИ 2 и опорный импульсный генератор 3, подключенный к входу двух идентичных каналов обработки информации. Каждый из каналов содержит последовательно соединенные схему 4 или 5 совпадения, счетчик-делитель 6 или 7, счетчик-измеритель 8 или 9 и схему 10 или И сравнения, соединенную со схемой 2 и входом соответствующего следящего счетчика-делителя 12 или 13, подключенного к другому входу схемы сравнения и к выходу установленной в другом канале обработки информации схемы совпадения. Сбросовый вход последней соединен с одним из выходов входного триггера / и сбросовыми входами соответствующего счетчика-делителя и счетчика-измерителя. Между вторыми выходами счетчиков-делителей 6 и 7, выходом схемы 2 и выходами триггера / включен блок 14 коррекции остатка, который содержит две входные 15 и 16 дополнительную 17 и промежуточную 18 схемы совпадения, общий 19, выходной 20 и входной 21 сумматоры, дешифратор 22 числа, дешифратор 23 и счетчик 24 числа циркуляции, дешифратор 25 и счетчик 26 порядкового номера, матричный определитель 27 задержки, управляющий триггер 28 и элемент 29 задержки.

Делитель работает в две стадии.

В процессе деления временных интервалов, ограниченных импульсами, поступающими на триггер 1, включенный по счетному входу, поочередно открываются схемы 4 и 5 совпадения.

Если с приходом первого импульса открывается схема 5 и импульсы с периодом следования Го с генератора 3 поступают па счетчик-делитель 7, то за время Т (делимый период) счетчик-измеритель 9 отсчитывает в

Т

масштабных единицах NTa, п единиц.

-/Vy о

Принятое счетчиком состояние п передается на схему // сравнения.

С приходом второго импульса состояние триггера 1 изменяется на обратное и открытой для импульсов с генератора 3 оказывается схема 4 во втором канале обработки информации. .Одновременно с делением в счетчике-делителе 6 и счетом в счетчике-измерителе 8 импульсы с генератора 3 через схему 4 поступают на следующий счетчик-делитель 13. Когда этот счетчик принимает состояние числа п, т. е. такое же, как и состояние счетчика-измерителя 9 по измерении первого интервала, схема 11 регистрирует совпадение состояний счетчиков, и импульс, появляющийся- в результате этого на выходе схемы 2, поступает на блок М коррекции остатка.

Одновременно счетчик-делитель 13 сбрасывается, в состояние «О. За время Т таких импульсов со схемы 2 поступает /(. Л,

пТо

Т. е. образуется выходная последовательт

ность импульсов с искомым периодом t - .

N

с приходом третьего импульса в цикле измерения работает схема 5, счетчик-делитель 7 и счетчик-измеритель Я а в цикле деления - схема 5, счетчик-делитель 12 и схема 10 сравнения.

При коррекции потока выходных импульсов из схемы 2 в качестве условного исходного момента принимается начало работы счетчика-делителя 13. При условии некратности делимого Т делителю ЛТо в счетчике-делителе 6 оказывается занесенным состояние г. Это состояние через схему 16 совпадения, управляемую триггером /, и сумматор 19 передается на дешифратор 22 и далее по шине i на матричный определитель 27 задержки. Счетчики 24 числа циркуляции и 26 порядкового номера находятся в состоянии «О. Промежуточная схема 18 совпадення закрыта исходным состоянием управляющего триггера 28.

Первый импульс с выхода схемы 2 поступает на дополнительную схему 17 совпадения, закрытую при всех состояниях дешифратора 22, кроме состояния на триггер 28, переводя его в состояние, при котором открывается схема 18; на сумматор 21, запуская схему 18, сумматор 21 и элемент 29 задержки; на счетчик 24, уртанавлизая его в состояние и на счетчик 26, устанавливая его в состояние «1, которое через дешифратор 25 по первой шине передается на матричный определитель.

Как только в счетчике 24 по ходу счета импульсов установится число i, в матричном определителе формируется импульс, который

лоступает ла выход через сумматор 20 в качестве первого 1со.ответственно задержанного импульса с коррекцией его временного положения на величину tTs-Одновременно имлульс с матричного определителя подается на триггер 28, переводя его в состояние, при котором схема 18 совпадения закрывается, и работа циркулирующего генератора до прихода второго импульса со схемы 2 срывается. В общем виде /С-ый импульс с выхода схемы 2 устанавливает счетчик 26 в состояние «К, которое через дешифратор 25 по шине К поступает на матричный определитель. Для этого импульса выходной отклик на матричном определителе образуется после i-K циркуляцией, т. е. временное положение задержанного /(-го импульса по входу с сумматора 20 скорректировано на величину 1-Д-тз.

В случае кратности делимого Г делителю уУГо остаток на счетчиках-делителях 6 и 7 равен нулю и дешифратор 22 открывает схему

П совпадения. Импульсы со схемы 2 не требуют коррекции временного положения и поступают на выход через схему П и сумматор 20 без задержки.

Предмет изобретения

1.Автоматический следящий делитель периодов следования импульсных сигналов, содержащий входной управляющий триггер, схему «ИЛИ и опорный импульсный генератор, подключенный к входам двух каналов обработки информации, каждый из которых содержит последовательно соединенные схему совпадания, счетчик-делитель, счетчик-измеритель и схему сравнения, соединенную со схемой «ИЛИ и входом соответствующего следящего счетчика-делителя, подключенного к другому входу схемы сравнения и выходу установленной в другом канале обработки информации схемы совпадания, сбросовый вход которой соединен с одним из выходов входного управляющего триггера и сбросовыми входами соответствующего счетчика-делителя и счетчика-измерителя, отличающийся тем, что, с целью повышения точности работы, в него введен блок коррекции остатка, входы которого соединены со вторыми выходами счетчиков-делителей, выходом схемы «ИЛИ и выходами входного управляющего триггера.

2.Делитель по н. 1, отличающийся тем, что блок коррекции остатка содержит две входные, дополнительную и промежуточную схемы совпадения; входной, выходной и общий сумматоры, дешифратор числа, дешифратор и счетчик числа циркуляции, дешифратор и счетчик порядкового номера, матричный определитель задержки, управляющий триггер и

элемент задержки, причем выходы входных схем совпадения через общий сумматор подключены к дешифратору числа, основные выходы которого соединены с первой группой входов матричного определителя задержки, а

управляющий выход - с одним из входов дополнительной схемы совпадения и входом управляющего триггера, второй вход которого соединен с выходом матричного определителя задержки и одним из входов выходного сумматора; выход схемы «ИЛИ подключен через дополнительную схему совпадания к другому входу выходного сумматора и одновременно соединен с входом управляющего триггера, входом счетчика порядкового номера,

сбросовым входом счетчика числа циркуляцией и входом входного сумматора, соединенного выходом через элемент задержки с входом промежуточной схемы совпадания, другой вход которой подключен к выходу управляющего триггера, а выход - к другому входу входного сумматора и входу счетчика числа циркуляции, подключенного через дешифратор числа циркуляции ко второй группе входов матричного определителя задержки, третья группа входов которого присоединена через дешифратор порядкового номера к выходу счетчика порядкового номера, который соединен сбросовым входом с входом входного управляющего триггера и входом делителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления периодов следования импульсных сигналов | 1977 |

|

SU732902A1 |

| Устройство для коррекции числа импульсов по параметру | 1984 |

|

SU1228118A1 |

| Система динамической синхронизации и корректировки рангов объектов в АСУ | 1985 |

|

SU1305630A1 |

| ЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1961 |

|

SU135700A1 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ОСНОСТИ И УЧЕТА ВАГОНОВ | 1970 |

|

SU265930A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ЧАСТОТЫ | 1970 |

|

SU264457A1 |

| ЦИФРОВОЙ АППРОКСИМАТОР | 1972 |

|

SU427465A1 |

| СПОСОБ ОБРАБОТКИ ГИДРОАКУСТИЧЕСКИХ СИГНАЛОВ СО СЛОЖНЫМ ЗАКОНОМ МОДУЛЯЦИИ | 2001 |

|

RU2293356C2 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

| Анализатор гармоник | 1988 |

|

SU1663571A1 |

Авторы

Даты

1973-01-01—Публикация