1

Известны цифровые регуляторы, содержащие датчик импульсов, переключатель задания, делитель ча|Стоты, генератор стабильной частоты, фильтр постоянной составляющей и суммирующий усилитель.

Однако эти регуляторы имеют большую инерционность и нестабильны.

Предлагаемый регулятор дополнительно содерж.ит две схемы совпадения, регистр -сдвига, формирователь длительности импульсов и два триггера, выходы которых подключены ко входам схем совпадения, которые соединены с формирователем длительности импульса, выходы которого подсоединены к параллельно подключенным входам импульсного интегратора и фильтра постоянной составляющей, соединенных с суммирующим усилителем через делитель частоты, связанный с переключателем задания скорости, а выход делителя частоты соединен со счетным входом одного из триггеров, выход которого подключен к одному из входов регистра сдвига, к другому выходу которого подключен генератор стабильной частоты, а первая и последняя ячейки регистра сдвига .подключены ко входам другого триггера.

Это позволяет увелить быстродействие и стабильность и упростить электрическую схему.

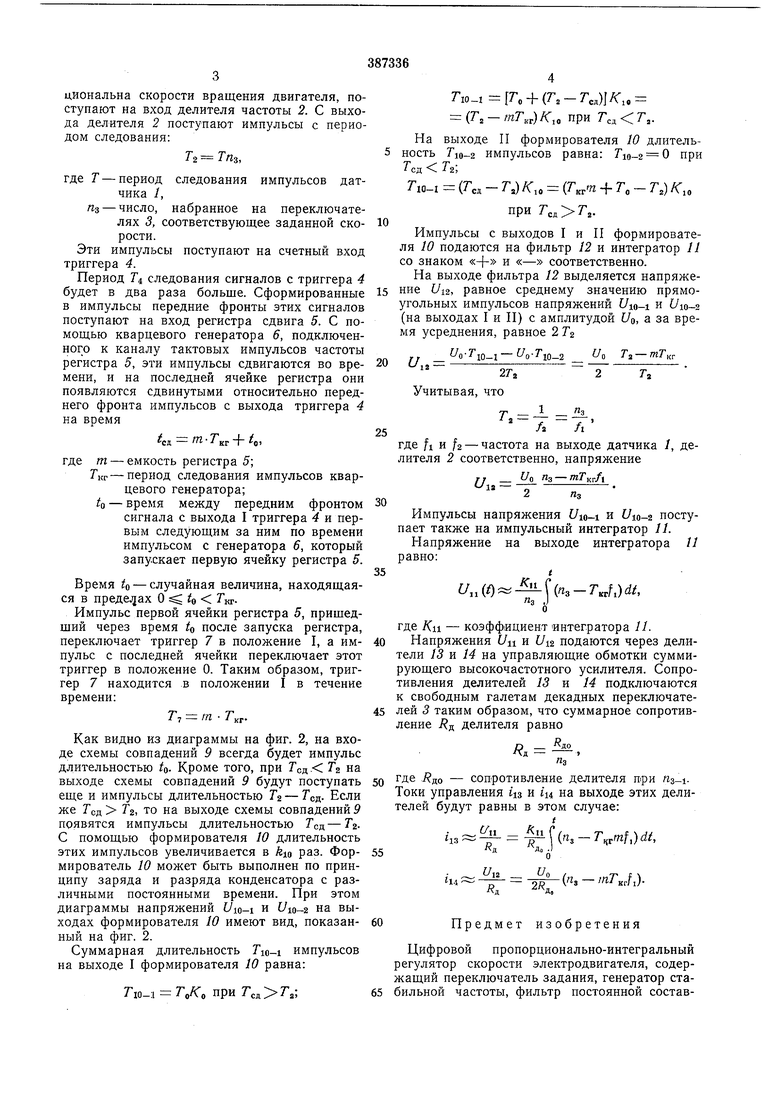

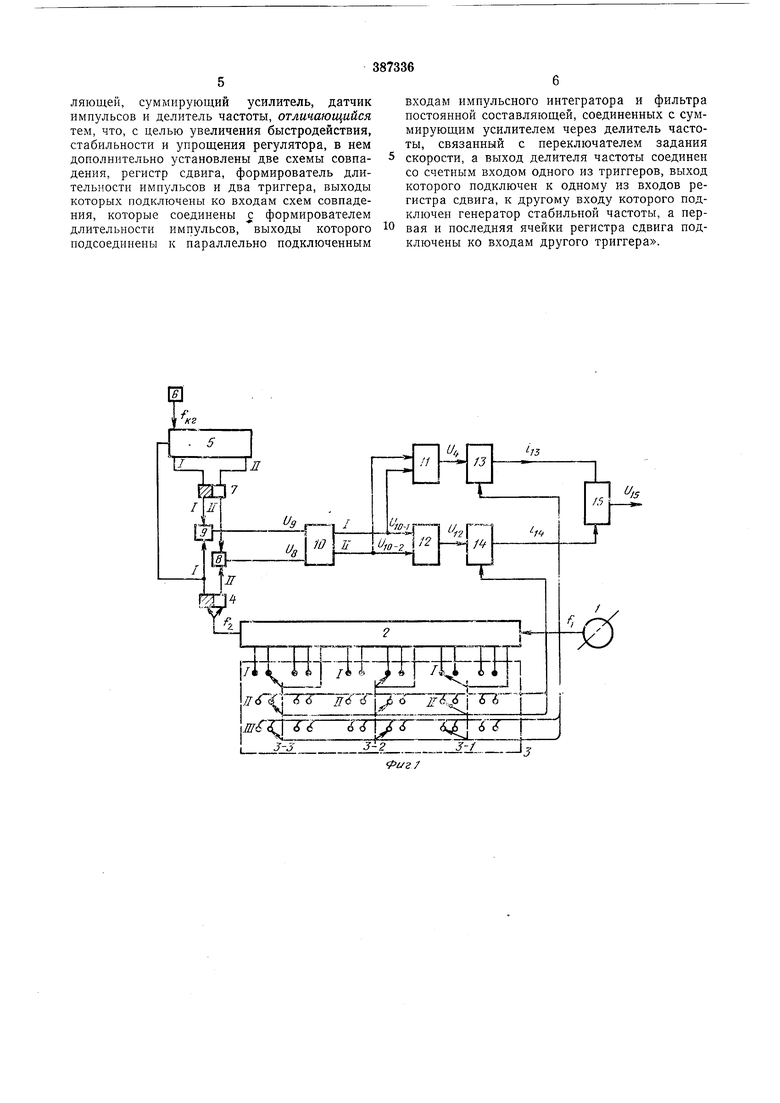

На фиг. 1 представлена функциональная

схема цифрового пропорционально-д1нтегрального регулятора; на фиг. 2 - временная диаграмма регулятора.

Предлагаемый регулятор состоит из датчика импульсов /, механически связанного с валом двигателя, делителя частоты 2, на который поступают импульсы от датчика /, переключателей задания 3, которые определяют емкость делителя 2, триггера 4, делящего на

два частоту с выхода делителя 2, регистра сдвига 5, на вход которого поступают сигналы с выхода триггера 4, кварцевого генератора 6, подающего тактовые импульсы на регистр 5, триггера 7, на выходы которого поступают

импульсы с первой и последней ячеек регистра 5, схем совпадения 5 и Я на входы которых поступают сигналы от триггеров 4 vi 7, формирователя длительности импульсов 10, приходящих со схем 8 и 9, импульсного интегратора П с накопительной емкостью, подключенной к выходам формирователя Ю, фильтра 12, сглаживающего сигналы с выхода формирователя 10, делителей 13 и 14 управляющих сигналов, поступающих от

интегратора 11 и фильтра 12, соединенных с переключателем 3, и суммирующего усилителя 15, на входы которого поступают сигналы от делителей 13 и 14. Устройство работает следующим образом.

Импульсы датчика /, частота которых пропордиональна скорости вращения двигателя, поступают на вход делителя частоты 2. С выхода делителя 2 поступают импульсы с периодом следования:

Гг-Гпз,

где Т - период следования импульсов датчика /,

Пз - число, набранное на переключателях 3, соответствующее заданной скорости.

Эти импульсы поступают на счетный вход триггера 4.

Период Т следования сигналов с триггера 4 будет в два раза больще. Сформированные в импульсы передние фронты этих сигналов поступают на вход регистра сдвига 5. С помощью кварцевого генератора 6, подключенного к каналу тактовых импульсов частоты регистра 5, эти импульсы сдвигаются во времени, и на последней ячейке регистра они появляются сдвинутыми относительно переднего фронта импульсов с выхода триггера 4 на время

г сд :/п-ГкгЧ-4.

где т - емкость регистра 5;

Ткг - период следования импульсов кварцевого генератора;

/о - время между передним фронтом сигнала с выхода I триггера 4 и первым следующим за ним по времени импульсом с генератора 6, который запускает первую ячейку регистра 5.

Время tu - случайная величина, находящаяся в пpeдeJJax О о кгИмпульс первой ячейки регистра 5, пришедший через время U после запуска регистра, переключает триггер 7 в положение I, а импульс с последней ячейки переключает этот триггер в положение 0. Таким образом, триггер 7 находится в положении I в течение времени:

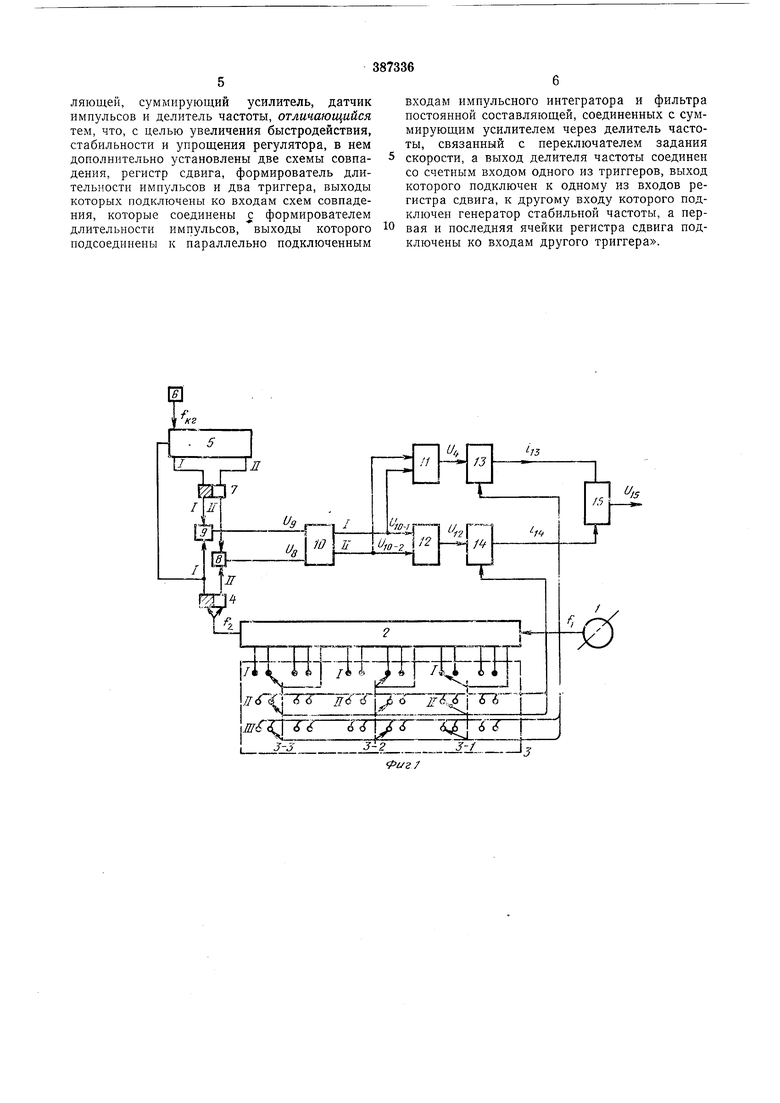

Г, - m ГкгКак видно из диаграммы на фиг. 2, на входе схемы совпадений 9 всегда будет импульс длительностью U- Кроме того, при Тсу,.. TZ на выходе схемы совпадений 9 будут поступать еще и импульсы длительностью TZ - Гсд. Если же Год TZ, то на выходе схемы совпадений 9

появятся импульсы длительностью Год-TZ.

С помощью формирователя 10 длительность этих импульсов увеличивается в йю раз. Формирователь 10 может быть выполнен по принципу заряда и разряда конденсатора с различными постоянными времени. При этом диаграммы напряжений t/io-i и t/io-a на выходах формирователя W имеют вид, показанный на фиг. 2.

Суммарная длительность TW-I импульсов на выходе I формирователя 10 равна:

Tio-.i T, при Год Г,;

Tio-i T, + (T,-T,,, (Т, - тТ,,) К,, при Гед Т,.

На выходе П формирователя 10 длительность Гю-з импульсов равна: О при Год TZ,

(Гед - Г,) /С,о ( -f - Т,} К,,

при ,.

Импульсы с выходов I и П формирователя 10 подаются на фильтр 12 и интегратор И со знаком и «- соответственно.

На выходе фильтра 12 выделяется напряжение (/12, равное среднему значению прямоугольных импульсов напряжений C/io-i и f/io-a (на выходах I и П) с амплитудой UQ, а за время усреднения, равное 2 Т

OTiO-l- 0-710-2

Ua Тз - тТкг

f/,,

2Га 2Т,

Учитывая, что

™ 1 Пд 2 - - - -.

/а /1

где /1 и f2 - частота на выходе датчика /, делителя 2 соответственно, напряжение

i/o Пз - тТкгА

и..

Пз

Импульсы напряжения f/io-i и f/io-a поступает также на импульсный интегратор //.

Напряжение на выходе интегратора 11 равно: 5/

U,,(f)-(n,-T,f,)dt,

«3 J

где /Си - коэффициент интегратора //.

0 Напряжения t/n и Uiz подаются через делители 13 и 14 на управляющие обмотки суммирующего высокочастотного усилителя. Сопротивления делителей 13 и 14 подключаются к свободным галетам декадных переключателей 3 таким образом, что суммарное сопротивление делителя равно

D °до

«3

где , - сопротивление делителя П1ри . Токи управления iis и iu на выходе этих делителей будут равны в этом случае:

/

(rh-T,,mf,}df,

13

и

/Т f

- on 1,3 i Krfij2R

д

предмет изобретения

Цифровой пропорционально-интегральный регулятор скорости электродвигателя, содержащий переключатель задания, генератор ста65 бильной частоты, фильтр постоянной составляющеи, суммирующий усилитель, датчик импульсов и делитель частоты, отличающийся тем, что, с целью увеличения быстродействия, стабильности и упрощения регулятора, в нем дополнптельно установлены две схемы совпадения, регистр сдвига, формирователь длительности импульсов и два триггера, выходы которых подключены ко входам схем совпадения, которые соединены с формирователем длительности импульсов, выходы которого подсоединены к параллельно подключенным

входам импульсного интегратора и фильтра постоянной составляющей, соединенных с суммирующим усилителем через делитель частоты, связанный с переключателем задания скорости, а выход делителя частоты соединен со счетным входом одного из триггеров, выход которого подключен к одному из входов регистра сдвига, к другому входу которого подключен генератор стабильной частоты, а первая и последняя ячейки регистра сдвига подключены ко входам другого триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отделения хроматографического микропика от склона основного пика | 1985 |

|

SU1256047A1 |

| Устройство синхронизации М-последовательности | 1989 |

|

SU1748274A1 |

| ПРЕОБРАЗОВАТЕЛЬ НЕЭЛЕКТРИЧЕСКИХ ВЕЛИЧИН В ЦИФРОВОЙ КОД | 1991 |

|

RU2020745C1 |

| Устройство поиска псевдослучайных последовательностей | 1981 |

|

SU1042199A1 |

| Анализатор частотного спектра | 1980 |

|

SU900209A1 |

| Программируемый источник питания | 1988 |

|

SU1597875A1 |

| Устройство для передачи и приема дискретной информации | 1980 |

|

SU886295A1 |

| Цифровой фазометр | 1985 |

|

SU1298687A2 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Устройство для измерения концентрации пыли в воздухе | 1985 |

|

SU1257477A1 |

J-J

иг

llllllllillliniiiil

«-/

у////

-п

////Л ////А

У/7/

///;

to 1

-tn I

Тед

тТк1

/7/.|рХЛ

1 Т

1

г.

Авторы

Даты

1973-01-01—Публикация