1

Предлагаемое изобретение относится к области вычислительной техники и может быть использовано в ЭВМ.

Известно арифметическое устройство, содержащее регистры чисел и логические элементы «И, недостатком которого является сравнительно большое время выполнения некоторых операций.

Предложенное устройство отличается тем, что в него введены третий и четвертый регистры чисел, схема адресной подстановки, состоящая из блока поразрядной выдачи содержимого третьего и четвертого регистров чисел, блока анализа значений разрядов и блока формирования сквозного переноса, причем блок анализа значений разрядов содержит три элемента импульсный вход первого элемента соединен с щиной импульсов сдвига, а потенциальный вход соединен с единичным выходом триггера младшего разряда четвертого регистра числа, выход первого элемента «И соединен с импульсными входами второго и третьего элементов «И, потенциальные входы которых соединены соответственно с нулевым и единичным выходом триггера младшего разряда третьего регистра числа; блок формирования сквозного переноса состоит из групп по числу разрядов с четырьмя элементами «И в группе, причем импульсные входы первого и второго

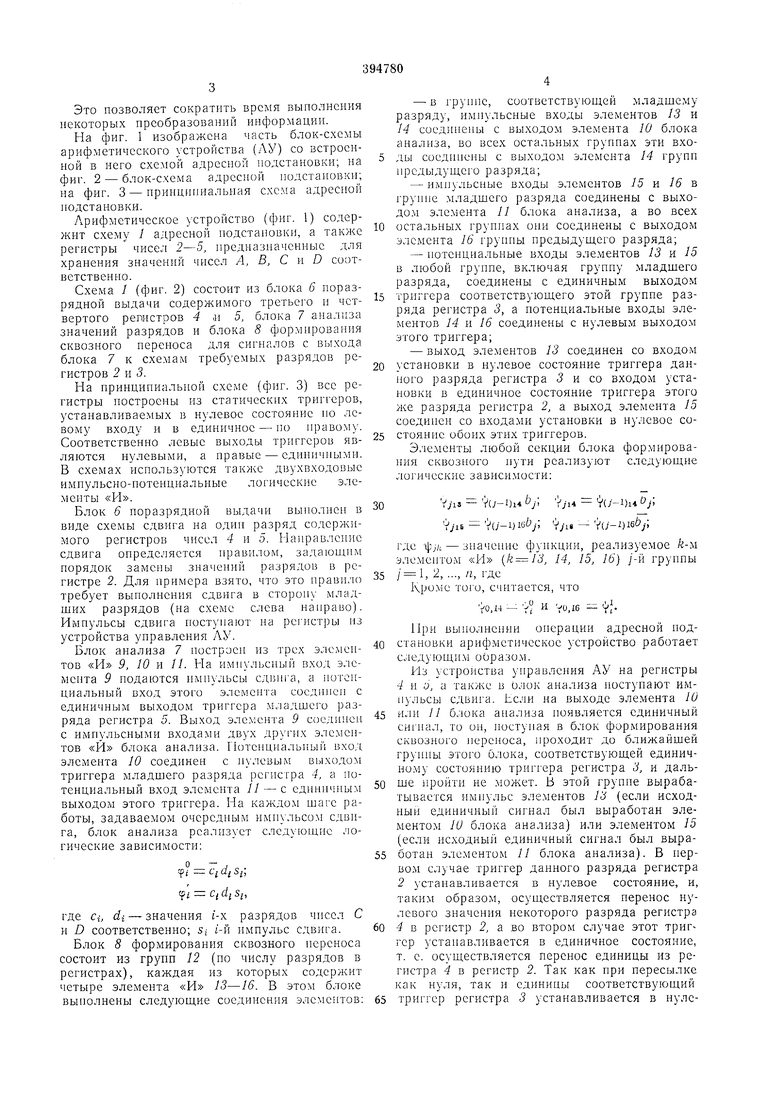

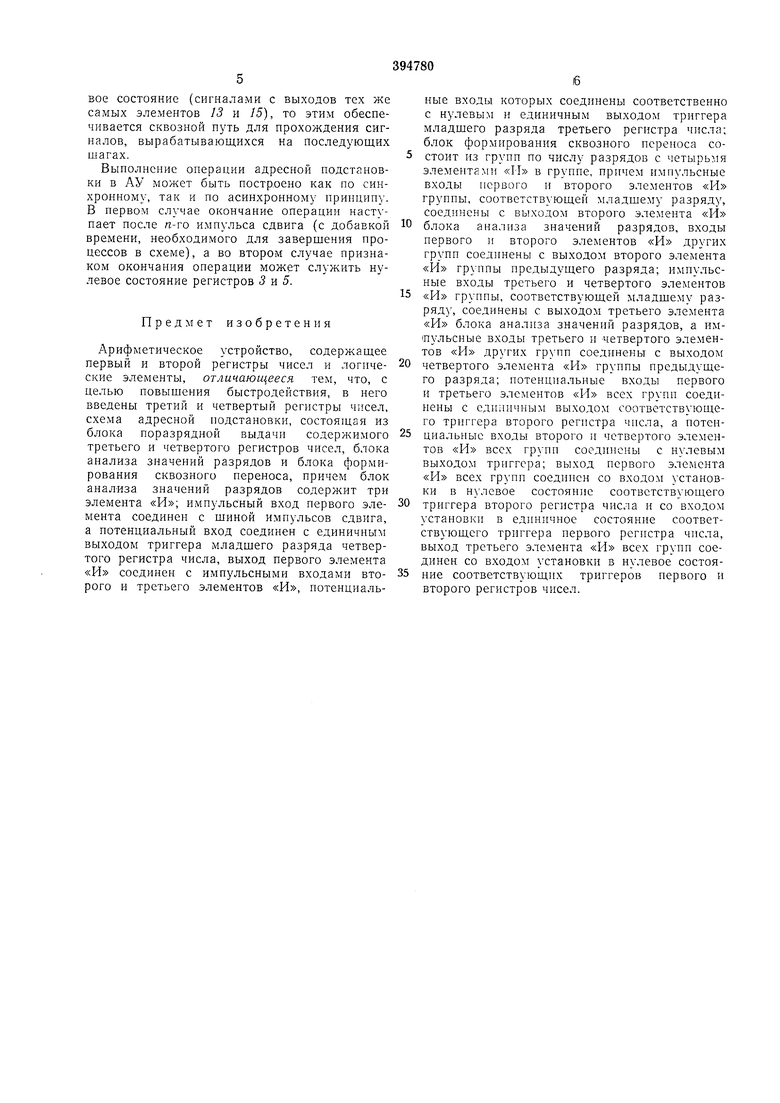

элементов «И группы, соответствующей младшему разряду, соединены с выходом второго элемента «И блока анализа значений разрядов, входы первого и второго элементов «И других групп соединены с выходом второго элемента «И группы предыдущего разряда; импульсные входы третьего и четвертого элементов «И группы, соответствующей младшему разряду, соединены с выходом третьего элемента «И блока анализа значений разрядов, а импульсные входы третьего и четвертого элементов «И других групп соединены с выходом четвертого элемента «И группы предыдущего разряда; потенциальные входы первого и третьего элементов «И всех групп соединены с единичным выходом соответтвующего триггера второго регистра числа, а потенциальные входы второго и четвертого элементов «И всех групп соединены с нулевым выходом триггера; выход первого элемента «И всех групп соединен со входом установки в нулевое состояние соответствующего триггера второго регистра числа и со входом установки в единичное состояние соответствующего триггера первого регистра числа, выход третьего элемента «И всех групп соединен со входами установки в нулевое состояние соответствующих триггеров первого и второго регистров чисел. Это позволяет сократить время выполнения некоторых преобразований информации. На фиг. 1 изображена часть блок-схемы арифметического устройства (ЛУ) со встроеиной в него схемой адресной подстановки; па фиг. 2 - блок-схема адресной подстановки; па фиг. 3 - иринципиальпая схема адресной нодстановки. Арифметическое устройство (фиг. 1) содержит схему / адрееиой иодстановки, а также регистры чисел 2-5, предназиаченные для хранения значений чисел А, В, С и D соответственно. Схема / (фиг. 2) состоит из блока 6 поразрядной выдачи содержимого третьего и четвертого регистров 4 и 5, блока 7 анализа значений разрядов и блока 8 формирования сквозного иереноеа для сигналов с выхода блока 7 к схемам требуемых разрядов регистров 2 и 3. На принциниальиой схеме (фиг. 3) все регистры построены из статических триггеров, устаиавливаемых в нулевое состояние по левому входу и в единичное - но нравому. Соответственно левые выходы триггеров являются нулевыми, а правые - единичными. В схемах используются также двухвходовые имиульсно-потенциальные логические элементы «И. Блок 6 поразрядной выдачи выполнен в виде схемы сдвига па один разряд содержимого регистров чисел 4 и 5. Направление сдвига определяется правилом, задаюпдпм порядок замепы значений разрядов в регистре 2. Для примера взято, что это правило требует выполнения сдвига в сторопу младших разрядов (на схеме слева направо). Импульсы сдвига поступают па регпстры пз устройства управления ЛУ. Блок анализа 7 построен из трех элемеитов «И 9, 10 и //. На импульсный вход элемента 9 подаются импульсы сд1;п1а, а потенциальный вход этогО элемента соединен с единичным выходом триггера младшего разряда регистра 5. Выход элемепта 9 соедипен с импульсными входами двух дру|-их элементов «И блока анализа. Потенциальный вход элемента 10 соединен с пулевым выходом триггера младшего разряда регпстра 4, а потенциальиый вход элемента // - с единнчным выходом этого триггера. На каждом шаге работы, задаваемом очередиым имнульсо.м сдвига, блок анализа реализует следуюшне логические зависимости: о - , cpi CidiSf; ffi - CtdiSi, где Сг, di - значения г-х разрядов чисел С и D соответственно; Si i-ii импульс сдвига. Блок 8 формирования сквозного иереноеа состоит из групп 12 (по числу разрядов в регистрах), каждая из которых содержит четыре элемента «И 13-16. В этом блоке выполнены следующие соединения элемептов: - в грунне, соответствующей младщему разряду, имиульсиые входы элементов 13 и 14 соединены е выходом элемента 10 блока анализа, во всех остальных группах эти входы соединены е выходом элемента 14 групп предыдущего разряда; -импульсные входы элементов 15 к 16 в группе л1ладшего разряда соединены с выходо.м элемента // блока анализа, а во всех остальных груипах оии соединены с выходом элемента 16 группы предыдущего разряда; -потенциальиые входы элементов 13 и 15 в любой группе, включая группу младшего разряда, соединены с единичным выходом триггера соответствующего этой группе разряда регистра 3, а потенциальные входы элементов 14 и 16 соединены с нулевым выходом этого триггера; -выход элементов 13 еоединен со входом установки в нулевое состояние триггера данного разряда регистра ,3 и со входом установки в единичное состояние триггера этого же разряда региетра 2, а выход элемента 15 соедипеп со входами установки в нулевое состояние обоих этих триггеров. Элементы любой секции блока формирования сквозного пути реализуют следующие логические зависимости: V;u - Y(;-i)i4 TJH - (j-i)n j ijii ) Oyj, (j-i)isbj; где ф;;; - значенне функции, реализуемое /г-м элементом «И (, 14, 15, 16) /-Й группы ,2, ..., п, где Кроме того, считается, что fo,M - v и yo,i6 . Нри выполнении онерации адресной подстановки арифметическое уетройство работает следующим ооразол. Из устройства уиравлсния АУ на регистры 4 и о, а также в Олок анализа ноступают импульеы сдвига. Ьсли на выходе элемента W или // блока анализа ноявляется единичный си1пал, то оп, поступая в блок формирования сквозного переноса, проходит до ближайшей груипы этого блока, соответствующей единично.му состояпию триггера регистра 3, и дальше пройти не может. Ь этой группе вырабатывается импульс элементов 13 (если исходный единичный сигнал был выработан элементом W блока анализа) или элементом 15 (если исходный единичный сигнал был выработан элементом 11 блока анализа). В нервом случае триггер данного разряда регистра 2 устанавливается в нулевое состояние, и, таким образом, осуществляется неренос нулевого значения некоторого разряда регистра 4 в регистр 2, а во втором случае этот триггер устаиавливается в единичное состояние, т. е. осуществляется перенос единицы из регистра 4 в регистр 2. Так как при пересылке ак нуля, так и единицы соответствующий триггер региетра 3 устанавливается в нулевое состояние (сигналами с выходов тех же самых элементов 13 и 15), то этим обеспечивается сквозной путь для прохождения сигналов, вырабатывающихся на последующих шагах.

Выполнение операции адресной подстановки в АУ может быть построено как по синхронному, так и по асинхронному принципу. В первом случае окончание операции наступает после п-то импульса сдвига (с добавкой времени, необходимого для завершения процессов в схеме), а во втором случае признаком окончания операции может служить нулевое состояние регистров 5 и 5.

Предмет изобретения

Арифметическое устройство, содержащее первый и второй регистры чисел и логические элементы, отличающееся тем, что, с целью повышения быстродействия, в него введены третий и четвертый регистры чисел, схема адресной подстановки, состоящая из блока поразрядной выдачи содержимого третьего и четвертого регистров чисел, блока анализа значений разрядов и блока формирования сквозного переноса, причем блок анализа значений разрядов содержит три элемента импульсный вход первого элемента соединен с шиной импульсов сдвига, а потенциальный вход соединен с единичным выходом триггера младщего разряда четвертого регистра числа, выход первого элемента «И соединен с импульсными входами второго и третьего элементов «И, потенциальные входы которых соединены соответственно с нулевым и единичным выходом триггера младшего разряда третьего регистра числа; блок формирования сквозного переноса состоит из групп по числу разрядов с четырьмя элементами «И в группе, причем импульсные входы первого п второго элементов «И группы, соответствующей младшему разряду, соединены с выходом второго элемента «И блока анализа значений разрядов, входы первого и второго элементов «И других групп соединены с выходом второго элемента «И группы предыдущего разряда; импульсные входы третьего и четвертого элементов «И группы, соответствующей младщему разряду, соединены с выходом третьего элемента «И блока анализа значений разрядов, а им(пульсные входы третьего и четвертого элементов «И групп соединены с выходом четвертого элемента «И группы предыдущего разряда; потенциальные входы первого и третьего элементов «И всех групп соединены с единичным выходом соответствующего триггера второго регистра числа, а потенциальные входы второго и четвертого элементов «И всех групп соединены с нулевым выходом триггера; выход первого элемента «И всех групп соединен со входо.м установки в нулевое состояние соответствующего триггера второго регистра числа и со входом установки в единичное состояние соответствующего триггера первого регпстра числа, выход третьего элемента «И всех групп соединен со входом установки в нулевое состояние соответствующих триггеров первого и второго регистров чисел.

L..

Фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Узел для сортировки информации | 1972 |

|

SU454548A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

| Устройство для сортировки чисел | 1990 |

|

SU1781680A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Генератор последовательности чисел | 1983 |

|

SU1166089A1 |

| Управляемый вероятностный преобразователь | 1975 |

|

SU638995A1 |

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU960792A1 |

| Генератор псевдослучайных чисел | 1981 |

|

SU1013955A1 |

| Устройство сортировки чисел | 1986 |

|

SU1441384A1 |

От генератора итдльсоб сдМа

Авторы

Даты

1973-01-01—Публикация