1

Изобретение относится к вычислительной технике и может быть использовано в арифметических устройствах ЭВМ, предназначенных, например, для обработки данных в автоматизированных системах управления.

Известен узел для сортировки информации, содержащий логические элементы «И и схемы «ИЛИ, схему формирования сквозного переноса, управляющие и информационные щины. В известной схеме узла сортировки информации наличие не участвующих в операции разрядов приводит к холостым тактам, связанным с оперированием этими разрядами, что увеличивает время выполнения всей операции.

Цель изобретения - повыщение быстродействия узла адресной подстановки путем исключения холостых тактов.

Для осуществления этой цели узел сортировки информации содержит п-разрядную схему избирательной выдачи, каждый разряд которой состоит из четырех логических элементов «И, причем потенциальные входы первого и второго элементов соединены с соответствующими данному разряду щинами «О и «1 «Признак замещения, а потенциальные входы третьего и четвертого элементов «И соединены с соответствующими данному разряду щинами «О и «1 «Замещение, импульсные входы первого и второго элементов «И объединены и соединены с выходом первого элемента «И предшествующего младщего разряда, причем в младщем разряде импульсные входы первого и второго элементов «И соединены с управляющей щиной «Такт, выход второго элемента «И соединен с соответствующей данному разряду щиной «Запись «О признака замещения и импульсными входами третьего и четвертого элементов «И, выходы третьих элементов «И всех разрядов соединены с соответствующими входами первой схемы «ИЛИ, выход которой соединен с первым входом схемы формирования сквозного переноса; выходы четвертых элементов «И

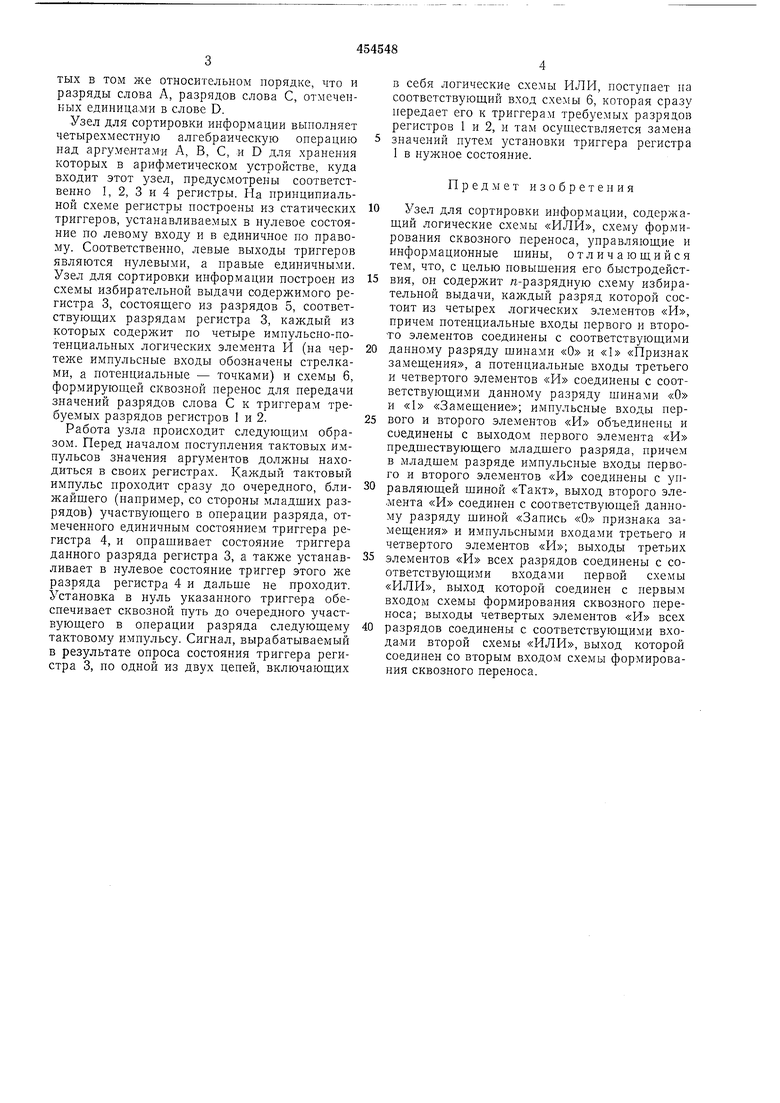

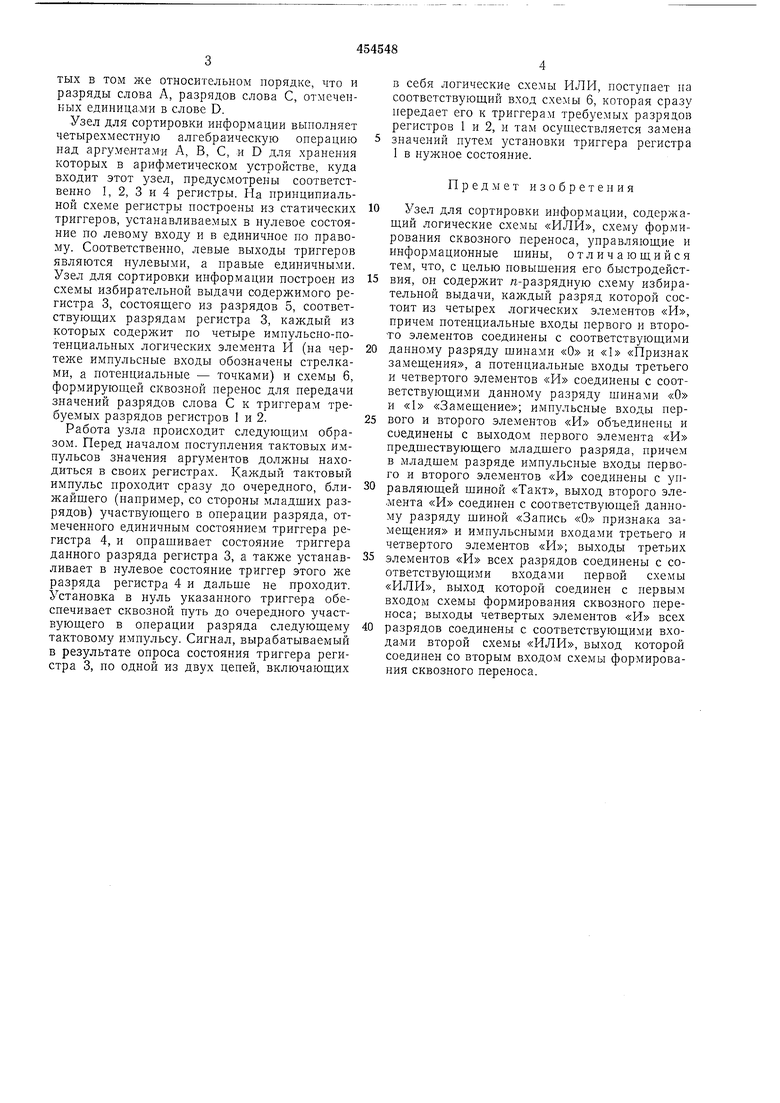

всех разрядов соединены с соответствующими входами второй схемы «ИЛИ, выход которой соединен с вторым входом схемы формирования сквозного переноса. На чертеже дана логическая схема узла

сортировки информации.

На схеме приняты следующие обозначения; 1, 2, 3, 4 - п-разрядные регистры чисел АУ (соответствуют числам А, В, С, D), содер/кащие схемы 5 - один разряд п-разрядной схемы избирательной выдачи, содержащей элементы 6 - схема формирования сквозного переноса и 7 - щина «Такт.

Узел сортировки информации осуществляет замену значений разрядов слова А, соответствующих единицам в слове В, значениями взятых в том же относительном порядке, что и разряды слова А, разрядов слова С, отмеченных единица.ми в слове D.

Узел для сортировки информации выполняет четырехместную алгебраическую операцию над аргументами А, В, С, и D для хранения которых в арифметическом устройстве, куда входит этот узел, предусмотрены соответственно I, 2, 3 и 4 регистры. Н,а принципиальной схеме регистры построены из статических триггеров, устанавливаемых в нулевое состояние по левому входу и в единичное по правому. Соответственно, левые выходы триггеров являются нулевыми, а правые единичными. Узел для сортировки информации построен из схемы избирательной выдачи содержимого регистра 3, состоящего из разрядов 5, соответствующих разрядам регистра 3, каждый из которых содержит по четыре импульсно-потенциальных логических элемента И (на чертеже импульсные входы обозначены стрелками, а потенциальные - точками) и схемы 6, формирующей сквозной перенос для передачи значений разрядов слова С к триггерам требуемых разрядов регистров 1 и 2.

Работа узла происходит следующим образом. Перед началом поступления тактовых импульсов значения аргументов должны находиться в своих регистрах. Каждый тактовый импульс проходит сразу до очередного, ближайщего (например, со стороны младших разрядов) участвующего в операции разряда, отмеченного единичным состоянием триггера регистра 4, и опращивает состояние триггера данного разряда регистра 3, а также устанавливает в нулевое состояние триггер этого же разряда регистра 4 и дальще не проходит. Установка в нуль указанного триггера обеспечивает сквозной путь до очередного участвующего в операции разряда следующему тактовому импульсу. Сигнал, вырабатываемый в результате опроса состояния триггера регистра 3, по одной из двух цепей, включающих

в себя логические схемы Р1ЛИ, поступает на соответствующий вход схемы 6, которая сразу передает его к триггерам требуемых разрядов регистров 1 и 2, и там осуществляется замена 5 значений путем установки триггера регистра 1 в нужное состояние.

Предмет изобретения

0 Узел для сортировки информации, содержащий логические схемы «ИЛИ, схему фор.мирования сквозного переноса, управляющие и информационные щины, отличающийся тем, что, с целью повыщения его быстродейст5 ВИЯ, он содержит л-разрядную схему избирательной выдачи, каждый разряд которой состоит из четырех логических элементов «И, причем потенциальные входы первого и второго элементов соединены с соответствующими

0 данному разряду щинами «О и «1 «Признак замещения, а потенциальные входы третьего и четвертого элементов «И соединены с соответствующими данному разряду шинами «О и «1 «Замещение ; импульсные входы первого и второго элементов «И объединены и соединены с выходом первого элемента «И предшествующего младшего разряда, причем в младшем разряде импульсные входы первого и второго элементов «И соединены с управляющей шиной «Такт, выход второго эле.мента «И соединен с соответствующей данному разряду шиной «Запись «О признака замещения и импульсными входами третьего и четвертого элементов выходы третьих

5 элементов «И всех разрядов соединены с соответствующими входами первой схемы «ИЛИ, выход которой соединен с первым входом схемы формирования сквозного переноса; выходы четвертых элементов «И всех

0 разрядов соединены с соответствующими входами второй схемы «ИЛИ, выход которой соединен со вторым входом схемы формирования сквозного переноса. LI Ш| Чш-т

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1973 |

|

SU394780A1 |

| УСТРОЙСТВО для ЦИФРОВОГО РЕГУЛИРОВАНИЯ СКОРОСТИ | 1973 |

|

SU374580A1 |

| Устройство для сопряжения с общей маги-СТРАлью ВычиСлиТЕльНОй СиСТЕМы | 1979 |

|

SU809143A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Канал обмена многомашинного комплекса | 1984 |

|

SU1236492A1 |

| ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО" | 1973 |

|

SU368606A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Буферное запоминающее устройство | 1978 |

|

SU750568A1 |

| Однородная вычислительная система | 1984 |

|

SU1275458A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

Авторы

Даты

1974-12-25—Публикация

1972-05-26—Подача