подключены к информационным входам соответствующих разрядов регистра сдвига, выходы первого и второго разрядов регистра сдвига подключены к первым входам первого и второга -сумматоров по модулю два соответственно, вторые входы которых подключены к выходам соответствующих переключателей второй группы, выходы первого и второго сумматоров по модулю два подключены к информационным входам коммутатора блока формирования знака, выход генератора.тактов подключен к синхронизирующим входам регистра начальных значений и регистра коэффициентов, первый выход первого распределителя импульсов подключен к синхронизирующему входу второго распределителя импульсов, к нулевым входам первого и третьего триггеров, а татсже к запрещающим входам первого и второго блоков преобразования в дополнительный код, первый потенциальный выход второго расп)еделителя импульсов подключен к управляющему входу коммутатора блока формирования знака и к. первому входу пятого элемента И, второй импульсный выход второго распределителя импульсов подключен к входу первого делителя частоты и к единичному входу четвертого триггера, выход которого подключен к уп..равляющему входу первого коммутатора выход первого коммутатора подключен

к второму ВХОДУ первого элемента И, первый информационный вход первого коммутатора соединен информационным входом элемента задержки и подключен к последовательному выходу ре-г гистра функций, выход элемента задержки подключен к второму информационному входу первого коммутатора и к информационному входу первого блока преобразования в дополнительный код, выход которого подключен к первому информационному входу второго коммутатора, управляющий вход которого подключен к единичному выходу первого триггера, а выход к первому информационному входу третьего коммутатора, второй информационный вход третьего коммутатора подключен к последовательному выходу и к первому последовательному информационному входу регистра начальных значений, управляющий вход третьего коммутатора подключен

к выходу .второго триггера, выход третьего коммутатора подключен к второму входу второго элемента И и к последовательному информационному входу регистра промежуточных результатов, последовательный выход которого подключен к второму информационному входу второго коммутатора, последовательный выход регистра коэффициентов подключен к его первому последовательно.му информационному входу и к второму входу четвертого элемента И, выход четвертого элемента И подключен к информационному входу второго блока преобразования в допол,нительный код, выход которого подключен к второму входу сумматора , п-й (п - разрядность чисел) выход первого распределителя импульсов подключен к нулевому входу четвертого триггера и к второму входу пятого элемента И, выход которого подключен к нулевому входу второго триггера, выход элемента ИЛИ блока настройки подключен к вторым последовательным информационным входам регистра начальных значений и регистра коэффициентов, последовательный информационный вход, сдвигающий вход иуправляющий вход записи регистра сдвига блока формирования знака подключены соответственно к входу с матора, к выходу первого делителя частоты и к выходу второго триггера, выход первого разряда регистра сдвига блока формированйя знака является выходом знака генератора последовательности чисел и подключен к разрешающему входу первого блока . . преобразования в дополнительный код, выход коммутатора блока формирования знака подключен к разрешающему входу второго блока преобразования в дополнительный код, блок;управления состоит из формирователя одиночных импульсов, триггера, элемента

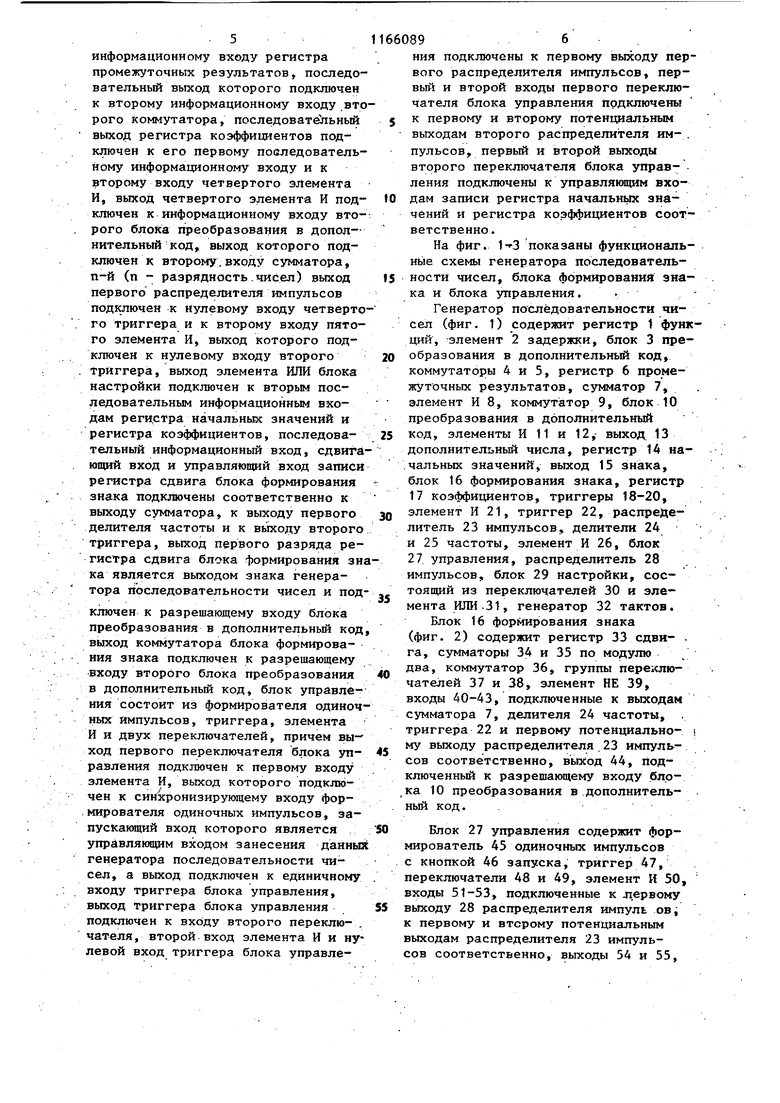

И и двух переключателей, причем выход первого переключателя блока управления подключен к первому входу элемента И, выход которого подклюг чен к синхронизирующему входу формирователя одиночных импульсов, запускающий вход которого является управляющим входом занесения данных генератора последовательности чисел, а выход подключен к единичному входу триггера блока управле- ния, выход триггера блока управления подключен к входу второго переключателя, второй вход элемента И и нулевой вход триггера блока управления подключены к первому выходу первого распределители импульсов, .первый и второй входы первого переключателя блока управления под 9ключены к первому и второму потенциальным выходам второго распределителя импульсов, первый и второй выходы второго переключателя блока управления подключены к управляющим входам зациси регистра начальных значений и регистра коэффициентов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор последовательностей чисел | 1982 |

|

SU1067490A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Функциональный преобразователь | 1983 |

|

SU1108442A1 |

| Интегро-дифференциальный вычислитель | 1983 |

|

SU1108445A2 |

| Квадратор | 1985 |

|

SU1258826A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1984 |

|

SU1228290A1 |

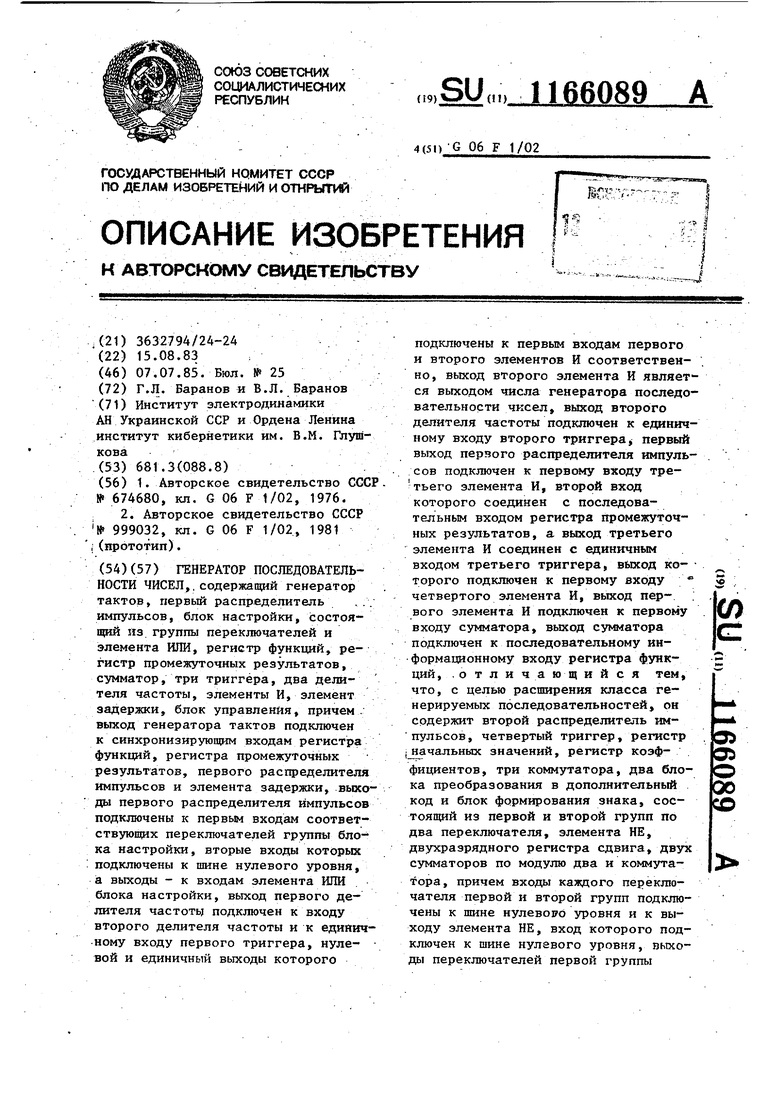

ГЕНЕРАТОР ПОСЛЕДОВАТЕЛЬНОСТИ ЧИСЕЛ,, содержащий генератор тактов, первый распределитель ... импульсов, блок настройки, состояпщй из группы переключателей и элемента ИЛИ, регистр функций, регистр промежуточных результатов, сумматор, три триггера, два делителя частоты, элементы И, элемент задержки, блок управления, причем . выход генератора тактов подключен к синхр они 3 ИР ующим входам р е гистра функций, регистра промежуточных результатов, первого распределителя Импульсов и элемента задержки, выходы первого распределителя импульсов подключены к первым входам соответствующих переключателей группы блока настройки, вторые входы которых подключены к шине нулевого уровня, а выходы - к входам элемента ИЛИ блока настройки, выход первого делителя частотц подключен к входу второго делителя частоты и к единичному входу первого триггера, нулевой и единичный выходы которого подключены к первым входам первого и второго элементов И соответственно, выход второго элемента И является выходом числа генератора последовательности чисел, выход второго делителя частоты подключен к единичному входу второго триггера первый выход первого распределителя импульсов подключен к первому входу третьего элемента И, второй вход которого соединен с последовательным входом регистра промежуточных результатов, а выход третьего элемента И соединен с единичным входом третьего триггера, выход ко- торого подключен к первому входу четвертого элемента И, выход пер-. W С вого элемента И подключен к первому входу сумматора, выход сумматора подключен к последовательному информационному входу регистра функций, .отличающийся тем, что, с целью расширения класса генерируемых последовательностей, он содержит второй распределитель има пульсов, четвертый триггер, регистр jJ aчaльныx значений, регистр коэфо: о эо со фициентов, три коммутатора, два блока преобразования в дополнительный код и блок формирования знака, состоящий из первой и второй групп по два переключателя, элемента НЕ, двухразрядного регистра сдвига, двух сумматоров по модулю два и коммутатора, причем входы каждого переключателя первой и второй групп подключены к шине нулевого уровня и к выходу элемента НЕ, вход которого подключен к шине нулевого уровня, выходы переключателей первой группы

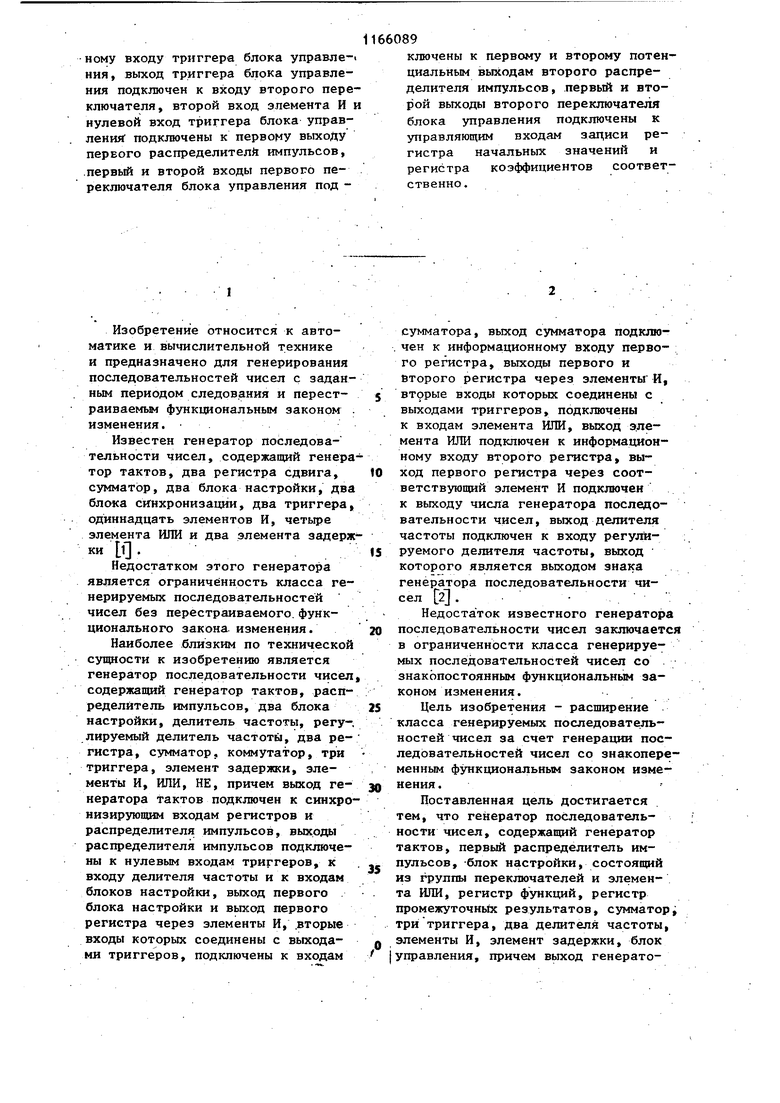

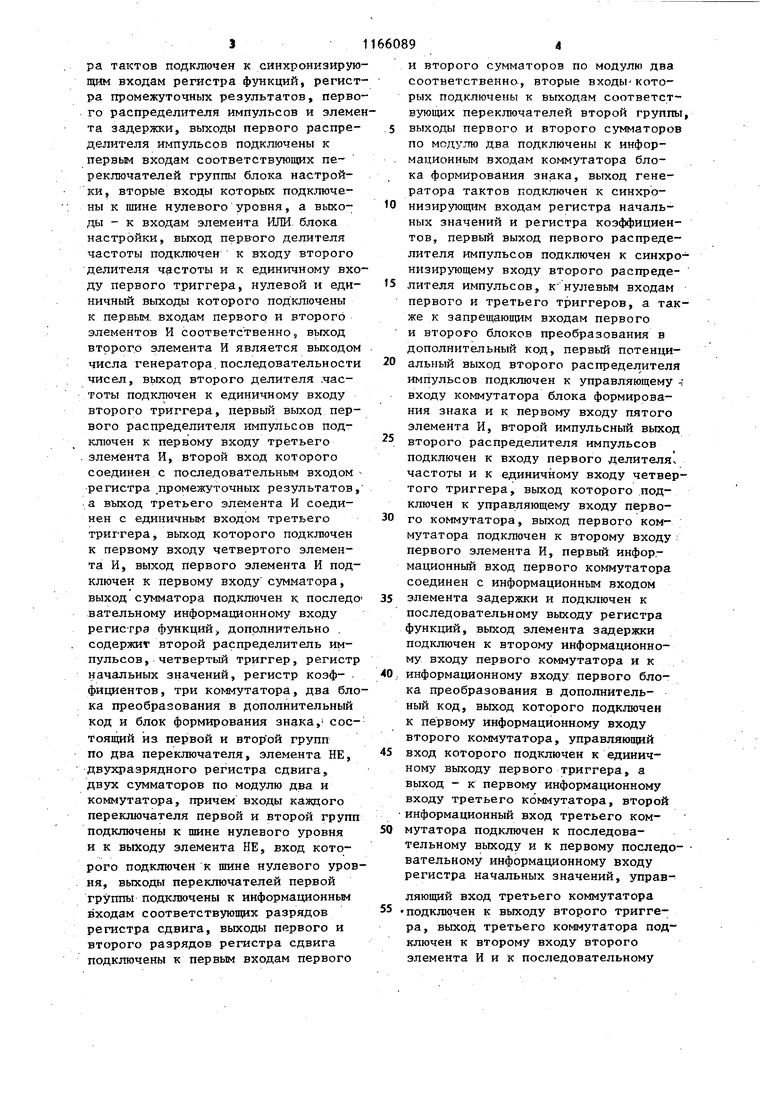

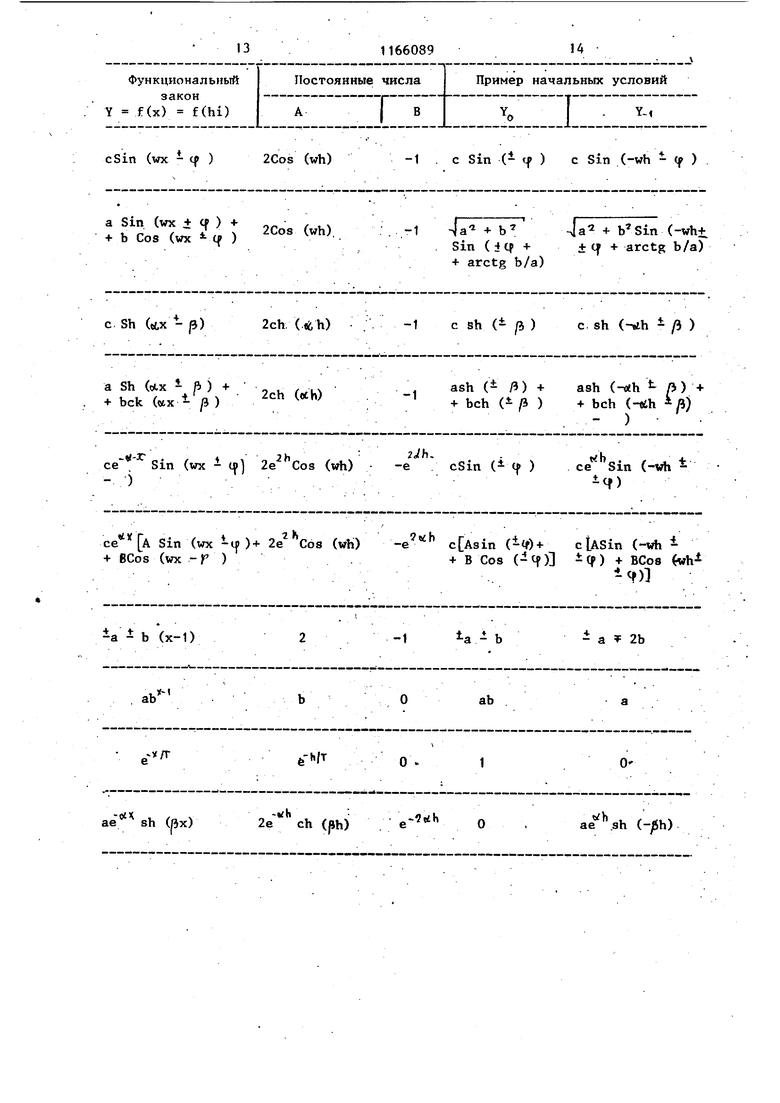

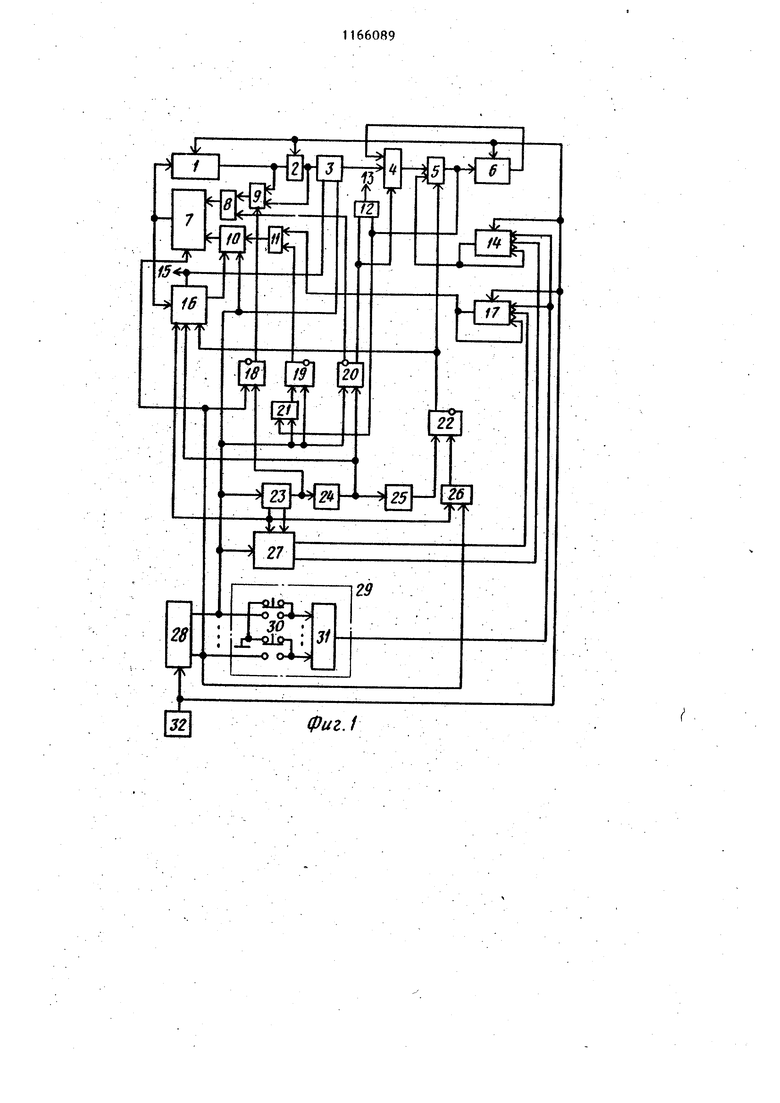

Изобретение относится к автоматике и вычислительной технике и предназначено для генерирования последовательностей чисел с заданным периодом следования и перестраиваемым функциональным законом изменения. Известен генератор последовательности чисел, содержапщй генера тор тактов, два регистра сдвига, сумматор, два блока настройки, два блока си нхронизации, два триггера одиннадцать элементов И, четыре элемента ИЛИ и два элемента задерж ки 1 . Недостатком этого генератора является ограниченность класса генерируемых последовательностей чисел без перестраиваемого, функционального закона, изменения. Наиболее близким по технической сущности к изобретению является генератор последовательности чисел содержащий генератор тактов, распределйтель импульсов, два блока настройки, делитель частоты, регулируемый делитель частоты, два регистра, сумматор, коммутатор, три триггера, элемент задержки, злементы И, ИЛИ, НЕ, причем выход генератора тактов подключен к синхро низирующим входам регистров и распределителя импульсов, выходы распределителя импульсов подключены к нулевым входам триггеров, к входу делителя частоты и к входам блоков настройки, выход первого . блока настройки и выход первого регистра через элементы И, вторые входы которых соединены с выходами триггеров, подключены к входам сумматора, выход сумматора подключей к информационному входу первого регистра, выходы первого и второго регистра через элементы И, вторые входы которых соединены с выходами триггеров, подключены к входам элемента ИЛИ, выход элемента ИЛИ подключен к информационному входу второго регистра, выход первого регистра через соответствующий элемент И подключен к выходу числа генератора последовательности чисел, выход делителя частоты подключен к входу регулй- ; руемого делителя частоты, выход которого является выходом знака генератора последовательности чисел 2 . . . Недостаток известного генератора последовательности чисел заключается в ограниченности класса генерируемых последовательностей чисел со знакопостоянным функциональным законом изменения. Цель изобретения - расширение класса генерируемых последовательностей чисел за счет генерации последовательностей чисел со знакопеременным функциональным законом изменения. Поставленная цель достигается тем, что генератор последовательности чисел, содержащий генератор тактов, первый распределитель импульсов, -блок настройки, состоящий из группы переключателей и элемента ИЛИ, регистр функций, регистр промежуточных результатов, сумматор; тритриггера, два делителя частоты, элементы И, элемент задержки, блок управления, причем выход генератоpa тактов подключен к синхронизирующим входам регистра функций, регистра промежуточных результатов, первого распределителя импульсов и элемета задержки, выходы первого распределителя импзльсрв подключены к первым входам соответствующих переключателей группы блока настройки, вторые входы которых подключены к шине нулевого уровня, а выходы - к входам элемента ИЛИ блока настройки, выход перв-ого делителя частоты подключен к входу второго делителя частоты и к единичному входу первого триггера, нулевой и единичный выходы которого подключены к первым, входам первого и второго элементов И соответственно, выход второго элемента И является выходом числа генератора.последовательности чисел, вьгход второго делителя .частоты подключен к единичному входу второго триггера, первый выход первого распределителя импульсов подключен к первому входу третьего . элемента И, второй вход которого соединен с последовательным входом регистра .промежуточных результатов, а выход третьего элемента И соединен с единичным входом третьего триггера, выход которого подключен к первому входу четвертого элемента И, выход первого элемента И подключен к первому входу сумматора, выход сумматора подключен к последо вательному информационному входу регистра функций, дополнительно . содержит второй распределитель импульсов, четвертый триггер, регистр начальных значений, регистр коэф- . фициентов, три коммутатора, два блока преобразования в дополнительный код и блок формирования знака, состоящий из первой и второй групп по два переключателя, элемента НЕ, двухразрядного регистра сдвига, двух сумматоров по модулю два и коммутатора, причем входы каждого переключателя первой и второй групп подключены к шине нулевого уровня и к выходу элемента НЕ, вход которого подключен к шине нулевого уровня, выходы переключателей первой группы подключены к информационным входам соответствующих разрядов регистра сдвига, выходы первого и второго разрядов регистра сдвига подключены к первым входам первого

и второго сумматоров по модулю два соответственно, вторые входы-которых подключены к выходам соответствзлощих переключателей второй группы,

5 выходы первого и второго сумматоров

по модулю два подключены к инфор. мационным входам коммутатора блока формирования знака, выход генератора тактов подключен к синхронизирующим входам регистра начальных значений и регистра коэффициентов, первый выход первого распределителя импульсов подключен к синхронизирующему входу второго распределителя импульсов, кнулевым входам первого и третьего триггеров, а также к запрещаюпщм входам первого и второго блоков преобразования в дополнительный код, первый потенциальный выход второго распределителя импульсов подключен к управляющему -: входу коммутатора блока формирования знака и к первому входу пятого элемента И, второй импульсный выход второго распределителя импульсов подключен к входу первого делителя , частоты и к единичному входу четвертого триггера, выход которого .подключен к управляющему входу первого коммутатора, выход первого коммутатора подключен к второму входу ; первого элемента И, первый инфор.мационный вход первого коммутатора соединен с информационным входом

5 элемента задержки и подключен к последовательному выходу регистра функций, выход элемента задержки подключен к второму информационному входу первого коммутатора и к

информационному входу первого блока преобразования в дополнительный код, выход которого подключен к первому информационн.ому входу второго коммутатора, управляющий

5 вход которого подключен к единичному выходу первого триггера, а выход - к первому информационному входу третьего коммутатора, второй информационный вход третьего коммутатора подключен к последовательному выходу и к первому последо- вательному информационному входу регистра начальных значений, управляющий вход третьего коммутатора

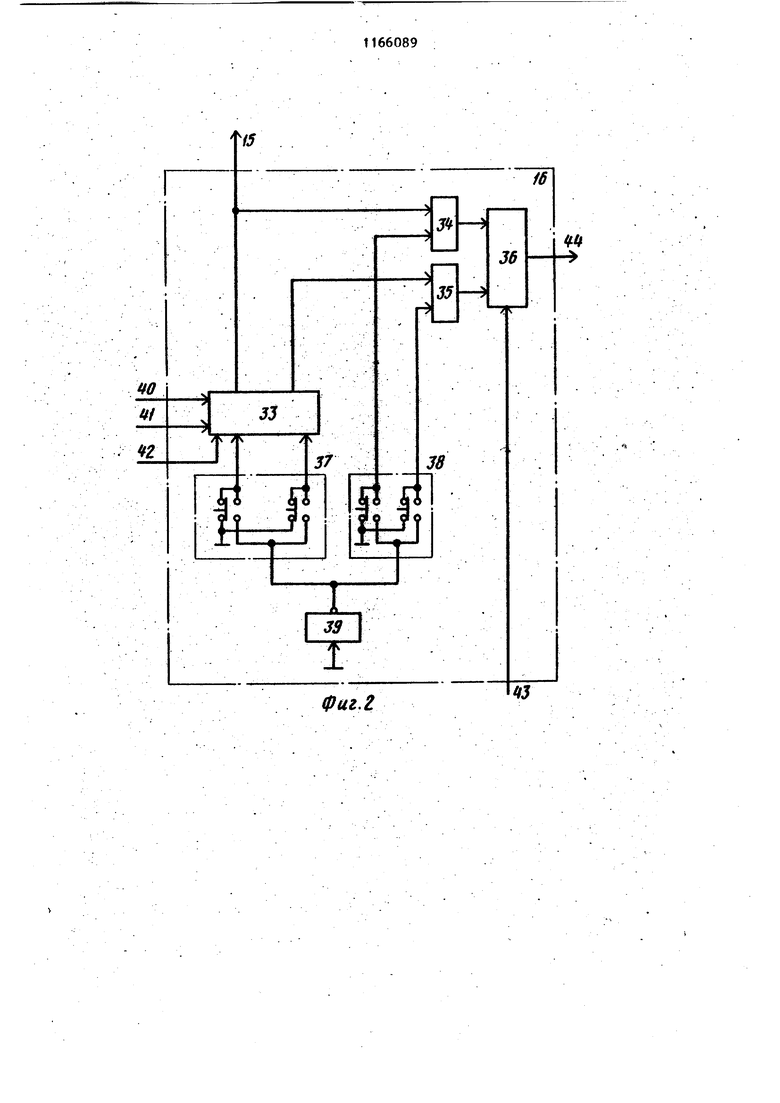

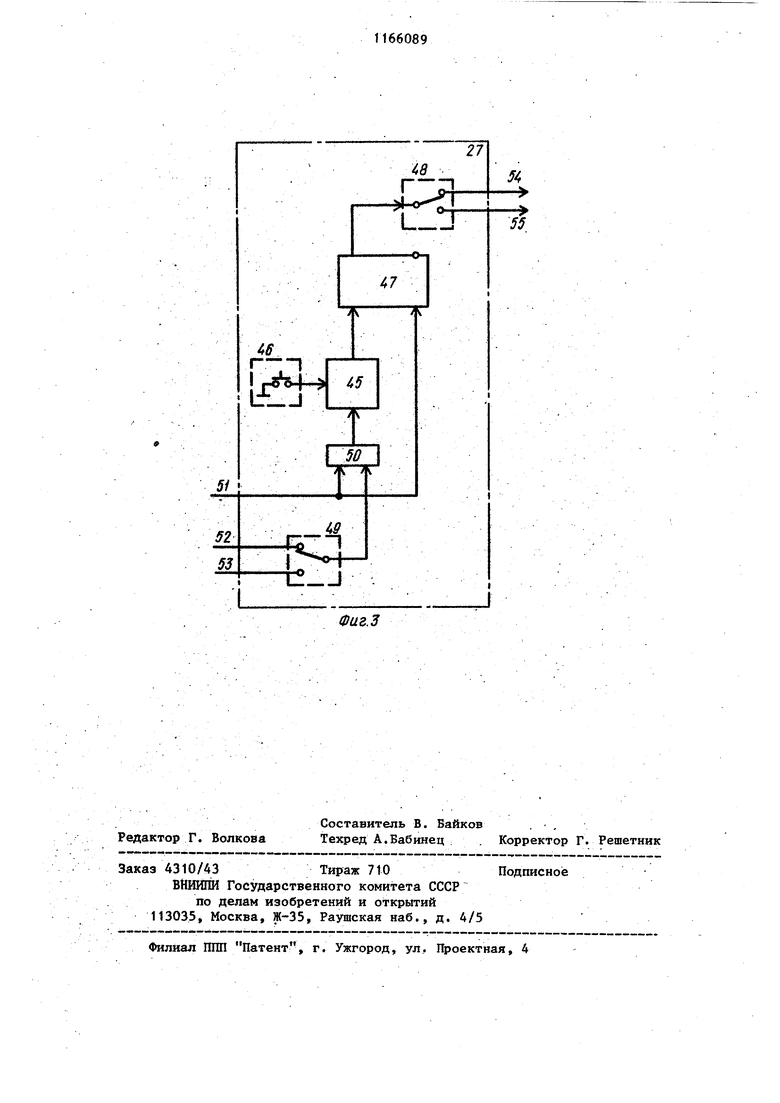

5 -подключен к выходу второго триггера, выход третьего коммутатора подключен к второму входу второго элемента Ник последовательному 5 информационному входу регистра промежуточных результатов, последовательный выход которого подключен к второму информационному входу .вто рого коммутатора, последовательный выход регистра коэффициентов подключен к его первому последовательному информационному входу и к второму входу четвертого элемента И, выход четвертого элемента И подключен к информационному входу второго блока преобразования в дополнительный код, выход которого подключен к второму,входу сумматора, п-й (п - разрядность.чисел) выход первого распределителя импульсов подключен к нулевому входу четверто го триггера и к второму входу пятого элемента И, выход которого подключен к нулевому входу второго триггера, выход элемента ИЛИ блока настройки подключен к вторым последовательным информационным входам регистра начальных значений и регистра коэффициентов, последовательный информационный вход, сдвига ющий вход и управляющий вход записи регистра сдвига блока формирования знака подключены соответственно к выходу сумматора, к выходу первого делителя частоты и к вьпсоду второго триггера, выход первого разряда регистра сдвига блока формирования зн ка является выходом знака генератора последовательности чисел и под ключен к разрешающему входу блока преобразования в дополнительный код выход коммутатора блока формирования знака подключен к разрешающему входу второго блока преобразования в дополнительный код, блок управления состоит из формирователя одиноч ных импульсов, триггера, элемента И и двух переключателей, причем вы ход первого переключателя блока управления подключен к первому входу элемента И, выход которого подключен к синхронизирующему входу формирователя одиночных импульсов, запускающий вход которого является управляющим входом занесения данны генератора последовательности чисел, а выход подключен к единичному входу триггера блока управления, выход триггера блока управления подключен к входу второго переключателя, второй.вход элемента И и ну левой вход триггера блока управле896ния подключены к первому выходу первого распределителя импульсов, первый и второй входы первого переключателя блока управления подключены к первому и второму потенциальным выходам второго распределителя им- . пульсов, первый и второй выходы второго переключателя блока управ- . ления подключены к управляющим входам записи регистра начальньпс значений и регистра коэффициентов соответственно. На фиг. IS показаны функциональные схемы генератора последовательности чисел, блока формирования знака и блока управления. Генератор последовательности чисел (фиг. 1) содержит регистр 1 функций, элемент 2 задержки, блок 3 преобразования в дополнительный код, коммутаторы 4 и 5, регистр 6 промежуточных результатов, сумматор 7, элемент И 8, коммутатор 9, блок 10 преобразования в дополнительный код, элементы И 11 и 12, выход 13 дополнительный числа, регистр 14 начальных значений, выход 15 знака, блок 16 формирования знака, регистр 17 коэффициентов, триггеры 18-20, элемент И 21, триггер 22, распрейелитель 23 импульсов, делители 24 и 25 частоты, элемент И 26, блок 27 управления, распределитель 28 импульсов, блок 29 настройки, состоящий из переключателей 30 и элемента ИЛИ-31, генератор 32 тактов. Блок 16 формирования знака (фиг. 2) содержит регистр 33 сдви- . га, сумматоры 34 и 35 по модулю два, коммутатор 36, группы переключателей 37 и 38, элемент НЕ 39, входы 40-43, подключенные к выходам сумматора 7, делителя 24 частоты, триггера 22 и первому потенциально- му выходу распределителя 23 импульсов соответственно, выход 44, Подключенный к разрешающему входу блока 10 преобразования в дополнительный код. . Блок 27 управления содержит формирователь 45 одиночных импульсов с кнопкой 46 запуска, триггер 47, переключатели 48 и 49, элемент И 50, входы 51-53, подключенные к .первому выходу 28 распределителя импуль ов к первому и второму потенциальным выходам распределителя 23 импульсов соответственно, выходы 54 и 55, 7 . подключенные к управляющим входам записи регистров 14 и 17. Генератор последовательности чисел работает следующим образом. Генератор 32 вьфабатывает импуль сы тактовой частоты f, которые последовательно проходят на п выходов распределителя 28 импульсов, (п разрядность чисел). Импульсы с первого выхода распределителя 28 поступают на вход распределителя 23 импульсов, имеющего два потенциальных и два импульсных выхода. Второй импульсHbrii выход распределителя 23 подключен к входу делителя 24 частоты на п-1. Делители 25 частоты имеют коэффициент деления N (число генерируемьге чисел последовательности в цикле), и период появления импульсов на его выходе Т 2п (п - 1) N/f равен длительнос ти цикла генерируемой последователь ности. : Функциональньй закон изменения чисел в последовательности определя ется рекуррентным соотношением Y; AY,., + BY;.,. (1) i 1, 2, ..., N, где Y;, Y ; - числа, генерируемые на 1-м и (i-1)-M цик лах работы распределителя 28; А и В - коэффициенты, определяющие закон изменения в соответствии с таблицей. Абсолютные значения начальн1)1х чисел YP J Y., и коэффициентов А, В в виде последовательных п-разрядньпс кодов (в п-х знаковых разрядах нули) предварительно записываются в регистр 14 начальньк значений и регистр 17 коэффициентов соответственно. Каждьй из регистров 14 и 17 п-раэрядный и хранит два п-разрядных числа. Первому числу соответствует сигнал (длительностью п тактов на первом потенциальном выходе распределителя 23, а второму числу на втором выходе. Первыми в регистры 14 и 17 записываются Y, и А, а затем Y(j и В. Разряды А (и аналогич но В, Y , YQ) набираются с помощью переключателей 30 блока 29 настройки и последовательно появляются на выходе элемента ИЛИ 31. При нажатии запускающей кнопки 46 (фиг. Зэ) в блоке 27 управления формирователь 9 45 вырабатывает одиночный импульс, синхронизируемый первым выходом распределителя 28 совместно с первым потенциальным выходом распределителя 23 - переключатель 49 замк-, нут на тину 52. S-триггер 47 переводится в единичное состояние до прихода следующего импульса на вход 51 с первого выхода распределителя 28. В результате на выходе триггера 47 формируется импульс длительностью п тактов, который через переключатель 48, замкнутый на шину 55, поступает на управляющий вход регистра 17 коэффициентов. Под действием этого импульса осуществляется запись последовательного п-разрядного кода в регистр 17с выхода элемента ИЛИ 31 в блоке 29 настройки. В отсутствие управляющего импульса последопательньш код циркулирует в регистре. Для записи чисел В, Y|, YQ требуется лищь установка переключателей 48 и 49 в соответствующие положения. Знаки чисел Y , Y набираются при помощи переключателей 37 (фиг. 2) в блоке 16 формирования знака и заносятся параллельным двухразрядным кодом в регистр 33 сдвига по сигналу управления на входе 42 от триггера 22 (каждьй из триггеров . . 18-22 - S-триггер) в начале калздого цикла формирования последовательности чисел. Для .набора знаков коэффициентов А и В используются переключатели 38. . Цикл формирования последовательности чисел согласно (1) начинается в момент появления импульса с выхода делителя 25, устанавливающего . триггер 22 в единичное состояние. Триггер 22 находится в единичном состоянии 2п-1 тактов и сбрасывается в нулевое состояние выходным сигналом элемента И 26. Единичный сигнал триггера 22 поступает на вход управления коммутатора 5, который подключает информационньй вход регистра 6 промежуточных результатов к выходу регистра 14 начальных значений функции. Завремя 2п-1 тактов двоичные коды абсолютных величин начальных значений функции YJJ и Y( под действием тактовых импульсов сдвигаются последовательным способом, начиная с 1Шадшего разряда, из регистра в регитр 6, который содержит 2п-1 разрядов. В случае единичного сигнала младшего разряда кода числа YO. элемент И 21 открывается в момент действия импульса на .первом выходе распределителя 28 импульсов. Выход ной импульс элемента И 21 устанавливает, триггер 19 в единичное .состояние, в котором он находится п тактов и сбрасывается в нулевое состояние импульсом первого выхода распределителя 28 импульсов. Едини ный сигнал с выхода триггера 19 под ключает с помощью элемента И 11 вход сумматора 7 к выходу регистра 17 коэффициентов. Под действием так товых импульсов последовательный дв ичный код коэффициента А через элемент И 11, блок 10 преобразования в дополнительный код и сумматор 7сдвигается, начиная с младшего разряда, в регистр 1 функций, который содержит п-1 разряд и дополняется до п разрядов элементом 2.задержки на такт. Аналогичным образом в следующие п тактов в случае единичного сигнала младшего разряда кода чи,сла У. триггер 19 устанавливается в единич ное состояние выходным сигналом элемента И 21, и двоичный код коэффициента В сдвигается, начиная с младшего разряда, с выхода регист-. ра 17 коэффициентов через элемент И 11 и блок 10 на вход сумматора.7 Блок 10 преобразования в дополнительный код в процессе передачи коэффициентов А и В управляется сиг налами блока 16 формирования знака. 8случае положительного знака произ ведений А УО и В Y, на разрешающем входе блока 10 действует нулевой .сигнал, и двоичные коды коэффициентов А и В пропускаются без изменения. Когда знак произведений и В У отрицателен, осуществляется преобразование в дополнительный код В конце каждого цикла преобразования блок 10 сбрасывается в исходное состояние по запрещающему входу сигналами первого выхода распределителя 28 импульсов. Спустя п тактов после начала цик ла генерации двоичньй код (прямой или дополнительньй) коэффициента А сдвигается с выхода регистра 1 функций через элемент 2 задержки, коммутатор 9 и элемент И 8 на первый вход сумматора 7, на второй вход которого в это время сдвигается двоичный код коэффициента В с выхода регистра 17 коэффициента через элемент И 11 и блок 10. Сумматор 7 суммирует последовательным способом прямые или дополнительные коды коэффициентов А и В, и двоичный код суммы записывается под действием тактовых импульсов в регистр 1 функций. Спустя 2п тактов после начала цикла генерации происходит сдвиг на один разряд двоичных кодов регистра 6 промежуточных результатов по отношению к двоичных кодам регистра 17 коэффициентов. Поэтому в (2 п + 1)-м такте на выходе регистра 6 действует сигнал второго разряда кода начального значения функции Уд. Этот сигнал проходит через коммутаторы 5 и 4 на вход элемента И 21, на другом входе которого в этот момент действует импульс первого разряда распределителя 28 импульса триггер 19 устанавливается в единичное состояние, в котором он подключает выход регистра 17 коэффициентов через элемент . И 11, блок 10 к входу сумматора 7. В это время триггер 18 устанавливается в единичное состояние импульсом второго выхода распределителя 23 импульсов. Триггер 18 находится . в единичном состоянии в течение . п-1 тактов и сбрасьфается в нулевое состояние импульсом п-го выхода распределителя 28 импульсов. Единичный сигнач 1фямого выхода триггера 18 переключает коммутатор 9 в состояние, в котором выход регистра 1 функции подключается через элемент И 8 к входу сумматора 7. В это время с выхода регистра 1 функций под действием тактовых импульсов сдвигается, начиная со второго разряда, двоичньй код алгебраической суммы произведений первых разрядов начальных значений функции на коэффициенты А Уд, + В У.,, . Таким образом, сумматор 7 спустя 2п тактов после начала цикла генерации осуществляет суммирование произведений коэффициента А на двоичную пе1эеменную второго разряда начального значения ункции с величиной А УЛ, + + В У-,( . С учетом сдвига величины A Y no отношению к величине A Y, В Y.,, на вмкоде сумматора 7 формируется последовательный двоичный код алгебраической суммы 2AY(j,2 + AYo.t + BY , который под действием тактовых импульсов сдвигается, в регистр 1 функции и через n тактов вновь поступает на вход сумматора 7 через элемент И 8, коммутатор 9 и элемент 2 задержки. Спустя Зп тактов после начала цикла генерации на выходе, регистра 6 промежуточных результатов действует сигнал, второго разряда числа Y. , который через коммутаторы 5 и 4 . . nocTynaet на вход элемента ,И 21. В случае единичного кода во втором разряде числа Y, элемент И 21 срабатьгоает по. импульсу первого выхода распределителя 28 импульсов и устанавливает триггер 19 в единичное состояние, в котором снимается блокировка элемента И 11. Двоичный код коэффициента В через элемент И 11 .и блок 10 сдвигается с выхода регистра 17 коэффициентов на вход сумматора 7, на другой вход которого с выхода регистра 1 функций через элемент 2 задержки, коммутатор 9 и элемент И 8 сдвигается двоичный код .величины 2AY( + AYo, + 1,1На выходе сумматора 7 формируется двоичный код величины 2AYo,2 2BY. + AYQJ+ BY,, который сдвигается по под действием тактовых импульсов в регистр 1 функций. - Аналогичным образом в регистре 1 функций за время 2пх (п-1) так. тов накапливается значение функции на первом цикле генерации согласно соотношению (1). Спустя 2п (п-1) тактов на вькоде делителя 24 частоты с коэффициен том делителя п-1 формируется импульс, который устанавливает триггер 20 в единичное состояние на время n тактов. Единичньй сигнал триггера 20 обеспечивает подключение выхода блока 3 преобразования в дополнительньй код через коммутаторы 5 и 4 к информационному входу регистра 6 и к входу элемента И 2. . . 8912 Под действием тактовых импульсов двоичньп код функции после первого цикла вычислений YJ сдвигается с выхода регистра 1 функций через элемент 2 задержки, блок 3, коммутаторы 5 и 4 в регистр 6 и через элемент И 12 на выход 13 числа. Блок 3 преобразователя в дополнительный код управляется сигналом, действующим на выходе 15 знака так, что прямой код, поступающий на его информационный, вход, проходит без изменения, а дополнительный код преобразуется в прямой код. Таким образом, на выходе блока 3 действует прямой код абсолютной величины нового значения функции YJ, который сдвигается на вы;сод 15 числа генератора последовательности чисел. Двоичный код абсолю.тного значения функции Y( записывается в регистр 6 вместо кода начального назначения Y.. , а в процессе сдвига в этом регистре за время 2п« (п-1) тактов двоичный код началь-. ньпс значений Y , сдвигается по отношению к двоичным кодам коэффициентов А и В на n разрядов и совпадает с коэффициентом В, а новое значение функции Y - с коэффициентом А.. . Во втором и всех последующих даклах генерации генератор последовательности чисел работает аналогичным образом, а на вьпсоде 13 числа через каждые 2п (n-t) тактов формируется последовательньй двоичньй код нового абсолютного значения функции Y , информацию о знаке ко- торой дает сигнал на выходе 15 знака. . Технико-экономические преимущества предлагаемого генератора порледовательности чисел по сравнению с известным заключается в расширении класса генерируемых последовательнрстей чисел со знакопеременным функциональным законом изменения, например тригонометрическим зако-. ном, наряду с возможностью генерации последовательности чисел со знакопостоянным функциональным законом изменения.

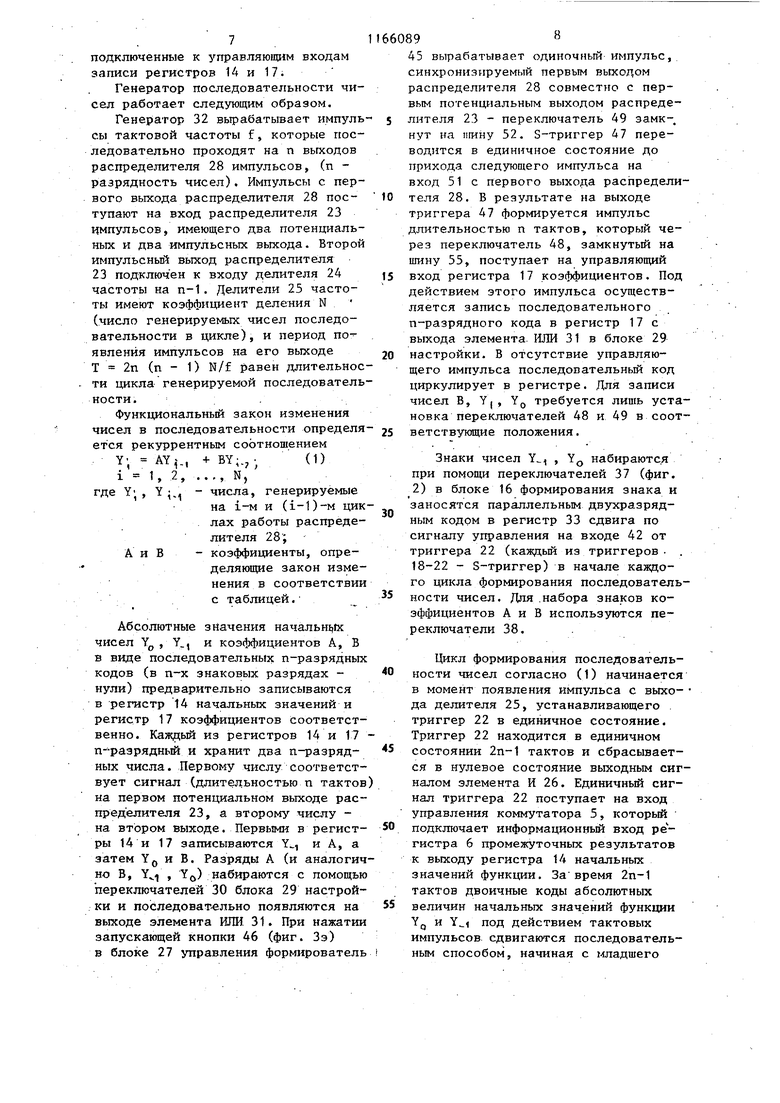

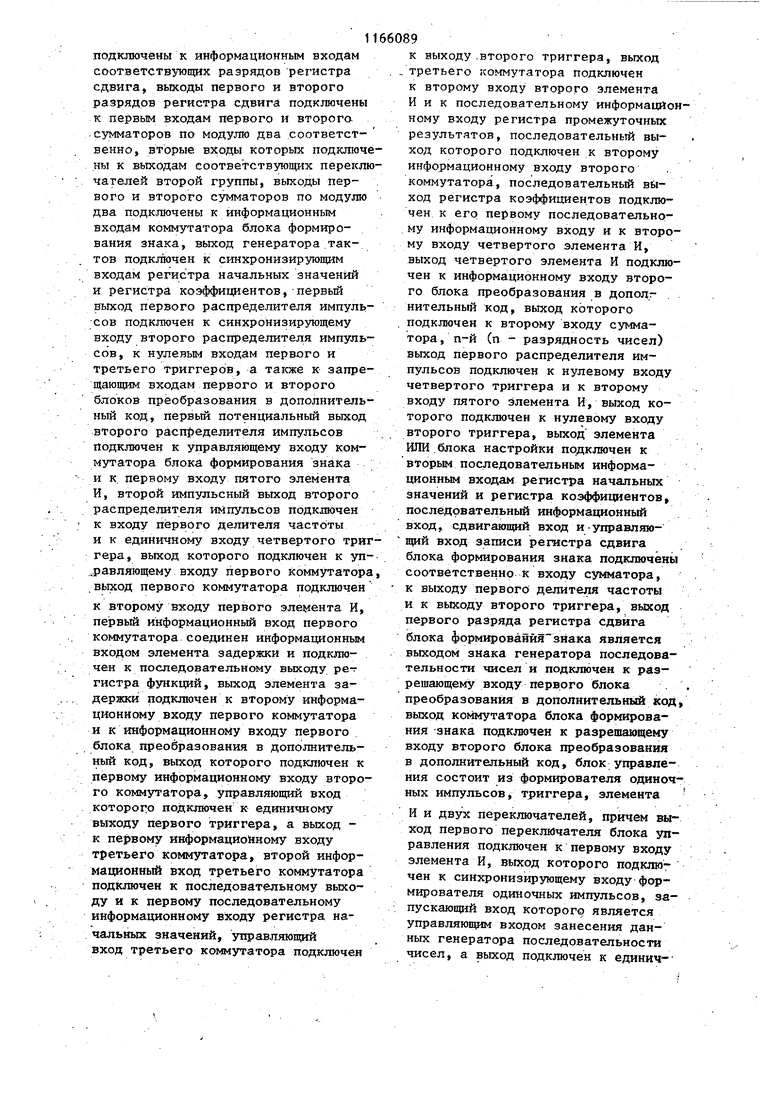

cSin (wx - cf )2Cos (wh)

a Sin (i« + cf ) -If b Cos (wx (f ) с Sh (ы,х - p)2ch. «fch) .-1

a Sh (cfcx i /i ) +, ..

.LI/ 4 n (.eLn)

+ bck («X fl )

2h,

-«(-r „,

ce Sin (wx - tp 2e Cos (wh)

2K.

Sin (wx i-u )+ 2e Cos (wh) «- BCos (wx - r ).

+ - t

-a i b (x-1)

Xl

ab

-ff

b-h|T

-«h

sh (ftx) 2e ch (ph)

-1 . с Sin (- cf ) с Sin (-wh - (p )

+ + bSin (-wht

-1

Sin ( i cp +± tf + arctg b/a)

+ arctg b/a)

ash (- ft) + ash (-xxh /5 ) + + bch (i /3 ) + bch (-«ih Я)

- )

гЬ„.

.1

cSin (i (f )ce Sin (-wh

let)

-e (i{f)+ clASin (-wh i

+ В Cos (-tf) -q) + BCos (wh-Ч)

-1ta b

- a т 2b

0

ab

0 .

(-/Sh)

.

0 с sh (- /5 )c. sh ( - ft )

Фиг.З

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| Способ металлизации диэлектрических подложек | 1970 |

|

SU674680A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Генератор последовательности чисел | 1981 |

|

SU999032A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-07—Публикация

1983-08-15—Подача