Изобретение относится к автоматике и вычисли1ельной технике и может быть использовано при построении преобразователей в специализированных вычислительных машинах. Известен преобразователь двоич.ного кода в двоично-десятичный код, содержащий су 15матор, блок анализа знака и блок управления 1. Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь двоичного кода в позиционный код со смешанным основанием,содержащий бло формирования эквивалентов, сумматор блок анализа знака, блок управления и генератор импульсов С2. Недостатки известных преобразователей состоят в относительно низком быстродействии и невозможности преобразования двоичного кода в код с основаниями, равными числам Фибоначчи-. Целью изобретения является повыше ние быстродействия и расширение функ циональных возмоушостей,.заключающих ся в преобразовании двоичного кода в позиционный код с основаниями,равными числам Фибоначчи. Поставленная цель достигается тем, что в преобразователь двоичного /кода в позиционный код со смешанным основанием, содержащий блок формиро- вания эквивалентов, сумматор, блок анализа знака, блок управления и генератор импульсов, выход которого соединен с тактовым входом блока управления, йотенциальные входы положительного и отрицательного знака которого соединены с потенциальными выходами соответственно положительного и отрицательного знака блока анализа знака, первый тактовый выход блока управления соединен с тактовым входом блока формирования эквивалентов,второй тактовый выход блока управления соединен с тактовым входом блока анализа знака, входы положительного и отрицательного знаков которого соответственно соединены с выходами полоясительнопо и отрицательного знака сумматора, первый и второй информационные входы которого соответственно соединены с первым и вторым информационными выходс1ми блока формирования эквивалентов,введены сдвиговый (Регистр, СДВИГОВЫЙ регистр кода Фибо;наччи и элемент задержки, вход которого соединен с импульсным выходом 1отрицательного знака блока анализа знака, иютульсньв1 входом отрицательного знака блока управления и входом младшего разряда сдвигового регистра, выход злемента задержки соединен со входами сдвига на два разряда сдвигового регистра и сдвигового регистра кода Фибоначчи, входы сдвига на один разряд которых соединены с импульсным входом положительного знака блока анализа знака и импульсным входом положительного знака блока управления, вход окончания преобразования которого соединен с выходом старшего разряда сдвигового регистра кода Фибоначчи ивходом окончания преобразования блока анализа знака, разрешающий выход блока управления соединен с разрешающим входом блока формирования эквивалентов, входы сложения и вы,читания которого соеданены соответственно с выхода1/1и сложения и вычита ния блока управления, вход пуска которого является входом пуска преоб разователя, коммутирующий клход блок анализа знака соединен с коммутирующим входом блока управления. При этом в преобразователе блок управления содержит два триггера, че тыре элемента И, два элемента задержки и два элемента ИЛИ, выходы ко тррых соединены соответственно с еди ничным и нулевым входами первого триггера, нулевой выход которого явл ется разреш;а101аим выходом блока управ ления и соединен с первым входом пер вого элемента И, второй вход которог соединен с першлм входом первого эле мента ИЛИ и через пергалй элемент задержки - с выходом второго элемента соединенного с первым тактокш выходом блока управления и першами входами третьего и четвертого элементов и, вторые входы которых являются потенцисшьными входгикш соответственно положительного и отрицательного знаков блоков управления, а выходя являются соответственно выходами сложения и вычитания блока управления, первый и второй входы второго элемента ИЛИ являются ЙМПУЛЬСНЬШИ ВХОдами соответственно положительного и отрицательного знаков блока управления, второй вход первого з лемента .И через второй элемент задержки соединен с коммутирунадим входом блока управления, а третий вход первог элемента ИЛИ является входом оконча ния преобразования блока управления и соединен с нулегаым входом .второго триггера, единичный вход которого является входом пуска блока управле ния, а единичный выход второго триггера .соединен с первым входом второ го элемента И, второй вход которого является тактов з м входом блока управ ления, выход первого элемента И является торым тактовым выходом блока управления. Крогле того, в преобразователе блок формирования эквивалентов содержит регистр старшего разряда, рёгиртр разности, вычитатель, пять посУ1едова-г тельно соединенных элементов задержки, шесть групп элементов И и преобразователь прямого кода в :Обратный, выход которого является первым информационным выходом блока формирования эквивалентов, а входы соединены с выходами элементов И первой группы, первые входы которой являются входами илчи.тания блока формирования эквивалентов, вторые входы соединены с выходами регистра старшего разряда и с первыми входами элементов И второй, третьей и четвертой групп, вторые входы элементов И второй группы являются входом сложения блока форкирования эквивалентов, а третьи входы э: уементов И первой и второй групп объединены и являются входом разрешения блока формирования эквивалентов, вход перво го элеме нт а з адержки я вляется тактовым входом формирователя экви-:валентов и соединен со вторыми входами элементов И третьей группы и тактовым входом регистра разности, информационные входы которого соединены с выходами элементов И пятой группы, первые BKOJOU которых соединены с выходом первого элемента задержки, а вторые входы элементов И пятой группы соединены с выходами вычитания, тактовый вход которого соединен с выходом второго элемента задержки, выходов третьего, четвертого и пятого элементов задержки соединены соответственно со вторыми Bxonatm элекюнтов И четвертой группы, тактовым,входом регистра старшего разряда и первыми входами элементов И шестой группы; вторые входы которых соединены с выходаки регистра разности, а выхоДФа соединены с информационными входами регистра стар.шего разряда, выходы элементов И третьей и четвертой групп соединены соответственно b первым и втррьш входами вычитателя/ выходы которого соединены со вторыми входакю элементов И пятой группы. Причем в преобразователе блок анализа знака содержит триггер знака, ТРИ элемента И, элемент ИЛИ и элемент задержки, через который тактовый вход блока анализа зн|ака соединен с первыми входами первого и второго элементов И, вторые входа которых являются соотв«ётственно входами положительного и отрицательного знаков блока анализа знака, а выходы первого и второго элементов И являются импульсными Выходами соответственно положительного и отрицательного знаков блока анализа знака и соединены.

с первыми входами третьего элемента. И и элемента ИЛИ, второй .вход которого является входом окончания преобразования блока анализа знака, а выход элемента ИЛИ соединен с нулеилм входом триггера знака, единичный вход которого соединен с выходом первого элемента И, а единичный и нулевой выходы триггера знака являются соответственно потенциальными выходами соответственно положительного и отрицательного знака блока анализа значка, причем единичный выход триггера знака соединен со .вторым входом третьего элемента И выход которого является коммутационным выходом блока анализа знака.

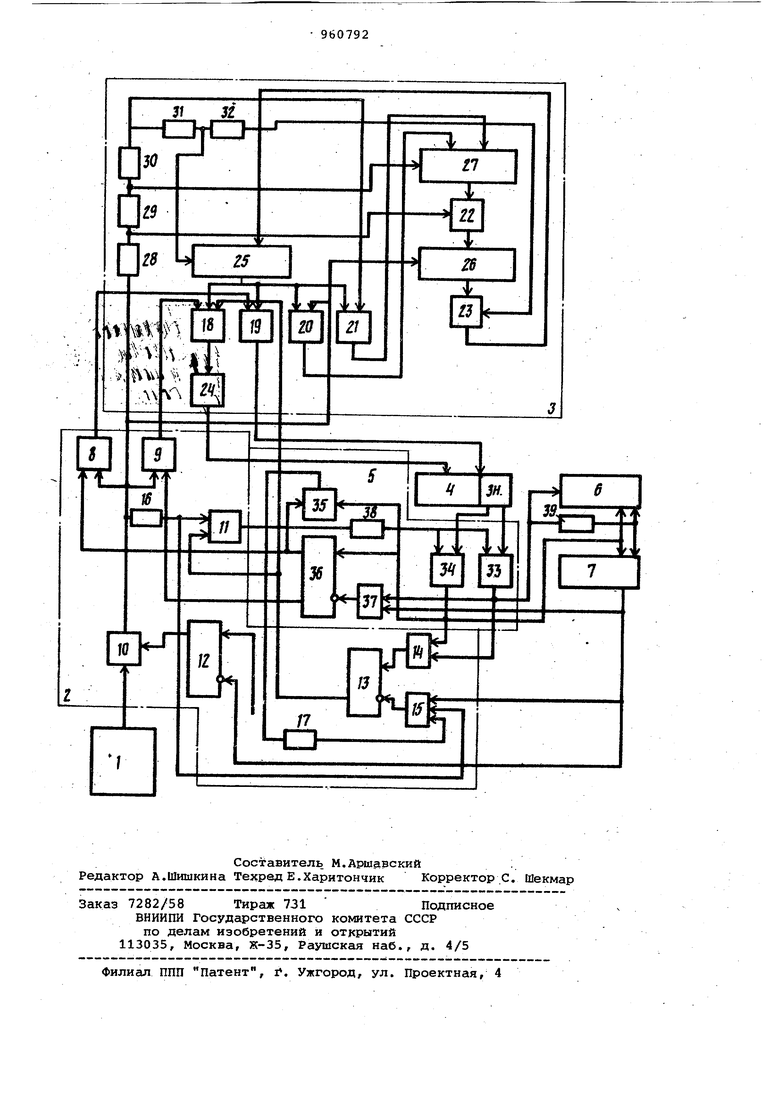

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, блок 2 управления, блок 3 формирования эквивалентов, сумматор 4, блок 5 анализа знака, сдвиговый регистр 6 и сдвиговый регистр 7 кода Фибоначчи. БЛОК 2 управления состоит из четырех элементов И 8-11, двух триггеров 12-13,. двух элементов ИЛИ 14-15 и элементов 16 и 17 3 адержки.

БЛОК 3 формирования эквивалентов, предназначенный для формирования фибоначчиевых весов разрядов, состоит из шести групп элементов И 18-23, преобразователя 24 прямого кода в обратный, регистра 25 старшего рд;зряда и регистра 26 разности, вычитател 27 и элементов 28-32 задержки.

Блок анализа знака, предназначенный для определения знака остатка, полученного при вычитаний фибоначчиевого эквивалента из npeo6pa3yeN rb числа, состоит из трех элементов И 33-35, триггера 36 знака, элемента ИЛИ 37 и элекюнта 38 задержки. Вход младшего разряда сдвигового регистра 6 соединен через элемент 39 задержки со входом сдвига на разрядi

Предлагаемое устройство работает следующим образом.

Предварительно на сумматор 4 накапливающего типа заносится преобразуемое число, на регистр 25 - вес старшего фибоначчиевого разряда q и на вычитатель 27 - вес q,j, в младший разряд сдвигового регистра 7 заносится 1. Остальные триггеры и регистры находятся в нулевом состоянии. При поступлении сигнала начала преобразрванияг триггер 12 устанавливается в 1 и первый тактовый им-пульс с генератора 1 импульсов чере элемент И 10 и:И 9 поступает в блок 3 формирования эквивалентов. В результате фибоначчкевый вес q, старшего разряда через группу элементов И 18 и преобразователь 24 прямого кода в обратный поступает в сумма1Рор 4, где ПРОИСХОДИТ его вычитание из преобразуемого числа. Одновременно с этим вес q. через группу элементов И 20 поступает в вычитатель 27, где происходит образование фибоначчиевого веса qi следующего младшего разряда, согласно правилу образования весов в фибоначчиевой системе счисления: q., qi+-i- Я,

Этот вес через группу элементов И 22 заносится на регистр 26, который

0 предварительно обнуляется. После этого происходит обнуление вычитателя 27 и на него с регистра 25 через группу элементов И 21 заносится фибоначчиевый вес , послечего на предварительно сброшенный в ноль регистр

5 25 через группу элементов И 23 переписывается фибоначчиейнй вес q. следующего младшего разряда с регистра 26.

Этот же тактовый иктульс через

0 элемент И 11 поступает в блок 5 анализа знака. Если в результате вычи-. тания фибоначчиевого веса q,- знак остатка получается положительный, шшульс через элементы И 33 и 1ШИ 14

5 устанавливает триггер 13 в единичное состояние и записывает единицу :в младший разряд сдвигового регистра 6, после чего осуществляется сдвиг содержимого регистров 6 и 7 на два

0 разряда. В данном случае при образо-. вании фибоначчиевого кода использует|ся основное контрольное свойство нормальной формы, согласно которому в двух соседних разрядах фибоначчиег5вого числа не могут быть две единицы, т.е. если в данном разряде фибоначчиевого кода записана 1, то в соседнем заведомо должен быть Ь.

По второму тактовому импульсу

0 происходит форкшрование фибоначчиевого веса qi-7 установка зв О , триггера 13, который, находясь в единичном состоянии, блокирует прохождение импульса через элемент И 11

5 и блок анализа знака и закрывает группы элементов И 18 и 19. Если в результате вычитания фибоначчиевого веса q,- знак остатка папучаетс;я отрицательный, т.е. преобразуемое число меньше данного веса, то импульс через

0 элементы И 34 и ИЛИ 14 устанавливает в 1 триггер 13, осуществляет сдвиг на один разряд содержимого регистров 6 и 7 и устанавливает в 1 триггер 36 знака.Но второму тактовому

5 ПРОИСХОДИТ формирование фибоначчиевого веса q, и установка в О триггера 13. Третий тактовый импульс проходит через элемент И 8 (так как триггер 36 находится в еди0;ничном состоянии ) в блок формирова:Ния фибоначчиевых эквивалентов и вес cj,j через группу элементов И 19 поступает в сумматор 4, где происходит его сложение с отрицательным остат5ком. В данном случае преобразование происходит без восстановления остат ка,т.е. если(, где А - преобразуемое число, то A-qv-, (A-q ) + q,--2, так как qf q. A-qt A-qiV-t- 44-1 Если в результате сложения вновь получается отрицательное число, импульс с элемента И 35 сдвигает содержимое регистров 6 и 7 на один разряд, устанавливает триггер 13 , проходит через элемент И 35, так ка триггер 36 знака находится в едйнич нЪм состоянии, элемент ИЛИ 15 и ус танавливает триггер 13 вновь в нуле вое состояние. Таким образом очеред ной тактовый импульс проходит ив блок формирования фибоначчиевого эквивалента и в блок анализа знака,На сумматоре 4 происходит вычисление следую&дего остатка. A-q..,j (A-q) + q-,,. Если в.сумматоре 4 получается положительное число, происходит устано ка в О триггера 36 знака через эле мент ИЛИ 37, в 1 триггера 13, заносится 1 в младший разряд сдвигового регистра б и осуществляется сдвиг содержимого регистров б и 7 на два разряда. Единица в старшем разряде сдвигового регистра 7 сигнализирует об окончании преобразования. Осуществляется установка в О триггеров 12 и 13 и триггера знака и тем самым блокируется прохождение очередного тактового импульса с ге нератора.. На сдвиговом регистре 6 за писан фибоначчиевый код, соответствуадий преобразуемому двоичному числу. Элементы задержки необходима (для синхронизации работы преобразователя.. В результате расширяются функциональные возможности преобразователя за счет преобразования двоичной системы счисления в фйбоначчиевую ,что .позволяет использовать в различных узлах ЦВМ фибоначчиевые коды, котоjaae обладают нулевой ошибкообнаруживающей способностью по сравнению с двоичной системой счисления, что ведет к улучшению контроля ЦВМ и повышается быстродействие преобразователя, так как преобразование осуществляется без восстановления остатка. Кроме того, в предложенном устрой стве преобразование двоичного кода в фибонач;чиевый осуществляется с большим быстродействием за счет использования двоичных сумматоров вмес то фибоначчиевых , быстродействие которых для 40-разрядных кодов приблизительно в 10 раз ниже. Формула изобретения 1. Преобразователь двоичного кода в позиционный код со смешанным-основанием, содержащий блок формирования эквивалентов, сумматор, блок анализа знака,блок управления и генератор импульсов, выход которого соединен с тактовым входом блока управления, потенциальные входа положительного и отрицательного знака которого соединены с потенциальными выходами соответственно положительного и отрицательного знака блока анализа знака, первый тактовый выход блока управления соединен с тактовым входом блока формирования эквивалентов, второй тактовый выход блока управления соединен с тактовым входом блока анализа знака, входы положительного и отрицательного знаков которого соответственно соединены с выходами положительного и отрицательного знака сумматора, первый и второй информацион.ные входы которого соответственно соединены с первым и вторым информационными выходами блока формирования эквивалентов, отличаювд и и с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей, заключающихся в преобразовании двоичного кода в позиционный код с основаниями, равными числам Фибоначчи, в него введены сдвиговый регистр, сдвиговый perгистр кода Фибоначчи и элемент за;держки, вход которого соединен с импульсным выходом отрицательного знака блока анализа знака, импульсным входом отрицательного знака блока управления и входом мцадачего разряда сдвигового регистра, выход элемента задержки соединен со входами сдвига на дйа разряда сдвигового регистра И сдвигового регистра кода Фибоначчи, входы сдвига на один разряд которых соединены с импульсным входом положительного знака блока анализа знака и импульсным входом положительного знака блока управления, вход окончания преобразования которого соединен с выходом старшего разряда сдвигового регистра кода Фибоначчи и входом окончания прео разойания блока анализа знака, разрешающий выход блока управления соединен с разрешающим входом блока формирования эквивалентов, входы сложения и Вйчитания которого соединены соответственно с выходами сложения и вычитания блока управления, вход пуска которого является входом ПУСка преобразова:теля, коммутирующий выход блока анализа знака соединен с кокплутирующим входом блока управления. 2. Преобразователь по п. 1, о т л и ч а ю щ и и с я тем, что, в нем блок управления содержит два триггера, четыре элемента И, два элемента задержки и два элемента ИЛИ, выходы которых соединены соответственно с единичным и нулевым входами первого триггера, нулевой выход которого является разрешающим выходом блока управления и соединен с первым входом первого элемента И, второ вход которого соединен с первым входом первого элемента ИЛИ и через первый элемент задержки - с выходом второго элемента И, соединенного с первым.тактовым выходом блока управления, и первыми входами третьего и четвертого элементов И, вторые вхо ды которых являются потенциальными входами соответственно положительног и отрицательного знаков блока управления, а выходы являются соответственно, выходами сложения и вычитания блока управления, первый и второ входы второго элемента ИЛИ. являются импульсными входами соответственно положительного и отрицательного знаков блока управления, второй вход. первого элемента ИЛИ через втЬрой элемент задержки соедин ен с коммутирующим входом блока управления, а третий вход первого элемента ИЛИ является входом окончания преобразования блока управления и соединен с нулевым входом второго триггера, единичный вход которого является входоМ пуска ,блока управления, а единичный выход второго триггера соединен с первым входом второго элемента И, второй вход которого является тактовым входом блока управления, выхрд первого элемента И является вторым тактовым выходом блока управления. 3. Преобразователь по пп. 1 и 2, отличающийся тем, что в нем блок формирования эквивалентов содержит регистр старшего разряда регистр разности, вычитатель, пять последовательно соединеиньгх элементов задержки, шесть групп элементов и преобразователь прямого кода в обратный, выход которого является первым информационным выходом блока формирования эквивалентов, а входы соединены с выходами элементов И пер вой группь, первые входы которой являются входами вычитания блока формирования эквивалентов, вторые входы соединены с выходами регистра старшего разряда и с первыми входами эле ментов И второй, третьей и четвертой групп, вторые входы элементов И группы являются входом сложения блока формирования эквивалентов, а третьи входы э.льментов И первой и второй групп объединены и являются входом разрешения блока фор мирования эквивалентов, вход первого элемента задержки является тактовым входом формирователя эквивалентов и соединен со вторыми входами элементо И третьей группы и тактовым входом регистра разности, информационные входы которого соединены с выходами элементов И пятой группы, первые входы которых соединены с выходом первого элемента задержки, а вторые входы элементов И пятой группы соединены с выходами вычитания, тактовый вход которого соединен с выходом второго элемента задержки, выходы третьего и четвертого и пятого элементов задержки соединены соответственно со вторыми вхрдами элементов И четвертой группы, тактовым входом регистра старшего разряда и первыми входами элементов И шестой группы, вторые входы которых соединены с выходаг/ш регистра разности, а выходы соединены с информационными входами регистра старшего разряда, выходы элементов И третьей и четвертой групп соединены соответственно с первым и вторым входами вычитателя, выходы которого соединены со вторыми входами элементов И пятой группы. 4. Преобразователь по пп. 1-3, отличающийся тем, что в нем блок анализа знака содержит триггер, знака, три элементачИ, элемент ИЛИ и элемент задержки, через который тактовый вход блока анализа знака соединен с первыми входами первого и второго элементов И, вторые входы которых являются соответственно входами положительного и отрицательного знаков блока ангшиза знака, а выходы первого и второго элементов И являются импульсными входами соотв тственно положительного и отрицательного знаков блока анализа знака и соединен с первыми входами третьего элемента И и элемента ИЛИ, второй вход которого является входом окончания преобразования блока анализа знака, а выход элемента ИЛИ соединен с нулевым входом триггера знака,единичный вход которого соединен с выходом первого элемента И, а единичный и нулевой выходы триггера знака являются соответственно потенциальными выходс1ми соответственно положительного и отрицательного знака блока анализа знака, причем единичный выход триггера знака соединен со вторым входом третьего элемента И, выход которого является коммутирукадим выходом блока анализа знака. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 437069, кл. G Об F 5/02, 1972, 2.Авторское свидетельство СССР № 720424, кл. G 06 F 5/02, 1975.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в позиционный код со смешанным основанием | 1980 |

|

SU945860A1 |

| Устройство для контроля @ -кодов Фибоначчи | 1984 |

|

SU1203711A1 |

| "Преобразователь кода Фибоначчи в код "золотой" пропорции" | 1990 |

|

SU1783616A1 |

| Преобразователь кодов | 1988 |

|

SU1552380A1 |

| Преобразователь числа в модулярный код | 1987 |

|

SU1444961A1 |

| Устройство для нормализации кодов Фибоначчи | 1980 |

|

SU951291A1 |

| Преобразователь кодов | 1986 |

|

SU1578813A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР КОДОВ ФИБОНАЧЧИ | 1993 |

|

RU2047898C1 |

| Преобразователь кодов | 1986 |

|

SU1438008A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

Авторы

Даты

1982-09-23—Публикация

1980-12-02—Подача