I

Устройство формирования адресов для записи в ОЗУ ординат гистограмм статистических характеристик случайных процессов может применяться в анализаторах случайиых процессов.

При снятии характеристик распределения случайных процессов необходимо фиксировать частость, с которой случайная величина принимает то или иное значение. Если необходимо исследовать одновременно несколько вероятных характеристик одного и того же процесса, то целесообразно для их фиксации иснользовать небольшое ОЗУ. При этом для каждой характеристики отводится некоторая область памяти (20-50 ячеек), каждая ячейка которой соответствует определенному численному значению случайных величиц, и при каждом измерении случайной величины число, хранящееся в соответствующей ячейке, увеличивается на единицу. В результате после цикла измерений в ячейках памяти окажутся занисаппымИ числа, показывающие сколько раз случайная величина нринимала то или иное значеиие. Делеиием этих чисел па общее число измерений получают распределение частостей, которое является оценкой для распределения вероятностей изменения случайной величины. Нанример, при снятии характеристики распределения числа ошибок в семиэлементном знаке используется восемь ячеек памяти и при приеме знака, например, с тремя ощибками, прибавляется единица к числу в третьей ячейке, а при приеме безощибочного знака - к числу в пулевой ячейке. В этом случае поиск соответствующей ячейки осуществляется довольно просто.

Однако часто большой диапазон изменений случайной величины заставляет переходить к группированным выборкам. Например, при измерении числа ошибок в блоках д„тино1{ до

500 элементов можно в первой группе (ячейке ОЗУ) фиксировать все испытания с числом ошибок от нуля до девяти, во второй - от десяти до пятидесятн и т. д. В этом случае для автоматическо записи результата измерения

в ячейку (фактически для определения адреса этой ячейки) потребуется специальная дешифрирующая схема, которая хранить значения групповых границ и в зависимости от конкретного измерения случайной величины формировать соответствующий адрес в ОЗУ.

Таким образом, адрес является некоторой сложной функцией от установленных групповых границ п от значения случайной величины.

Эту функцию можно реализовать схемой дешифратора с регистрами, но только для конкретных грунповых границ. Любое изменение этих граннц потребует внесения в схему дешифратора большого числа переключательных

элементов. В то же время необходимость такого изменения в нодавляющем большннсгве случаев очевидна. Нанример, нри анализе статических свойств дискретного канала связи измеряемый нараметр может изменяться в нределах от нуля до семи для числа ошибок в знаках н от нуля до десяти для интервалов между ошибками.

В известном устройстве, содержащем делитель частоты, счетчики неисках енных интервалов, буферные накопители и регистрирующие устройства, установлены фиксированные границы грунповых интервалов. Вследствие этого известное устройство обладает следующими недостатками: использование счетчиков затрудняет получение большого числа грунновых интервалов и, следовательно, ограничивает степень правдоподобия получаемой статистической характеристики; наличие фиксированных грунновых интервалов не позволяет использовать известное устройство для снятия характеристик, отличающийся от характеристики безошибочных интервалов масштабом измеряемого нараметра.

В нредлагаемом устройстве при изменении групповых границ все необходнмые переключения в схемиой части дешифратора производятся автоматически одним пакетным переключателем, связанным с дешифратором. Предлагаемая схема позволяет устанавливать групповые границы в логарифмическом масштабе с Коэффициентом два (каждый последующи интервал вдвое больше предыдущего) и делить групповой интервал на подгруппы в линейном масштабе.

Установкой различного режима можно менять соотношение логарифмической и линейной частей.

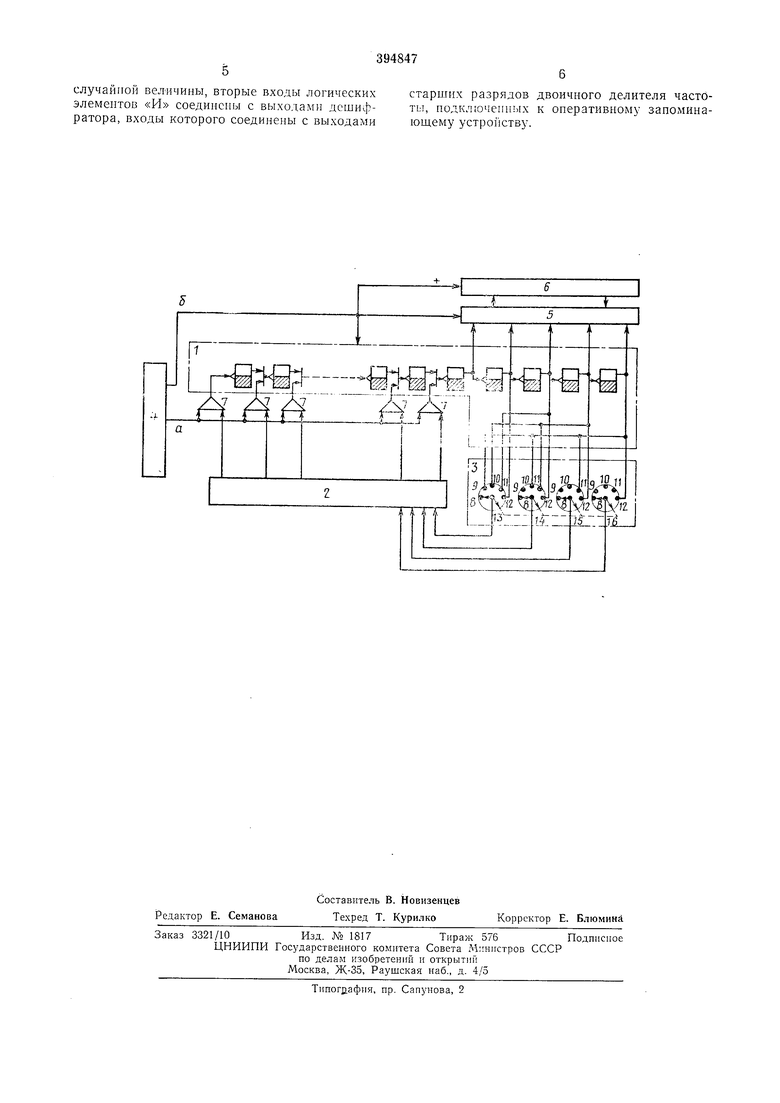

Сущность изобретения состоит в том, что устройство содержит логические элементы «И, подключенные выходами ко входам младщих разрядов двоичиого делителя частоты и соединенные первыми входами с выходом датчика случайной величины. Вторые входы логических элементов «И соединены с выходами дешифратора, входы которого соединены с выводами старших разрядов двоичного делителя частоты, подключенных к оператнвиому запоминающему устройству.

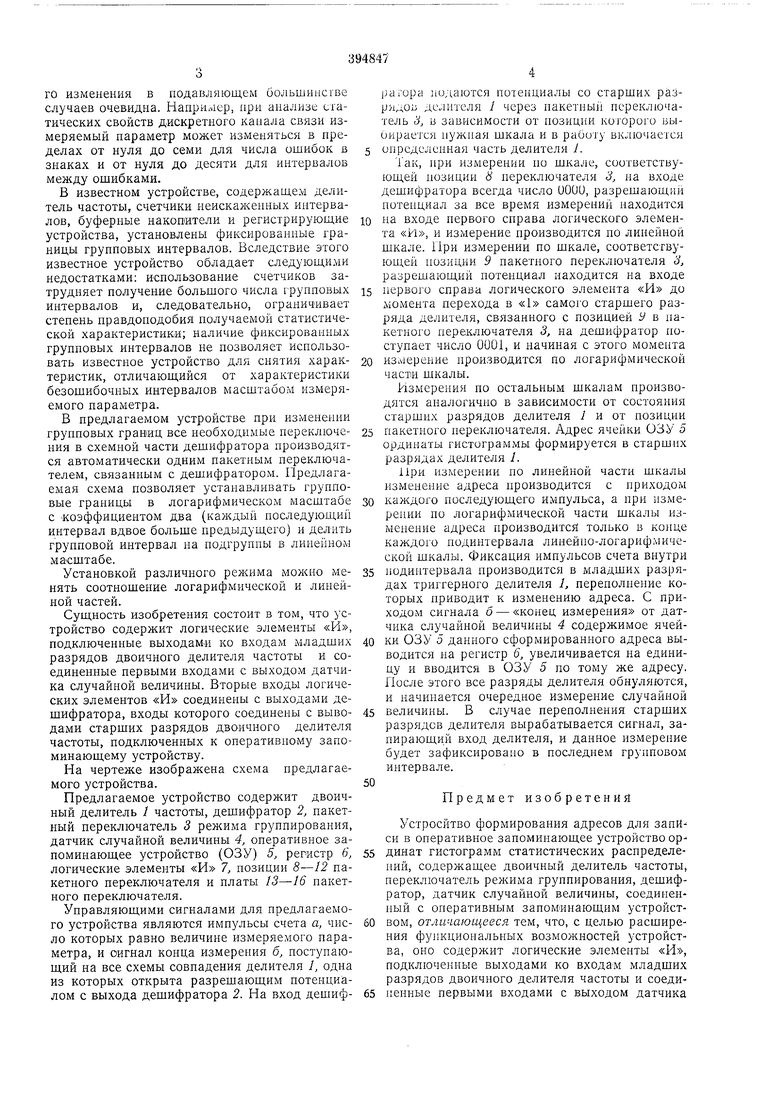

На чертеже изображена схема предлагаемого устройства.

Предлагаемое устройство содержит двоичный делитель 1 частоты, дешифратор 2, пакетный переключатель 3 режима группирования, датчик случайной величины 4, оперативное запоминающее устройство (ОЗУ) 5, регистр 6, логические элементы «И 7, позиции 8-12 пакетного переключателя и платы 13-16 пакетного переключателя.

Управляющими сигналами для предлагаемого устройства являются импульсы счета а, число которых равно величине измеряемого параметра, и сигнал конца измерения б, поступающий на все схемы совпадения делителя 1, одна из которых открыта разрешающим потенциалом с выхода дешифратора 2. На вход дешифрагора подаются потенциалы со старшнх разpHAO i делителя 1 через пакетньп переключатель 3, Б зависимости от позиции которого выоирается нужная шкала и в работу включается определенная часть делителя У.

1 ак, нри измерении по шкале, соответствующей позиции i; переключателя 3, на входе дешифратора всегда число 0000, разрешающий потенциал за все время измерений находится

на входе нервого справа логического элемента «И, и измерение производится ио линейной шкале. При измерении по щкале, соответствующей позиции 9 пакетного переключателя 3, разрешающий потенциал находится на входе

нервого справа логического элемента «И до момента перехода в «1 самого старщего разряда делителя, связанного с позицией У в пакетного переключателя 3, на дешифратор поступает число 0001, и начиная с этого момента

измерение производится но логарифмической части шкалы.

Измерения но остальным шкалам производятся аналогично в зависимости от состояния старших разрядов делителя 7 и от позицнн

пакетного переключателя. Адрес ячейки ОЗУ 5 ординаты гистограммы формируется в старшнх разрядах делителя 1.

При измерении по линейной части шкалы изменение адреса производится с приходом

каждого носледующего импульса, а нри измерении но логарифмической части щкалы изменение адреса производится только в конце каждого нодинтервала линейно-логарифмической шкалы. Фиксация импульсов счета внутри

нодинтервала нроизводится в младших разрядах триггерного делителя 1, переполпение которых приводит к изменению адреса. С приходом сигнала б - «конец измерения от датчика случайной величины 4 содержимое ячейки ОЗУ 5 данного сформированного адреса выводится на регистр 6, увеличивается на единицу и вводится в ОЗУ 5 по тому же адресу. После этого все разряды делителя обнуляются, и начинается очередное измерение случайной

величины. В случае переполнения старщих разрядов делителя вырабатывается сигнал, занирающий вход делителя, и данное измерение будет зафиксировано в последнем групповом интервале.

Предмет изобретения

Устросйтво формирования адресов для записи в оперативное запоминающее устройство ординат гистограмм статистических распределений, содержащее двоичный делитель частоты, переключатель режима группирования, дешифратор, датчик случайной величины, соединенный с оперативным заноминающим устройством, отличающееся тем, что, с целью расширения фу кциональных возможностей устройства, оно содержит логические элементы «И, подключенные выходами ко входам младших разрядов двоичного делителя частоты и соедипенные первыми входами с выходом датчика

случайной величины, вторые входы логических элементов «И соединегнм с выходами дешифратора, входы которого соединены с выходами

старших разрядов двоичного делителя частоты, подключенных к онеративыому запоминающему устройству.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

| Устройство контроля качества часовых механизмов | 1988 |

|

SU1569799A2 |

| Устройство для приема дискретной информации | 1989 |

|

SU1693735A1 |

| УСТРОЙСТВО ГРУППОВОГО ВВОДА ИНФОРМАЦИИ с ПЕРФОКАРТ В ЭЛЕКТРОННУЮ ВЫЧИСЛИТЕЛЬНУЮМАШИНУ | 1966 |

|

SU179991A1 |

| Запоминающее устройство с исправлением ошибок при считывании информации | 1976 |

|

SU607281A1 |

| Анализатор законов распределения | 1979 |

|

SU960845A1 |

| Имитатор ошибок двоичных кодов параметров | 1978 |

|

SU767744A1 |

| Устройство контроля качества часовых механизмов | 1986 |

|

SU1332257A1 |

| УСТРОЙСТВО ДЛЯ ПРОГНОЗИРОВАНИЯ СЛУЧАЙНЫХ СОБЫТИЙ | 2020 |

|

RU2763126C1 |

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

Авторы

Даты

1973-01-01—Публикация