I,

Изобретение относится к области ядерной электроники и, в частности, к многоканальным измерителям статистически распределенных во времени импульсов.

Известны многоканальные измерители скорости счета импульсов, содержащие таймер, .коммутатор каналов, коммутатор диапазонов, устройство управления, последовательно соединенные селектор и регистр числа, причем параллельно входам селектора включены входы регистра адреса, подключенного через запомин1аюш,ее устройство к регистру числа, а к входам селектора через схемы «И подключены измеряемые каналы. Однако такие измерители обладают значительной погрешностью.

С целью уменьшения погрешности измерения в предлагаемом измерителе другие входы каждой схемы «И соединены раздельно с двумя триггерами, входы первого триггера подключены соответственно к выходу устройства управления и через ключ к выходу введенного дешифратора, соединенного с частью отводов регистра числа, входы второго триггера порознь соединены с устройством управления и таймером через (последовательно включенные схемы «ИЛИ и элементы совпадений, вторые входы элементов совпадений соединены с выходами коммутатора диапазонов, к которому подключены дополнительные разряды регистра числа, канальные выходы коммутатора каналов соединены с элементами совпадений и ключами соответствующих каналов, адресные выходы коммутатора каналов включены на регистр адреса, управляющее

5 устройство подключено дополнительно к дешифратору и обоим коммутаторам.

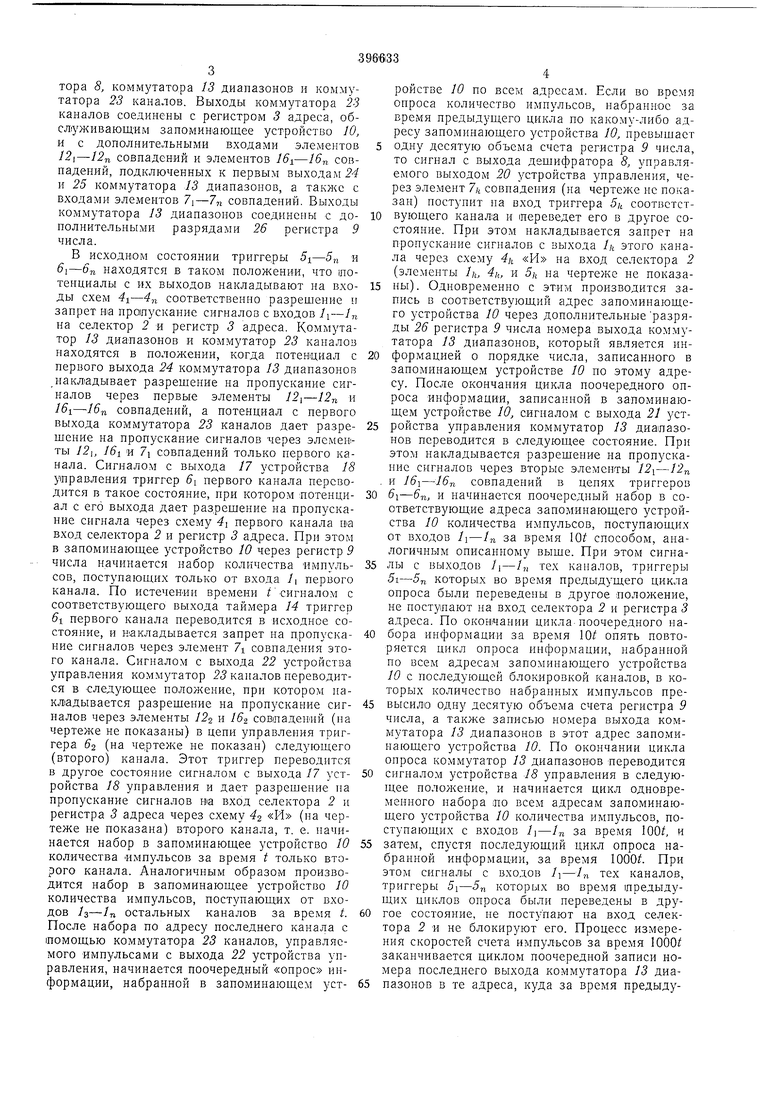

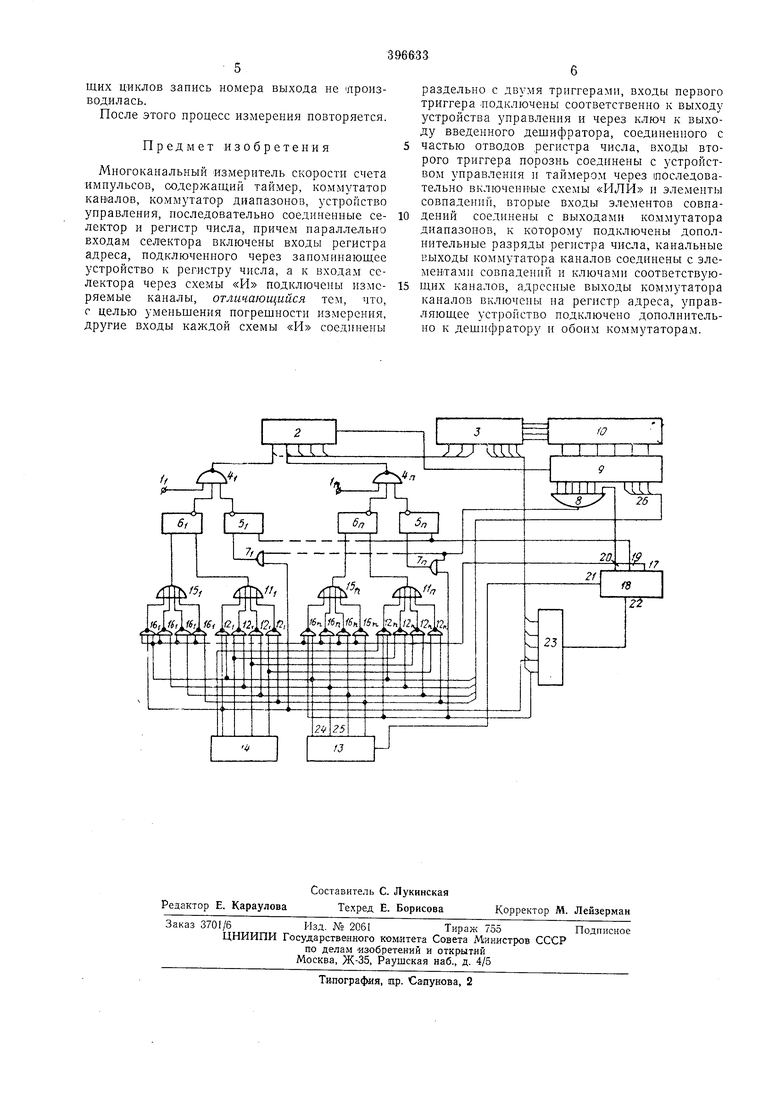

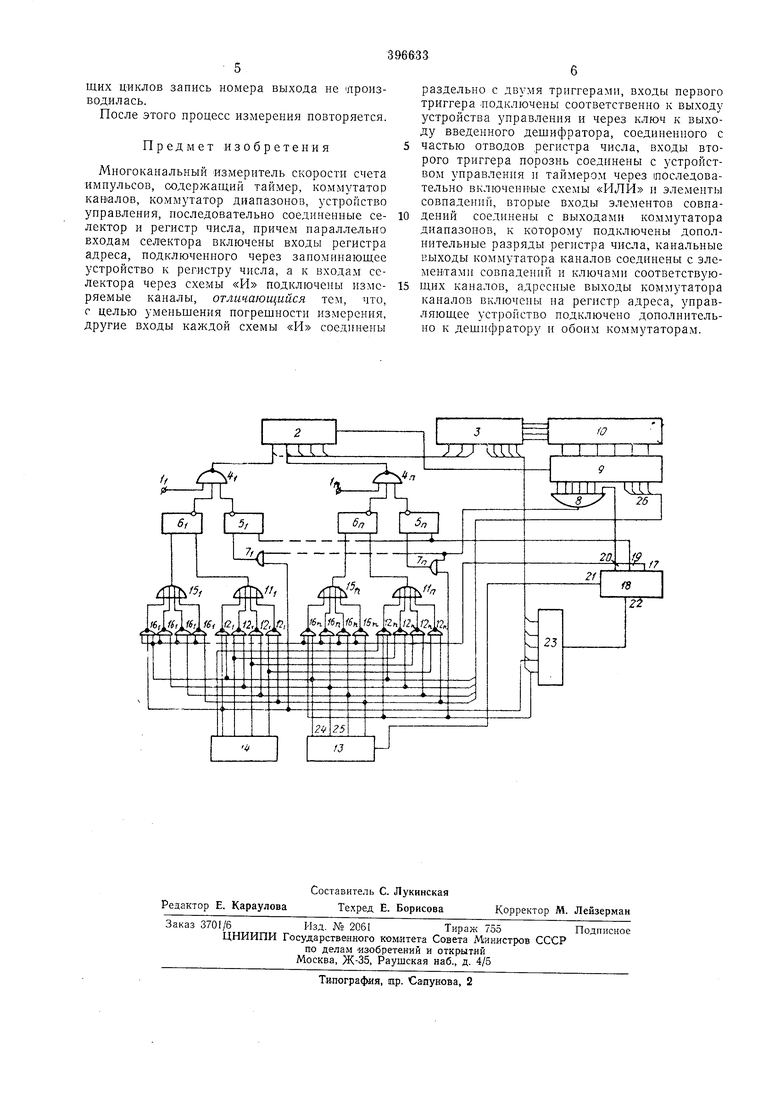

На чертеже показана схема предлагаемого

многоканального измерителя скорости счета.

Входы /1-/,; подключены к селектору 2 и

0 регистру 3 адреса через схемы «И, соединенные вторыми входами с выходами триггеров 5i-5„ и 6i-6п. Первые входы триггеров 5i-5„ через элементы совпадений (ключи) подключены к выходу дешифратора

5 8 одной десятой объема счета регистра 9 числа, соединенного с запоминающим устройством 10 и выходом селектора 2. Первые входы триггеров 6i-6п через схемы «ИЛИ и элементы совпаденнй, подключенные вторыми входами к выходам коммутатора 13 диaiпaзoнoв, соединены с выходами таймера 14 с носледовательным десятикратным увеличением временных интервалов. Вторые входы триггеров через схемы

5 15i-/5„ «ИЛРЬ и элементы 16 --/бд совпадений, подключенные к выходам коммутатора 13 диапазонов, соединены с выходом 17 устройства 18 управления, выходы 19-22 которого соединены соответственно с вторыми

0 входами триггеров 5i-5п, входами дешифратора 8, коммутатора 13 диапазонов и коммутатора 23 каналов. Выходы коммутатора 23 каналов соединены с регистром 3 адреса, обслуживающим запоминающее устройство 10, и с дополнительными входами элементов 12i-12п совпадений и элементов совпадений, подключенных к первым выходам 24 и 25 коммутатора 13 диапазонов, а также с входами элементов совпадений. Выходы коммутатора 13 диапазонов соединены с дополнительными разрядами 26 регистра 9 числа. В исходном состоянии триггеры и 6i-6п находятся в таком положении, что иотенциалы с их выходов накладывают на входы схем 4i-4п соответственно разрешение и запрет Hia проиускание сигналов с входов Д-/„ на селектор 2 и регистр 3 адреса. Коммутатор 13 диапазонов и коммутатор 23 каналов находятся в положении, когда потенциал с первого выхода 24 коммутатора 13 диапазонов накл адывает разрешение на пропускание сигналов через первые элементы 12i-12п и 16i-16п совпадений, а потенциал с первого выхода коммутатора 23 каналов дает разрешение на пропускание сигналов через элсмевты 12i, 16i и /1 совпадений только первого канала. Сигналом с выхода 17 устройства 18 управления триггер 6i первого канала переводится в такое состояние, при котором потенциал с его выхода дает разрешение на пропускание сигнала через схему 4i первого канала еа вход селектора 2 и регистр 3 адреса. При этом в запоминающее устройство 10 через регистр 9 числа начинается набор количества импульсов, поступающих только от входа 1 первого канала. По истечении времени /сигналом с соответствующего выхода таймера М триггер 6i первого канала переводится в исходное состояние, и накладывается запрет на пропускание сигналов через элемент 7i совпадения этого канала. Сигналом с выхода 22 устройства управления коммутатор 5 каналов переводится в следующее положение, при котором иакл адывается разрешение на пропускание сигналов через элементы 122 и /& совпадений (на чертеже не показаны) в цепи управления триггера 62 (на чертеже не показан) следующего (второго) канала. Этот триггер переводится в другое состояние сигналом с выхода 17 устройства 18 управления и дает разрешение па пропускание сигналов iia вход селектора 2 и регистра 3 адреса через схему 2 «И (на чертеже не показана) второго канала, т. е. начинается набор в запоминающее устройство 10 количества импульсов за время t только второго канала. Аналогичным образом производится набор в запоминающее устройство 10 количества импульсов, поступающих от входов /3-/г остальных каналов за время /. После набора по адресу последнего канала с помощью коммутатора 23 каналов, управляемого импульсами с выхода 22 устройства управления, начинается поочередный «опрос информации, набранной в запоминающем устройстве 10 по всем адресам. Если во время опроса количество импульсов, набранное за время предыдущего цикла по какому-либо адресу запоминающего устройства 10, превышает одну десятую объема счета регистра 9 числа, то сигнал с выхода дешифратора 8, управляемого выходом 20 устройства управления, через элемент 7k совнадения (на чертеже не показан) поступит на вход триггера 5k соответствующего канала и переведет его в другое состояние. При этом накладывается запрет на пропускание сигналов с выхода /А этого канала через схему 4ii «И на вход селектора 2 (элементы Ik, 4k, и 5k на чертеже не показаны). Одновременно с этим производится запись в соответствующий адрес запоминающего устройства 10 через дополнительныеразряды 26 регистра 9 числа номера выхода коммутатора 13 диапазонов, который является информацией о порядке числа, записанного в запоминающем устройстве 10 по этому адресу. После окончания цикла поочередного опроса информации, записанной в запоминающем устройстве 10, сигналом с выхода 21 устройства управления коммутатор 13 диапазонов переводится в следующее состояние. При этом накладывается разрешение на пропускание сигналов через вторые элементы 12i-12п и 16i-16п совпадений в цепях триггеров 1-6п, И начинается поочередный набор в соответствующие адреса запоминающего устройства 10 количества импульсов, поступающих от входов /1-In за время 10/ способом, аиалогичным описанному выше. При этом сигналы с выходов /1-/,j тех каналов, триггеры 5t-5„ которых во время предыдущего цикла опроса были переведены в другое положение, не поступают на вход селектора 2 и регистра 3 адреса. По окончании цикла поочередного набора информации за время 10/ опять повторяется цикл опроса информации, набранной по всем адресам запоминающего устройства 10 с последующей блокировкой каналов, в которых количество набранных импульсов превысилю одну десятую объема счета регистра 9 числа, а также записью номера выхода коммутатора 13 диапазонов в этот адрес запоминающего устройства 10. По окончании цикла опроса коммутатор 13 диапазонов переводится сигналом устройства 18 управления в следующее положение, и начинается цикл одновременного набора ;по всем адресам запоминающего устройства 10 количества импульсов, поступающих с входов /1-/„ за время 100/, и затем, спустя последующий цикл опроса набранной информации, за время 1000/. При этом сигнал1Ы с входов тех каналов, триггеры 5i-5„ которых во время предыдущих циклов опроса были переведены в другое состояние, ие поступают на вход селектора 2 и не блокируют его. Процесс измерения скоростей счета импульсов за время 1000/ заканчивается цикло.м поочередной записи номера последнего выхода коммутатора 13 диапазонов в те адреса, куда за время предыдущих циклов запись номера выхода не производилась. После этого процесс измерения повторяется.

Предмет изобретения

Многоканальный измеритель скорости счета импульсов, содержащий таймер, коммутатор кавалок, коммутатор диапазонов, устройство управления, последовательно соединенные селектор и регистр числа, причем параллельно входам селектора включены входы регистра адреса, подключенного через запоминающее устройство к регистру числа, а к входам селектора через схемы «И подключены измеряемые каналы, отличающийся тем, что, с целью уменьщения погрешности измерения, другие входы каждой схемы «И соединены

раздельно с двумя триггерами, входы первого триггера .подключены соответственно к выходу устройства управления и через ключ к выходу введенного дещифратора, соединенного с

частью отводов .регистра числа, входы второго триггера порознь соединены с устройством управления и таймером через шоследовательно включенные схемы «ИЛИ и элементы совпадений, вторые входы элементов совпадений соединены с выходами коммутатора диапазонов, к которому подключены дополнительные разряды регистра числа, канальные выходы коммутатора каналов соединены с элементами совпадений и ключами соответствующих каналов, адресные выходы коммутатора каналов включены на регистр адреса, управляющее устройство подключено дополнительно к дешифратору и обоим коммутаторам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многопрограммный регулятор температуры | 1983 |

|

SU1136123A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| Многоканальный регулятор тепловых процессов (его варианты) | 1980 |

|

SU943667A1 |

| Устройство для регистрации ритма сердечной деятельности и характера его изменений | 1978 |

|

SU784867A1 |

| Многоканальное устройство приоритетного обслуживания | 1989 |

|

SU1675886A1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Система радиосвязи | 1989 |

|

SU1660187A1 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| Многоканальный коммутатор | 1991 |

|

SU1780182A1 |

Авторы

Даты

1973-01-01—Публикация