Изобретение относится к радиоэлектронике, в частности к электронной коммутационной технике, и может быть использовано в автоматических системах сбора информации.

Известен многоканальный коммутатор, содержащийгенератор тактовых импульсов, распределитель импульсов, блок управления, выход которого подключен через дополнительный ключевой элемент и источник тока к шине питания, общую и информационную шину, в каждом канале источник информации, первый и второй ключевые элементы и синхронный Д-триггер. Выход источника информации в каждом канале через первый ключевой элемент подключен к информационной шине, первый вход источника информации соединен с общей шиной, а второй вход через второй ключевой элемент-с шиной питания. Информационный вход Д-триггер;з первого канала соединен с выходом распределителя импульсов, прямые выходы Д-триггеров, кроме Д-триггера последнего канала, соединены с информационными входами Д-триггеров последующих каналов и с входами ключевых

элементов соответственно своих каналов. Коммутатор содержит также генератор импульсов ускоренного опроса, регистр адреса, регистр текущего адреса, формирователь импульса запроса, элемент ИЛИ, два триггера, четыре элемента И, М элементов сравнения, причем входы каждого из элементов сравнения соединены с одноименными выходами регистра адреса и регистра текущего адреса, а выходы всех М элементов сравнения подключены к входам первого М-входового элемента И, выход которого подключен к второму входу первого триггера, первый вход которого соединен с выходом формирователя импульсов запроса и вторым входом второго триггера, прямой выход первого триггера подключен к первому входу второго элемента И, к второму входу которого подключен выход генератора импульсов ускоренного опроса, а выход второго элемента И подключен к первому входу элемента ИЛИ, инверсный выход первого триггера подключен к первому входу третьего элемента И, к второму входу которого подключен генератор тактовых импульсов, а выход третьего элемента И соединен с первым входом второго триггера и первым входом четвертого элемента И, EITOрой вход которого соединен с прямым выходом второго триггера, а выход четвертого элемента ИЛИ подключен к второму входу элемента ИЛИ, выход которого соединен с входами распределителя импульсов, блока управления, регистра текущего адреса, входами синхронизации Д-триггеров.

Недостатком данного коммутатора является значительное время доступа к адресуемому источнику информации, прямо пропорциональное его номеру в цепи источников, а также невозможность сохранения достоверности информации канала, при опросе которого поступил сигнал запрос канала.

Известен также коммутатор, содержащий генератор тактовых импульсов, распределитель импульсов, блок управления, выход которого подключен через дополнительный ключевой элемент и источник тока к шине питания, общую и информационную шину, в каждом канале источник информации, первый и второй ключевые элементы и синхронный Д-триггер. Выход источника информации в каждом канале через первый ключевой элемент подключен к информационной шине, первый вход источника ин формации соединен с общей шиной, а второй вход через второй ключевой элемент соединен с шиной питания. Информационный вход Д-триггера первого канала соединен с выходом распределителя импульсов, прямые выходы Д-триггеров, кроме триггера последнего канала, соединены с информационными входами Д-триггеров последующих каналов и с входами ключевых элементов соответственно своих каналов. Коммутатор содержит также элемент И, устройство формирования адреса, дьа блока из М элементов И, блок из М элементон ИЛИ, блока АЦП, блок из N элементов И. запоминающее устройство, триггер Шмидта, регистр адреса, причем первый вход элемента И, вход запись запоминающего устройства и первые входы элементов И первого блока из М элементов И и блоке из N элементов И соединены с инверсным выходом триггера UJмидтa, прямой выход которого подключен к входу чтение запоминающего устройства и к первым входам элементов И второго блока из М элементов И, вход триггера Шмидта соединен с входом запрос многоканального коммутатора, вторые входы элементов И второго блока из М элементов И соединены с соответствующими выходами регистра адреса, входы которого соединены с адресными входами многоканального коммутатора.

второй вход элемента И подключен к выходу генератора тактовых импульсов, а выход элемента И соединен с входами распределителя импульсов, блока управления, устройства формирования адреса и с входами синхронизации Д-триггеров, синхронизирующий вход устройства формирования адреса подключен к выходу распределителя импульсов, вторые входы элементов И первого блока из М элементов И подключены к соответствующим выходам устройства формирования адреса, выходы одноименных элементов И первого и второго блоков из М-элементов И соединены соответственное

первыми и вторыми входами соответствующих элементов ИЛИ блока из М элементов ИЛИ, выходы которых соединены с соответствующими адресными входами запоминающего устройства, информационные входы

которых соединены с соответствующими выходами элементов И блока из N элементов И,- информационные выходы запоминающего устройства соединены с информационными выходами многоканального коммутатора, вторые входы элементов И блока из N элементов И соединены с соответствуюш.ими выходами блока АЦП, входкоторого подключен к информационной шине.

Недостатком данного коммутатора является его неспособность обеспечить свободный доступ г отребителя к источнику информации в реа.пьном масштабе времени.Наиболее близким к предлагаемому является многоканальный коммутатор, содер;| аш,ий блок формирования адреса канала, таймер, распределитель, импульсов, блок управления, ключевой элемент, источниктока, информационную иину, шину питания и

общую шину, а также генератор тактовых импульсов, выход которого соединен с входом блока управления, выход которого подключен через ключевой элемент и источник тока к шине питания, соединенной в каждом

канале с первым входом первого ключевого элемента, второй вход которого подключен к первому входу второго ключевого элемента и выходу Д-триггера, а выход соединен с первым входом источника информации, рторой вход которого подключен к общей шине, а выход соединен с вторым входом второго ключевого элемента, выход которого подключен к информационной шине, причем вход сброса Д-триггера соединен с входами

сброса Д-триггеров остальных каналов и первым выходом блока формирования адреса канала, вход которого соединен с входом адреса устройства. Выход таймера подключен к синхронизирующим входам Д-триггеров каналов и входу распределителя

импульсов, выход которого соединен с информационным входом Д-триггера первого канала и первым входом таймера, группа вторых входов которого подключена соответственно к группе вторых выходов блока формирования адреса канала, группа третьих входов - соответственно к выходам Дтриггеров каждого канала, причем выход Д-триггера, за исключением Д-триггера последнего канала, связан с информационным входом Д-триггера последующего канала, четвертый вход таймера соединен с выходом генератора тактовых импульсов, пятый - с первым выходом блока формирования адреса канала, а шестой - с информационным входом устройства.

Недостатком данного коммутатора являются его низкие функциональные возможности, обусловленные неспособностью коммутатора реализовать свободный доступ потребителя к каналам при коррекции режимов их опроса и адресный опрос каналов,

Цель изобретения - расширение области использования устройства путем реализации свободного доступа к каналам при коррекции режима их опроса и адресного опроса каналов.

Поставленная цель достигается тем. что в многоканальный коммутатор, содержащий блок формирования адреса канала, таймер, генератор тактовых импульсов и в каждом канале Д-триггер, выход которого соединен с выходной шиной данного канала, а синхронизирующий вход с синхронизирующими входами Д-триггеров остальных каналов и выходом таймера, группа первых входов которого подключена соответственно к группе первых выходов блока формирования адреса канала, группа вторых входов - соответственно к выходам Д-триггеров каждого канала, причем выход Д-триггера, за исключением Д-триггера последнего канала, связан с информационным входом Д-триггера последующего канала, третий вход таймера соединен с выходом генератора тактовых импульсов, четвертый - со вторым выходом блока формирования адреса канала, пятый - с информационным входом устройства, дополнительно введены блок свободного доступа, блок выбора режима, элемент ИЛИ и формирователь одиночного импульса, вход которого соединен с выходом таймера, а выход - с шестым входом таймера и входом элемента ИЛИ, второй вход которого подключен к выходу Д-триггера последнего канала, а выход - к информационному входу Д-триггера первого канала, при этом второй вход формирователя одиночного импульса

соединен со вторым выходом блока формирования адреса канала и первым входом блока свободного доступа, группа вторых входов которого подключена соответственно к группе вторых входов таймера, третий вход соединен с синхронизирующими входами Д-триггеров каналов, четвертый - с первым входом управления устройства, пятый - с первым выходом блока выбора режима, второй выход которого соединен с входом адреса блока формирования адреса канала, первый, второй и третий входы соответственно с входом адреса устройства, вторым и третьим входами управления устройства, а группа четвертых входов - соответственно с группой первых выходов блока свободного доступа, группы вторых и третьих выходов которого подключены соответственно к входам установки и входами сброса Д-триггеров каналов, а четвертый выход - к седьмому входу таймера.

Осуществление изобретения позволит расширить функциональные возможности устройства за счет реализации возможности свободного доступа к каналам при коррекции режима их опроса и адресного опроса каналов. Будет обеспечена возможность получения потребителем информации каналов с большей оперативностью.

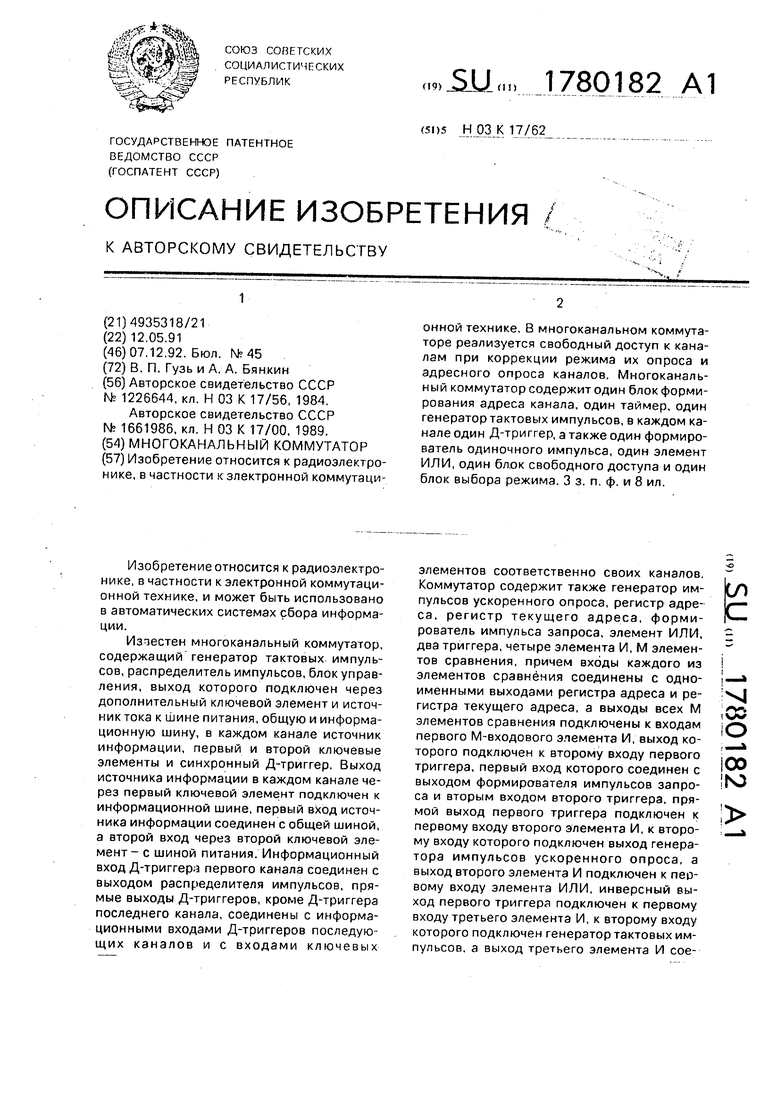

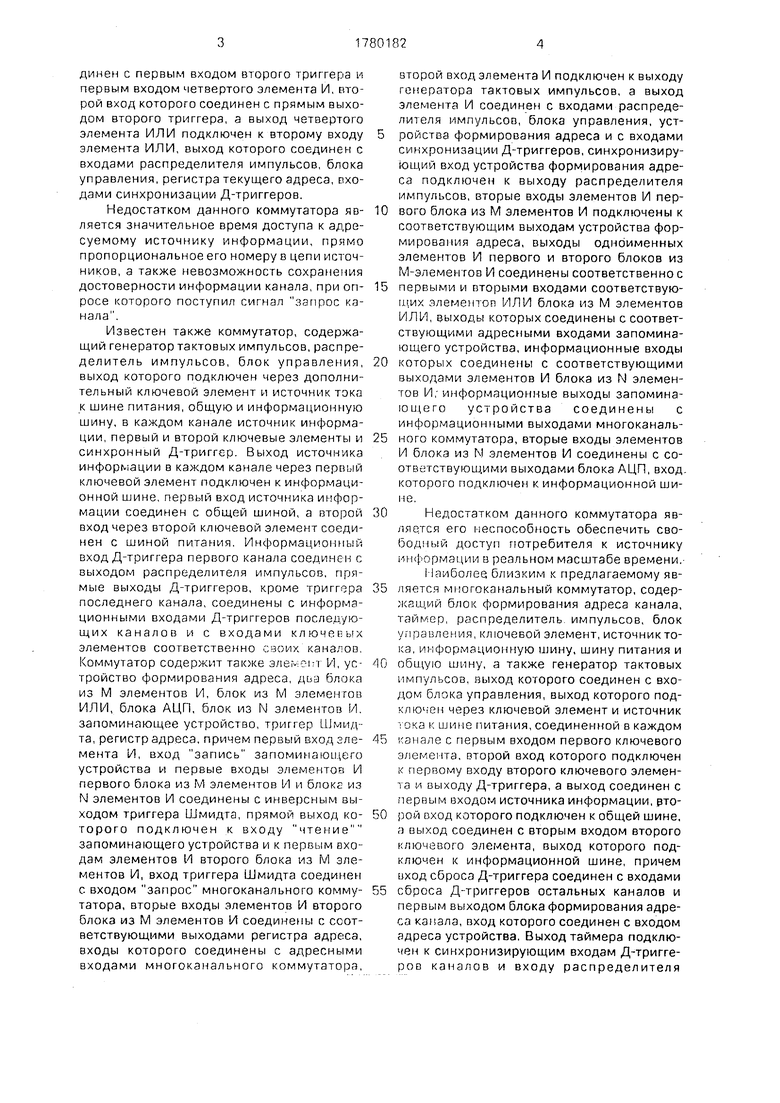

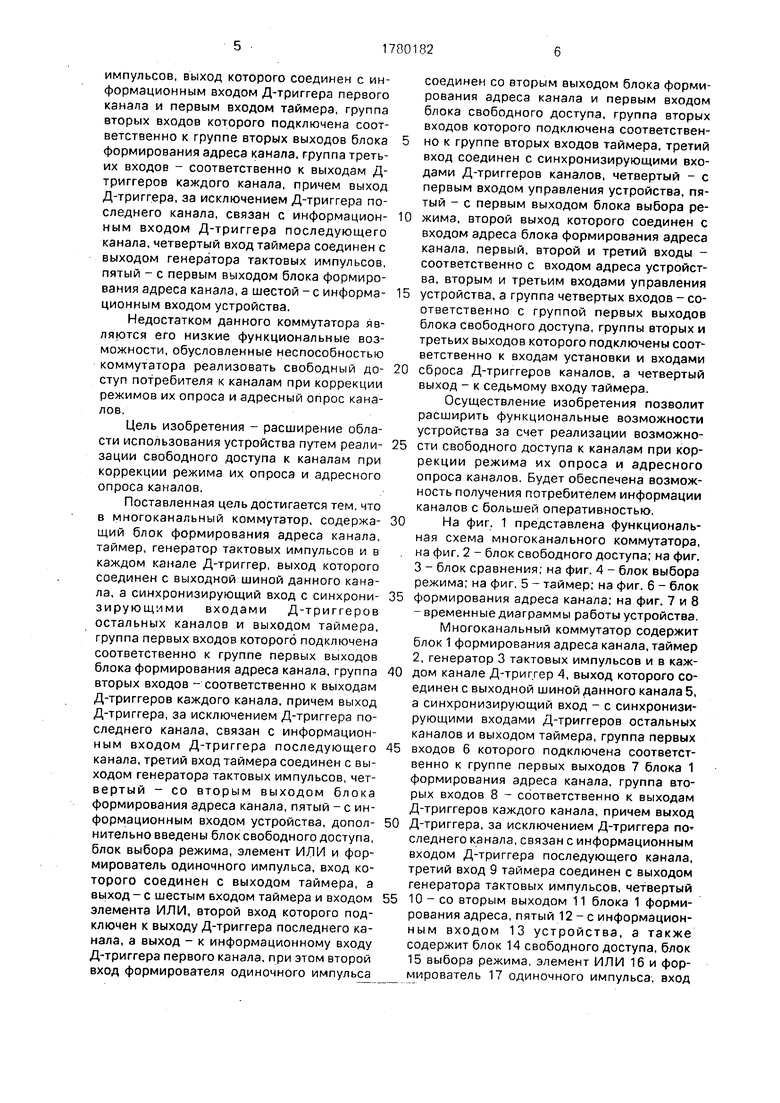

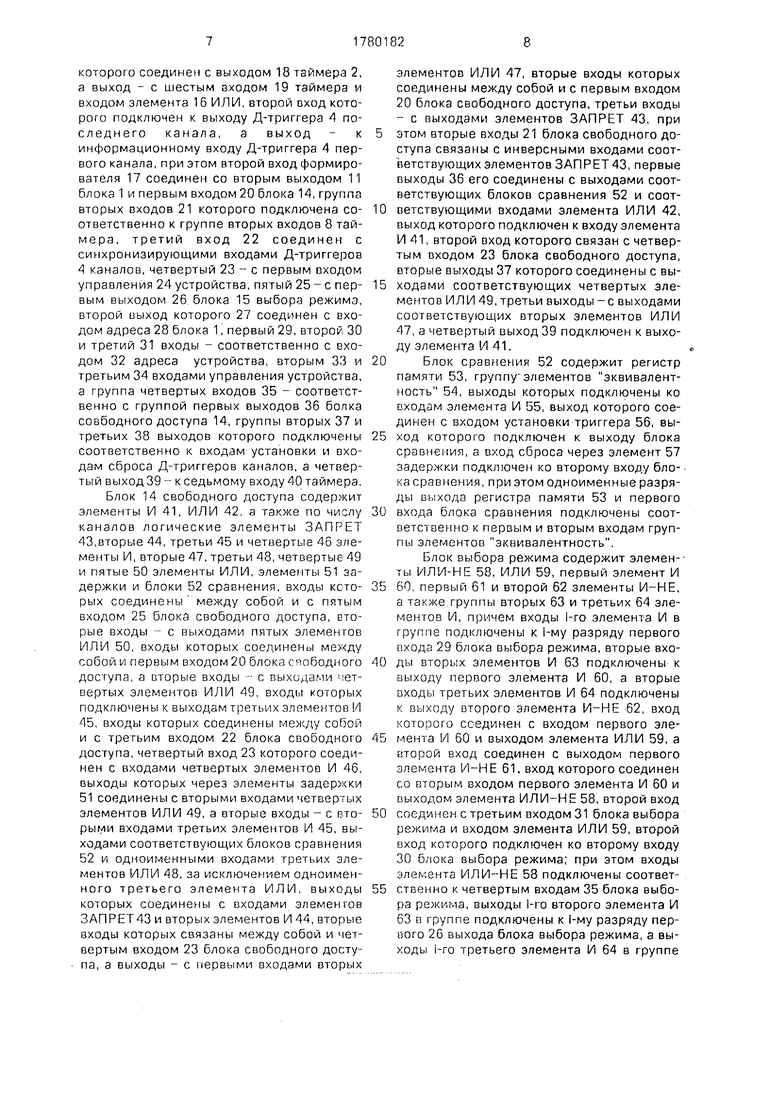

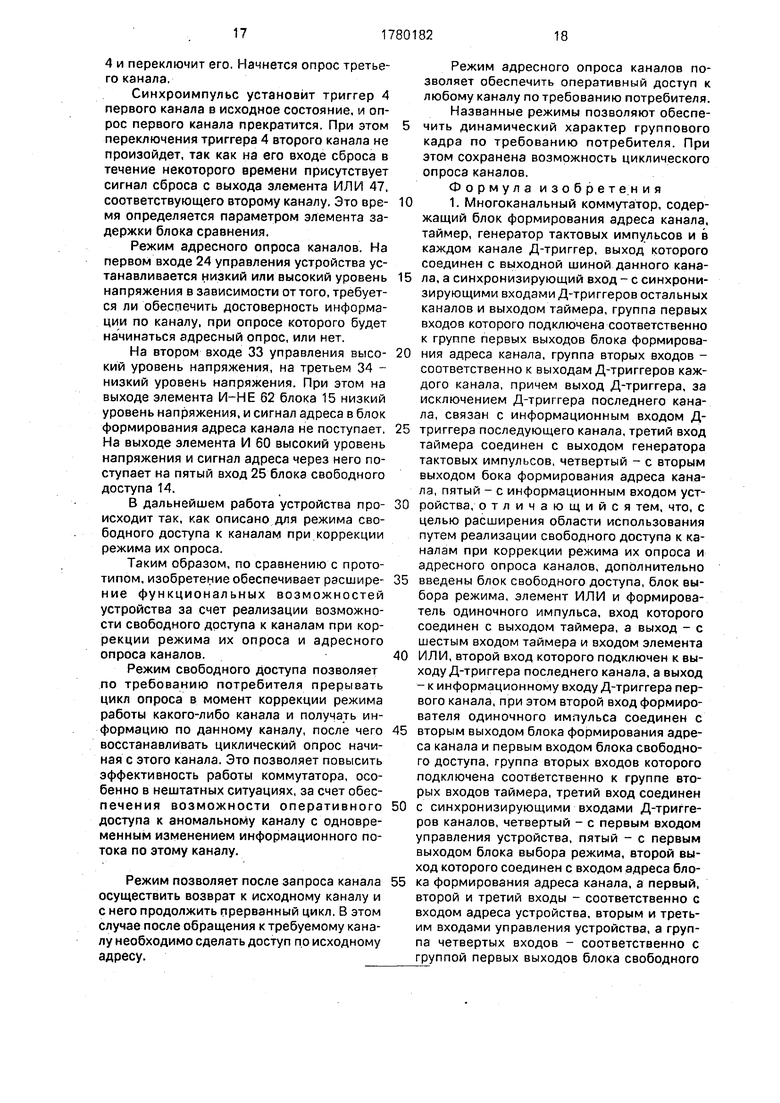

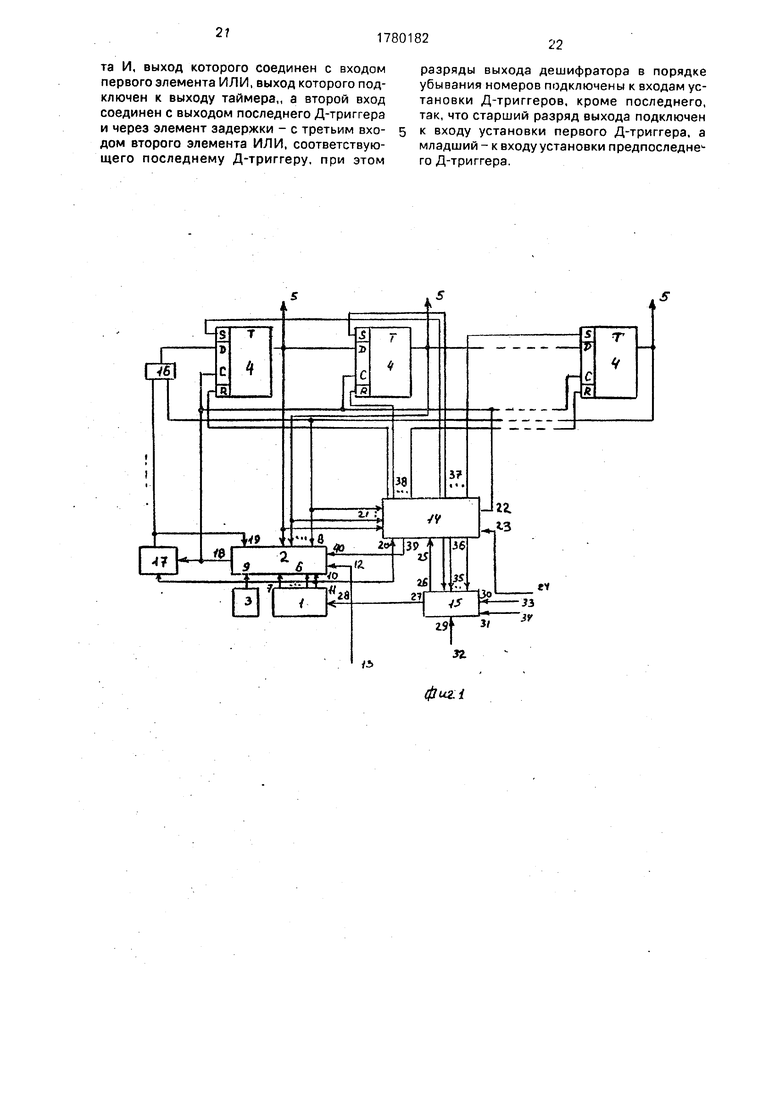

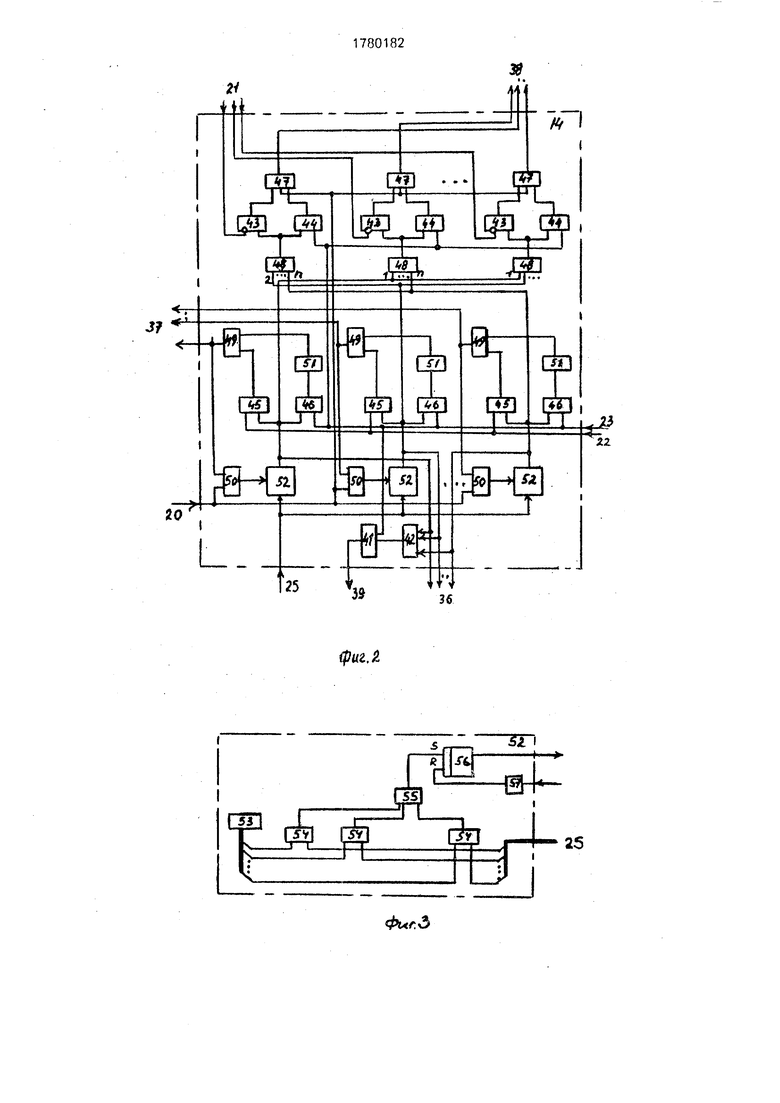

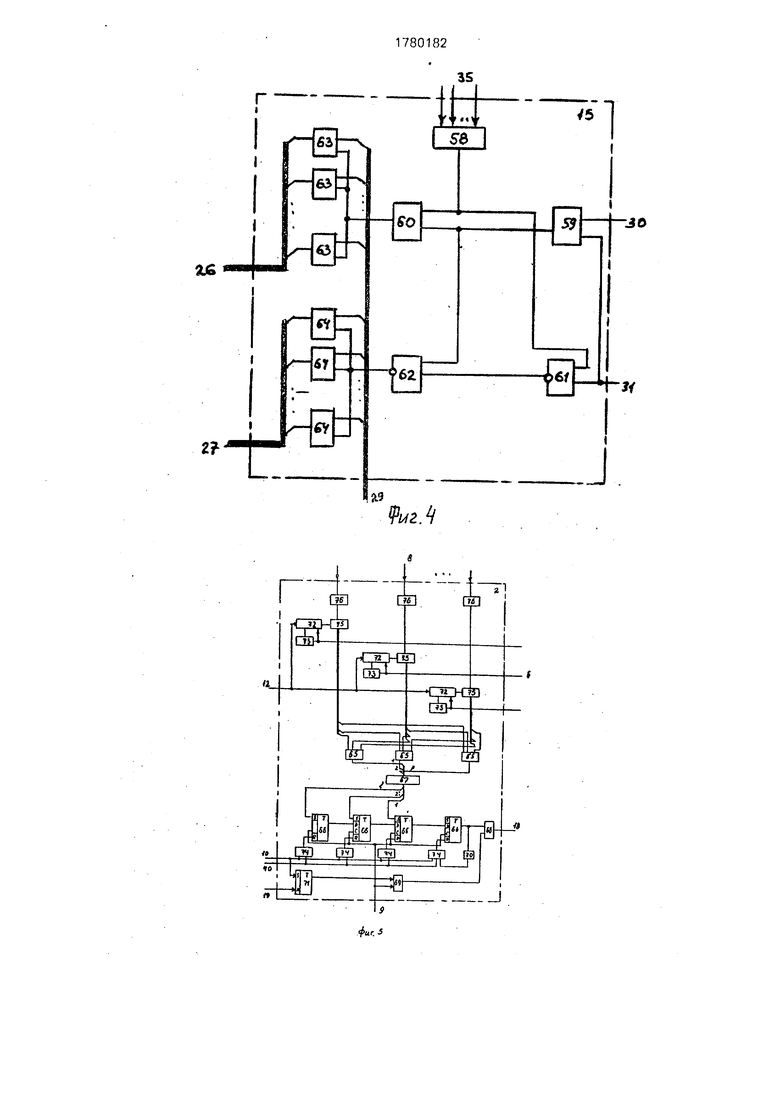

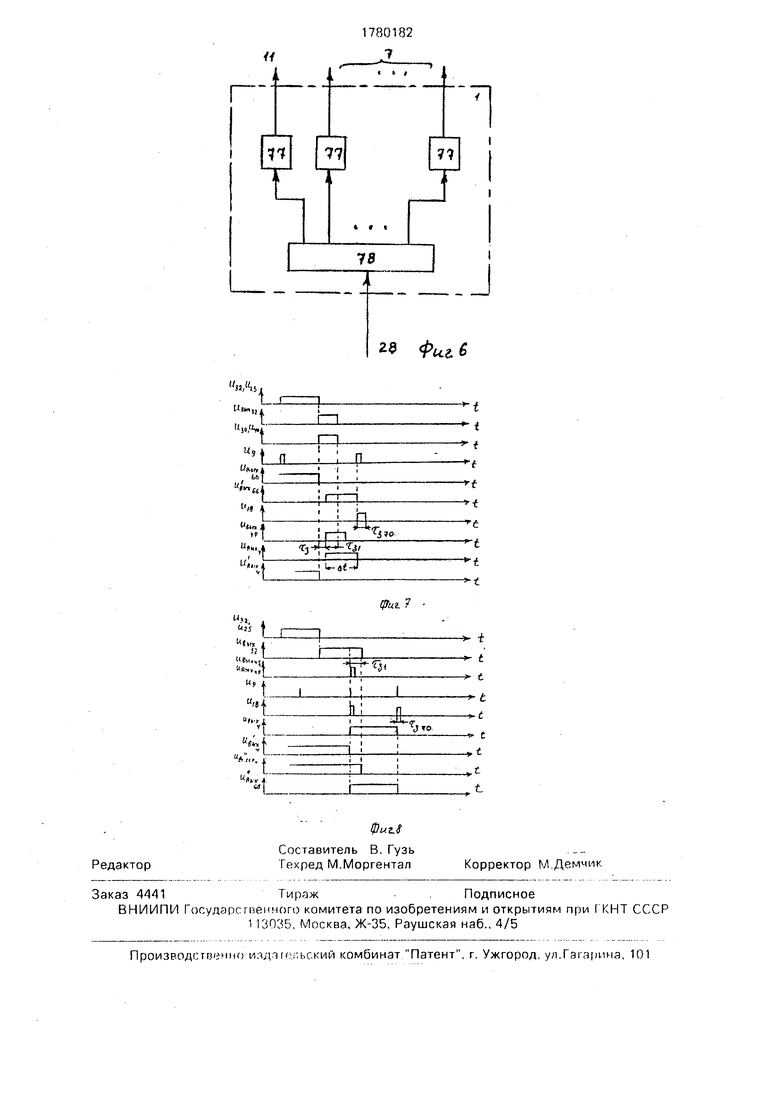

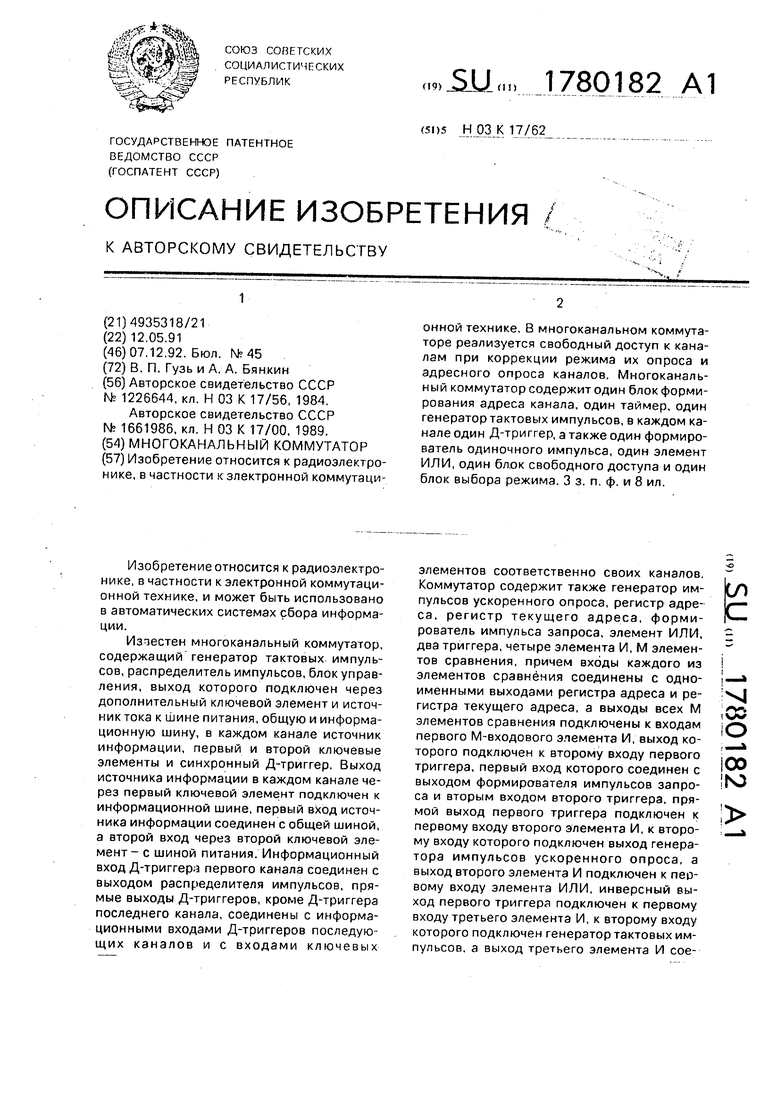

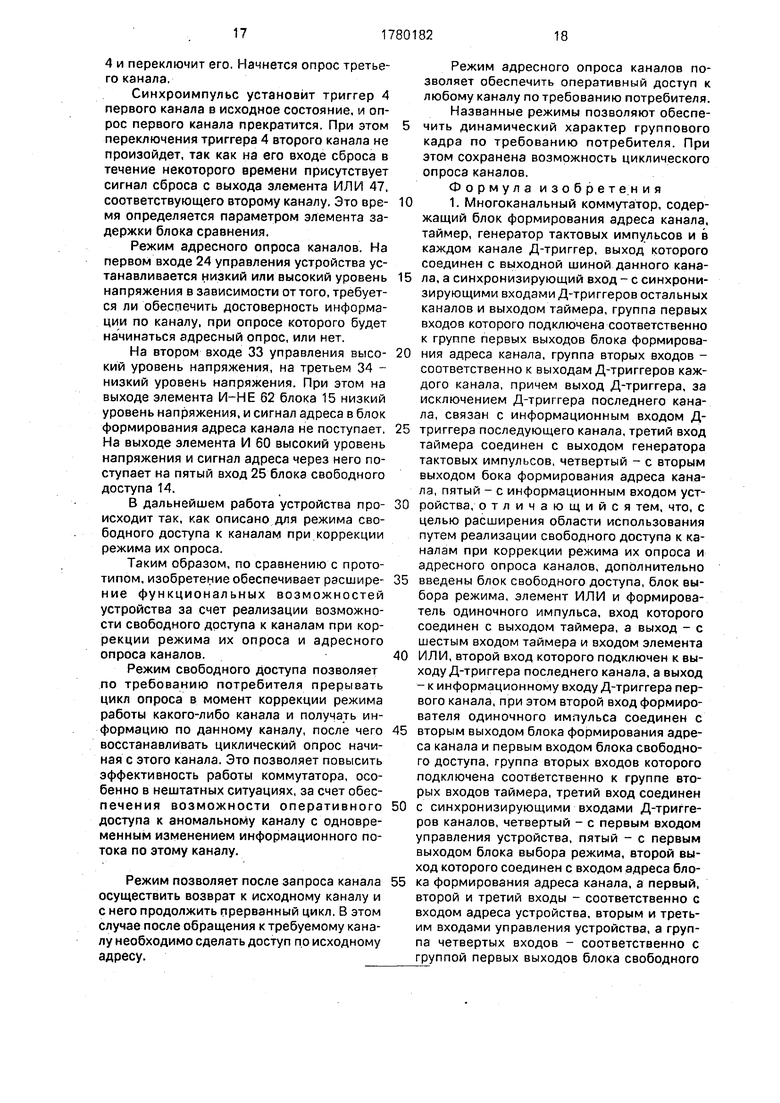

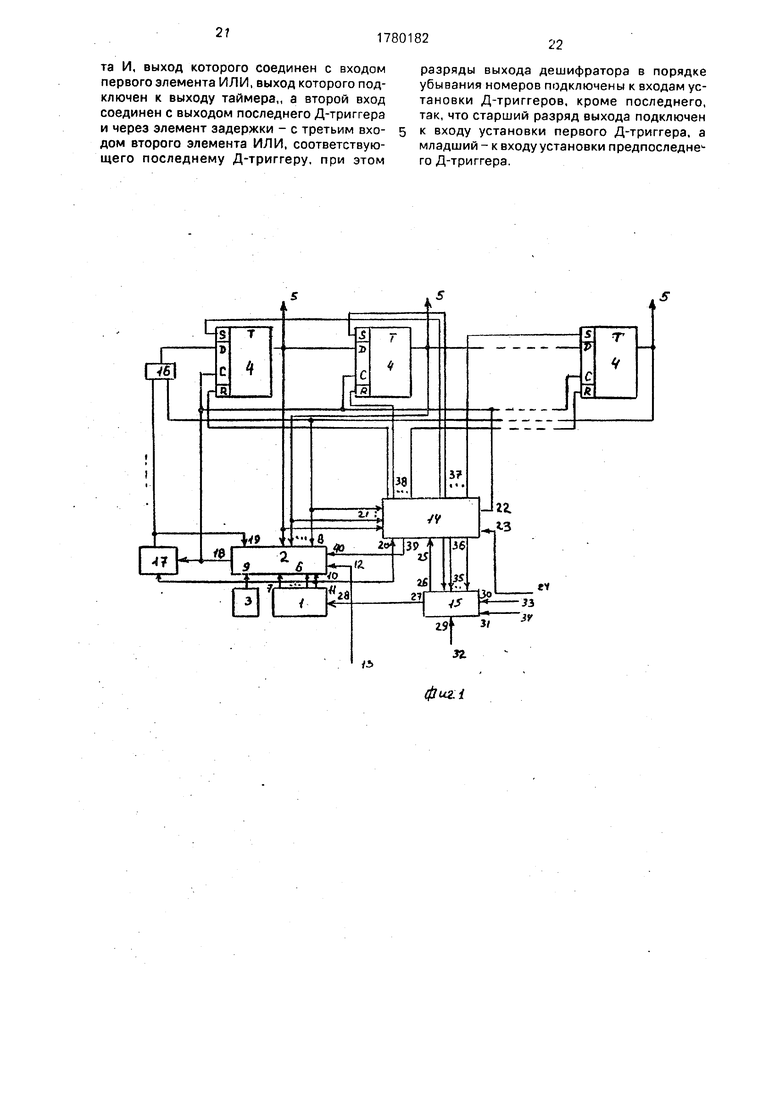

На фиг. 1 представлена функциональная схема многоканального коммутатора, на фиг. 2 - блок свободного доступа; на фиг. 3 - блок сравнения; на фиг. 4 - блок выбора режима; на фиг. 5 - таймер; на фиг. 6 - блок формирования адреса канала; на фиг. 7 и 8 - временные диаграммы работы устройства.

Многоканальный коммутатор содержит блок 1 формирования адреса канала, таймер 2, генератор 3 тактовых импульсов и в каждом канале Д-триггер 4, выход которого соединен с выходной шиной данного канала 5, а синхронизирующий вход - с синхронизирующими входами Д-триггеров остальных каналов и выходом таймера, группа первых входов 6 которого подключена соответственно к группе первых выходов 7 блока 1 формирования адреса канала, группа вторых входов 8 - соответственно к выходам Д-триггеров каждого канала, причем выход Д-триггера, за исключением Д-триггера пО следнего канала, связан с информационным входом Д-триггера последующего канала, третий вход 9 таймера соединен с выходом генератора тактовых импульсов, четвертый 10 - со вторым выходом 11 блока 1 формирования адреса, пятый 12 - с информационным входом 13 устройства, а также содержит блок 14 свободного доступа, блок 15 выбора режима, элемент ИЛИ 16 и формирователь 17 одиночного импульса, вход

которого соединен с выходом 18 таймера 2, а выход - с шестым входом 19 таймера и входом элемента 16 ИЛИ, второй вход которого подключен к выходу Д-триггера 4 последнего канала, а выход - к информационному входу Д-триггера 4 первого канала, при этом второй вход формирователя 17 соединен со вторым выходом 11 блока 1 и первым входом 20 блока 14, группа вторых входов 21 которого подключена соответственно к группе вторых входов 8 таймера, третий вход 22 соединен с синхронизирующими входами Д-триггеров А каналов, четвертый 23 - с первым входом управления 24 устройства, пятый 25 - с первым выходом 26. блока 15 выбора режима, второй выход которого 27 соединен с входом адреса 28 блока 1 i первый 29, второй 30 и третий 31 входы - соответственно с входом 32 адреса устройства, вторым 33 и третьим 34 входами управления устройства, а группа четвертых входов 35 - соответственно с группой первых выходов 36 болка совбодного доступа 14, группы вторых 37 и третьих 38 выходов которого подключены соответственно к входам установки и входам сброса Д-триггеров каналов, а четвертый выход 39 - к седьмому входу 40 таймера. Блок 14 свободного доступа содержит элементы И 41, ИЛИ 42. а также по числу каналов логические элементы ЗАПРЕТ 43,вторые 44, третьи 45 и четвертые 46 элементы И, вторые 47, третьи 48, четвертые 49 и пятые 50 элементы ИЛИ, элементы 51 задержки и блоки 52 сравнения, входы которых соединены между собой и с пятым входом 25 блоки свободного доступа, вторые входы - с выходами пятых элементов ИЛИ 50, входы которых соединены между собой 1/1 первым входом 20 блока спободного доступа, а вторые входы - с выходами четвертых элементов ИЛИ 49, входы которых по,дключены к выходам третьих элементов И 45, входы которых соединены между собой и с третьим входом 22 блока свободного доступа, четвертый вход 23 которого соединен с 1ходами четвертых элементов И 46, выходы которых через элементы задержки

51соединены с вторыми входами четвертых элементов ИЛИ 49, а вторые входы - с вторыми входами третьих элементов И 45, выхо,цами соответствующих блоков сравнения

52и одноименными входами третьих элементов ИЛИ 48, за исключением одноименного третьего элемента ИЛИ, выходы которых соединены с входами элеменгов ЗАПРЕТ43и вторых элементов И 44, вторые входы которых связаны между собой и четвертым входом 23 блока свободного доступа, а выходы - с |-|ервыми входами вторых

элементов ИЛИ 47, вторые входы которых соединены между собой и с первым входом 20 блока свободного доступа, третьи входы - с выходами элементов ЗАПРЕТ 43, при

этом вторые входы 21 блока свободного доступа связаны с инверсными входами соответствующих элементов ЗАПРЕТ43, первые выходы 36 его соединены с выходами соответствующих блоков сравнения 52 и соответствующими входами элемента ИЛИ 42, выход которого подключен к входу элемента И 41, второй вход которого связан с четвертым входом 23 блока свободного доступа, вторые выходы 37 которого соединены с выходами соответствующих четвертых элементов ИЛИ 49, третьи выходы-с выходами соответствующих вторых элементов ИЛИ 47, а четвертый выход 39 подключен к выходу элемента И 41.

Блок сравнения 52 содержит регистр

памяти 53, группу элементов эквивалентность 54, выходы которых подключены ко входам элемента И 55, выход которого соединен с входом установки триггера 56, выход которого подключен к выходу блока сравнения, а вход сброса через элемент 57 задержки подключен ко второму входу бло-ка сравнения, при этом одноименные разряды выхода регистра памяти 53 и первого

входа блока сравнения подключены соответственно к первым и вторым входам группы элементов эквивалентность.

Блок выбора режима содержит элемен-ты ИЛИ-НЕ 58, ИЛИ 59, первый элемент И

60, первый 61 и второй 62 элементы И-НЕ, а также.группы вторых 63 и третьих 64 элементов И, причем входы i-ro элемента И в группе подключены к i-му разряду первого входа 29 блока выбора режима, вторые входы вторых элементов И 63 подключены к выходу первого элемента И 60, а вторые входы третьих элементов И 64 подключены к выходу второго элемента И-НЕ 62, вход которого соединен с входом первого элемента И 60 и выходом элемента ИЛИ 59, а второй вход соединен с выходом первого элемента И-НЕ 61, вход которого соединен со вторым входом первого элемента И 60 и выходом элемента ИЛИ-НЕ 58, второй вход

соединен с третьим входом 31 блока выбора режима и входом элемента ИЛИ 59, второй вход которого подключен ко второму входу 30 блока выбора режима; при этом входы элемента ИЛИ-НЕ 58 подключены соответственно к четвертым входам 35 блока выбора режима, выходы 1-го второго элемента И 63 в группе подключены к 1-му разряду первого 26 выхода блока выбора режима, а выходы i-ro третьего элемента И 64 в группе

подключены к i-му разряду второго выхода 27 блока выбора режима.

Таймер содержит группы элементов ИЛИ 65, Д-триггеры 66 дешифратор 67, первый 68 элемент ИЛИ. элемент И 69, элемент 70 задержки, триггер 71 режима, а также группы регистров 72, элементов 73 задержки, вторых элементов ИЛИ 74, ключевых элементов 75. ждущих мультивибраторов 76, входы которых соединены соответственно с вторыми входами 8 таймера, а выходы - с первыми входами ключевых элементов 75, вторые входы которых подключены к выходам соответствующих регистров 72, а одноименные разряды выходов ключевых элементов 75 соединены с входами соответствующих элементов ИЛИ 65, выходы которых подключены к входу дешифратора 67 в соответствии с номерами разрядов на входах элементов ИЛИ 65, при этом первые входы 6 таймера соединены с соответствующими входами сброса регистров 72 и через элементы задержки 73 с входами записи регистров, информационные входы которых соединены между собой и с пятым входом 12 таймера, третий вход которого соединен с первым входом элемента И 69 и синхровходами Д-триггеров 66, выходы которых соединены с информационными входами последующих Д-триггеров 66, за исключением последнего, а их входы сброса соединены с выходами соответствующих вторых элементов ИЛИ 74, первые входы которых соединены между собой и с седьмым входом 40 таймера, вторые входы вторых элементов ИЛИ 74 соединены между собой, с четвертым входом 10 таймера и с входом установки триггера режима 71, вход сброса которого соединен с шестым входом 19 таймера, а выход - со вторым входом элемента И 69. выход которого соединен с входом первого элемента ИЛИ 68, выход которого подключен к выходу 18 таймера, а второй вход соединен с выходом последнего Дтриггера 66 и через элемент задержки 70 соединен с третьим входом второго элемента ИЛИ 74, соответствующего последнему Д-триггеру 66; при этом разряды выхода дешифратора 67 в порядке убывания номеров подключены к входам установки Д-триггеров, кроме последнего, так, что старший разряд выхода подключен к входу установки первого Д-триггера, а младший - к входу установки предпоследнего Д-триггера.

Блок формирования адреса канала аналогичен подобному блоку в прототипе. Он содержит группу ждущих мультивибраторов 77.выход первого из которых соединен со вторым выходом 11 блока формирования адреса канала, а выходы остальных подключены соответственно к группе первых выходов 7 блока формирования адреса канала, входы ждущих мультивибраторов соединены соответственно с выходами дешифратора 78, вход которого подключен к входу 28 блока формирования адреса канала.

Многоканальный коммутатор работает следующим образом.

Исходный режим. На втором и третьем

0 входах управления устройства низкий уровень напряжения. При.этом на выходе элемента И-НЕ 62 блока выбора 15 режима будет высокий уровень напряжения и информация с входа 32 адреса устройства через третьи элементы И 64 будет поступать на блок формирования адреса канала 1. На вход 25 блока свободного доступа 14 она не поступит вследствие низкого уровня напряжения на выходе элемента И 60 блока выбо0 ра режима.

В первом режиме устройство работает аналогично прототипу. 1-|ачалу опроса должно предшествовать введение в блок 1 формирования адреса канала с входа 32 адреса

5 устройства кодовой окмбинации начало работы. При этом на выходе дешифратора 78, соединенном с входом первого ждущего мультивибратора 77, появится высокий уровень напряжения, под действием которого

0 произойдет формирование импульса на выходе 11. Высокий уровень напряжения на выхо,це 11 установит в исходное состояние формирователь 17 одиночного импульса, блоки 52 сравнения и обнулит Д-триггеры 4

5 каналов и передним фронтом Д-триггеры 66 таймера и триггер 71 режима. Д-триггеры 66 по входам установки и сброса срабатывают по переднему фронту сигнала установки и сброса, Д-триггеры 4 по этим.входам срабатывают по уровню, сигнала. На прямых выходах Д-триггеров установится низкий уровень напряжения, на выходе триггера 71 режима - высокий.

Пусть необходимо увеличить длительность опроса канала на К, где К - число, вводимое по информационному входу 12 устройства в соответствующий регистр 72 таймера. На вход 28 блока 1 формирования адреса канала подается код номера канала.

0 длительность опроса которого нужно изменить. При этом происходит срабатывание соответствующего ждущего мультивибратора 77 и высокий уровень напряжения установится на первом выходе 7 блока.

5 соответствующем поданному на вход блока 1 коду номера канала. При этом на соответствующем первом входе 6 таймера появится сигнал, передний фронт которого обнулит соответствующий регистр 72, а через время задержки, определяемое соответствующим элементом 73 задержки, обеспечит запись параллельного кода числа К. в выбранный регистр.

Генератор тактовых импульсов 3 формирует последовательность тактовых нмпульсов с периодом повторения Т. Сигналы тактовой частоты через элемент И 69, на втором входе которого высокий уровень напряжения, и первый элемент ИЛИ 68 поступают на синхронизирующие входы Д-триггеров 4 и формирователь 17 о,циночных импульсов, формирующий на своем выходе одиночный импульс при поступлении на него с выхода 18 таймера первого синхроимпульса генератора тактовых импульсов. Сигнал, появившийся на выходе формирователя 17, поступит на инфор/Лационный вход Д-триггера4 первого канала, на синхронизирующем входе которого в этот момент присутствует сигнал с выхода 18 таймера 2. Д-триггер 4 первого канала переключится и на его выходе (выходной шине) установится высокий уровень 1 апряжения.

Передний фронт сигнала на выходе Дтриггера 4 вызывает срабатывание соответствующего ждущего мультивибратора 76, который формирует импульс, открывающий соответствующий ключевой элемент 75. Так как i-ый разряд входа дешифратора 67 соединен с выходом элемента ИЛИ 65, объединяющего i-ые разряды выходов ключе зых элементов 75, параллельный код числа К, записанного в регистр 72 первого каизлз. через ключевой элемент 75 и элементы ИЛ1/; 65 поступит на вход дешифратора 67. В соответствии со значением числа К, записанного в регистре 72 опрашиваемого канала, на опре,целенном выходе дешифратора 67 сформируется импульс, длительность которого зависит от параметров ссотиетствующего ждущего мультивибратора 76. Этот импульс передним фронтом установит в единичное состояние соответствующий Дтриггер 66. Число Д-триггеров 66 опредсл; ется количеством выходных разрядов дешифратора 67 и не больше L«2 (так как в завмсимости от величины Кмах могут быть задействованы все или не все выходные разряды дешифратора 67). При этом старший разряд дешифратора 67, соответствующий Кмакс, соединен с первым Д-тр;лггером 66, а младший, соответствующий , - с предпоследним Д-триггером 66. Так как в этот момент триггер 71 режима сигналом с выхода формирователя 17 установлен в нулевое состояние, следуюа1ий импульс тактовой частоты генератора 3 тактоЕ ых импульсов не поступит через элемент И 69 и элемент ИЛИ 68 на выход 18 таймера 2, а переключит соответствующий Д-триггер 66,

находящийся в единичном состоянии. Следующий тактовый импульс вызовет переключение следующего Д-триггера 66. Процесс переключения этих триггеров будет повторяться до тех пор, пока не переключится последний Д-триггер 66, выход которого через элемент ИЛИ 68 связан с выходом 18 таймера 2, Сигнал на выходе 18 таймера 2 своим передним фронтом переключит Д-триггеры 4 каналов и начнется опрос следующего канала.

Значение числа К, записанного в регистр 72 соответствующего канала, определяет выбор Д-триггера 66, местоположение

5 которого в цепочке задает длительность опроса дэиного кймала.

Элеменг задержки 70, выход которого через элемент ИЛИ 73 соединен с входом сброса последнего Д-триггера 66, обеспечивает его принудительную установку в нулевое состояние через время ГзУО и формирование выходного импульса последнего Д-триггера 66.

Принципиальная необходимость эле5 мента задержки 70 обусловлена следующим. Пусть в два или несколько последовательь ых регистров 72 записанозначение . С началом опроса первого канала, для которого , переключится в

0 единичное положение предпоследний Дтриггер 66. Следующий тактовый импульс переключит последний Д-триггер 66, на выходе которого появится единичный сигнал,который передним фронтом переключит Д5 триггеры 4. Начнется опрос следующего канала, для которого .

Предпоследний Д-триггер 66 вновь переключится в единичное состояние, а следующий тактовый импульс подтвердит

0 нахождение последнего Д-триггера 66 в единичном состоянии. Так как формирования HOBOCJ переднего фронта сигнала не происходит на его выходе, следующего переключения Д-триггеров 4 не произойдет.

5 Процесс опроса каналов нарушится.

Число К можно записывать во время работы коммутатора в регистры 72 любых каналов, в том числе и с те, где ранее было записано иное значение числа К.

0Сигнал с выхода Д-триггера 4 последнего канала через элемент ИЛИ 16 поступает на вход Д-триггера 4 первого канала, и процесс опроса повторяется.

Режим свободного доступа к каналам

5 при коррекции режима их опроса.

На первом и третьем (соответственно 24 и 34) входах упрааления высокий уровень напряжения, на информационном входе 13 устройства - код числа К, которое требуется записать по адресу А, подаваемому на вход

адреса 32 устройства. Значение адреса с первого входа 29 (Злока выбора режима через третьи элементы И 64. на других входах которых высокий уровень, напряжения с выхода элемента И-НЕ 62, поступает на вход 28 блока 1 формирования адреса канала и через вторые элементы И 63, на других входах которых высокий уровень напряжения с выхода элемента И 60 - на пятый вход 25 блока 14 свободного поступа. При этом осуществляется запись кода числа К в регистр памяти таймера 2 по указанному адресу. На выходе блока сравнения 52, соответствующего этому адресу, появится высокий уровень напряжения, который через четвертый элемент И 46, на другом входе которого высокий уровень напряжения по первому входу. 24 управления, элемент задержки и четвертый элемент ИЛИ 49 поступит на второй выход 37 блока свободного доступа, а значит, на вход установки Д-триггера 4, соответствующего адресу А. Одновременно сигнал с выхода блока сравнения 52 поступит через третьи элементы ИЛИ 48, вторые элементы И 44 и вторые элементы ИЛ И 47 на третьи выходы 38 блока свободного доступа, а значит, входы сброса Д-триггеров 4. не соответствующие адресу А, и обнулит их. Высокий уровень сигнала с выхода 52 блока сравнения через элементы ИЛИ 42 и И 41 поступит на четвертый выход 39 блока свободного доступа, седьмой вход 40 таймера и через элементы ИЛИ 74 передним фронтом обнулит Д-триггеры 66 таймера.

Д-триггер 4, соответствующий адресу А. сигналом по входу установки будет переключен в единичное положение, при этом благодаря элементу 51 задержки на выходе четвертого элемента И 46 переключение его, запуск ждущего мультивибратора 76 таймера и установка соответствующего триггера 66 в единичное состояние произойдет после обнуления Д-триггеров 66 сигналом по седьмому входу таймера. Длительность опроса канала будет установлена в соответствии со значением числа К, записанного в регистре 72 памяти канала, к которому потребитель получил доступ. После опроса канала, соответствующего адресу А, будет продолжен циклический опрос последующих каналов. После того, как значение адреса А поступило на вход блока свободного доступа, на выходе соответствующего блока 52 сравнения появится высокий уровень напряжения, который приведет к установлению низкого уровня напряжения на выходе элемента ИЛИ-НЕ 58 блока 15 выбора режима. Это приведет к тому, что следующее значение адреса (свободный доступ к другому каналу) не может быть подано в

блок формирования адреса и блок свободного доступа ранее, чем обнулится блок 52. Обнуление блока 52 сравнения осуществляется сигналом с выхода четвертого элемента 5 ИЛИ 49, поступающим через пятый элемент ИЛИ 50 на второй вход блока сравнения после установки Д-триггера 4, соответствующего адресу А, в единичное состояние. На фиг, 7 приведены временные диаграммы работы коммутатора при осуществлении свободного доступа к каналу. При этом в регистре 72 памяти, соответствующем ка-налу, к которому осуществляется доступ, записывается значение . На

5 диаграмме; гз - параметры элемента задержки на выходе элемента И 46; гз1 параметры элемента задержки блока сравнения; Гз70 параметры элемента задержки 70 таймера; U вых4 - уровень сигнала на

0 выходе тригера 4 канала, опрашиваемого в момент времени, предшествующий началу свободного доступа к другому каналу; UBUX. - уровень сигнала на выходе три1тера 4 канала, к которому осуществляется свободный доступ, .66 - уровень сигнала на выходе триггера 66, предпоследнего в цепочке триггеров 56 тзймера (в случае из цепочки задействуется именно этот триггер).

0Из диаграммы видно, что ,цля случая,

когда К-О, длительность опроса канала At меньше периода следования тактовой частоты Т (при этом Т ГЗ+ Гз1). Величины Д. может оказаться недостаточно для обеспечения достоверности информации по каналу. В атом . случае потребитель может обеспечить достозерность. установив значение .

Для удобства потребителя сигнал с выхода элемента ИЛИ-НЕ 58 может использоваться для индикации времени, когда разрешен свободный доступ.

В устройстве предусмотрена возможность сохранения достоверности информа5 ции канала, при опросе которого должен быть начат свободный доступ к другому каналу. В этом случае на первом входе 24 управления устройства низкий уровень напряжения, а сигнал с выхода блока 52 сравнения поступает на вход четвертого элемента ИЛИ 49 через третий элемент И 45 только в момент прихода синхроимпульса по третьему входу 22 блока свободного доступа. До этого момента продолжается опрос предыдущего канала, на входе сброса Д-триггера 4 которого сигнал с выхода второго элемента ИЛИ 47 отсутствует. С приходом синхроимпульса переключения последующего Д-триггера 4 не произойдет.

так как на его входе сброса в течение времени Тз1 после прихода синхроимпульса ( Гз1 - параметр элемента задержки блока сравнения) присутствует сигнал с выхода соответствующего второго элемента ИЛИ 47, Сигнал с выхода четвертого элемента ИЛИ 49 установит Д-триггер 4, соответствующий адресу А на входе 32 устройства, в единичное поломсение и начнется опрос соответствующего . Блок 52 сравнения устанавливается сигналом с выхода четвертого элемента ИЛИ 49 в исходное состояние.

На фиг, 8 приведены временные диаграммы работы коммутатора для указанного случая, где: Увых. 4 - уровень сигнала на выходе триггера 4 канала; к которому осуществляется свободный доступ; U вых.1 уровень сигнала на выходе триггера 4 канала, при опросе которого пришел сигнал U32 на свободный доступ: U вх.сбр.1 уровень сигнала на входе сброса триггера 4, состоящего в цепочке за триггером, при опросе которого пришел сигнал Uaa на свободный доступ: Увых.бб сигнал на выходе триггера 66 предпоследнего в цепочке триггера 66 таймера (),

Блок сравнения работает следующим образом.

Пусть в режиме свободного доступа к каналам при коррекции режима их опроса на вход 25 блока свободного доступа подан код адреса А канала, к которому производится свободный доступ. Разряды кода А по первому входу блока сравнения поступают на соответствующие входы элементов ЭКВИВАЛЕНТНОСТЬ, на вторые входы которых поступают одноимен1 ые разряды кода адреса, записанного в регистре памяти зтого блока сравнения. В регистре г амяти записывается код адреса, соответсгвуюшдзго номеру его канала. При совпадении кодов на выходе элемента И появится высокий уровень напряжения, который устанспит триггер в единичное состояние.

Появление высокого уровня сигна.па lia выходе триггера блока срави1ения к тому, что на выходе элемента ИЛИ-НЕ 58 блока выбора режима установится низкий уровень напряжения, которы 1 прекратит подачу кода адреса А, или любого другого адреса, через элементы И 63 блока 15 на вход блока сравненил. Единичный сигнал с выхода блока сравнения через элемен И 46, элемент 51 задержки и элeмeflт ИЛИ 49 поступает на выход 37 блока свободного доступа и устанавливает соответствующий адресу А триггер 4 устройства в единичное состояние, через элемент ИЛИ 50 поступае на второй вход блока сравнения и, спустя

интервал времени r.3i( Гз1 - параметр элемента задержки блока сравнения) устанавливает в исходное (нулевое) сгостояние его триггер, а значит, и сам блок сравнения (см.

фиг. 7), При этом на выходе элемента 14ЛИНЕ 58 устанавливается высокий уровень сигнала.

Если на входе блока сравнения сохранится код адреса А, цикл сброса записи информации в триггеры 4 устройства повторится. Поэтому длительность подачи кода адреса на вход 25 блока свободного доступа должна быть минимальной и обеспечивать лишь переключение триггера бло5 ка сравнени;:,

В случае функционирования устройства в режиме свободного доступа с сохранением достоверности информации по каналу, при опросе которого пришел запрос на свободный доступ, установка блока сравнения в исходное состояние производится также спустявременной интервал, определяемый параметром элемента задержки блока сравнения (см. фиг. 8), Параметр элемента задержки блока сравнения выбирается так, чтобы в случае прихода синхроимпульса не допустить установки в единичное положение триггера 4, который стоит в цепочке вслед за триггером канала, по которому.обеспечивается сохранение достоверности информации,

Пример. Пусть требуется сохранить достоверность по первому каналу, свободный доступ производится к третьему каналу,

5 на выходе блока сравнения, соответствующего третьему каналу, высокий уровень напряжения. На выходах всех элементов ИЛИ 48, кроме элемента ИЛИ 48 третьего канала, установится высокий уровень напряжения.

0 На выходе элемента 43 первого (опрашиваемого в данный момент) канала низкий уровень напряжения. Значит, на выходе элемента ИЛИ 47 первого канала не формируется сигнал сброса триггера 4 первого

5 канала и канал продолжает опрашиваться. На выходе элемента ИЛИ 47 третьего канала также нулевой сигнал, т.е. триггер 4 этого канала не обнуляется, а готов к переключению в еди1- ичное состояние по приходу с-иг0 напз установки. Так как все остальные каналы не опрашиваются, на выходах их элементов НЕТ 43, а значит, на выходах элементов ИЛИ 47, им соответствующих, и входах сброса триггеров 4 этих каналов будет сигнал высокого уровня. Синхроимпульс, поступивший на вход 22 блока свободного доступа, через элемент 14 45 и ИЛИ 49 третьего канала поступит на выход 37 блока свободного доступа, а значит, на вход установки соответствующего триггера

4 и переключит его. Начнется опрос третьего канала.

Синхроимпульс установит триггер 4 первого канала в исходное состояние, м опрос первого канала прекратится. При этом переключения триггера 4 второго канала не произойдет, так как на его входе сброса в течение некоторого времени присутствует сигнал сброса с выхода элемента ИЛИ 47. соответствующего второму каналу. Это время определяется параметром элемента задержки блока сравнения.

Режим адресного опроса каналов. На первом входе 24 управления устройства устанавливается низкий или высокий уровень напряжения в зависимости оттого, требуется ли обеспечить достоверность информации по каналу, при опросе которого будет начинаться адресный опрос, или нет.

На втором входе 33 управления высокий уровень напряжения, на третьем 34 низкий уровень напряжения. При этом на выходе элемента И-НЕ 62 блока 15 низкий уровень напряжения, и сигнал адреса в блок формирования адреса канала не поступает. На выходе элемента И 60 высокий уровень напряжения и сигнал адреса через него поступает на пятый вход 25 блока свободного доступа 14.

В дальнейшем работа устройства происходит так, как описано для режима свободного доступа к каналам при коррекции режима их опроса.

Таким образом, по сравнению с прототипом, изобретение обеспечивает расширение функциональных возможностей устройства за счет реализации возможности свободного доступа к каналам при коррекции режима их опроса и адресного опроса каналов.

Режим свободного Доступа позволяет по требованию потребителя прерывать цикл опроса в момент коррекции режима работы какого-либо канала и получать информацию по данному каналу, после чего восстанавливать циклический опрос начиная с этого канала. Это позволяет повысить эффективность работы коммутатора, особенно в нештатных ситуациях, за счет обеспечения возможности оперативного доступа к аномальному каналу с одновременным изменением информационного потока по этому каналу.

Режим позволяет после запроса канала осуществить возврат к исходному каналу и с него продолжить прерванный цикл. В этом случае после обращения к требуемому каналу необходимо сделать доступ по исходному адресу.

Режим адресного опроса каналов позволяет обеспечить оперативный доступ к любому каналу по требованию потребителя. Названные режимы позволяют обеспе5 чить динамический характер группового кадра по требованию потребителя. При этом сохранена возможность циклического опроса каналов.

Формула изобретения

0 1. Многоканальный коммутатор, содержащий блок формирования адреса канала, таймер, генератор тактовых импульсов и в каждом канале Д-триггер, выход которого соединен с выходной шиной данного канала. а синхронизирующий вход-с синхронизирующими входами Д-триггеров остальных каналов и выходом таймера, группа первых входов которого подключена соответственно к группе первых выходов блока формирования адреса канала, группа вторых входов соответственно к выходам Д-триггеров каждого канала, причем выход Д-триггера. за исключением Д-триггера последнего канала, связан с информационным входом Д5 триггера последующего канала, третий вход таймера соединен с выходом генератора тактовых импульсов, четвертый - с вторым выходом бока формирования адреса канала, пятый - с информационным входом устройства, отличающийся тем, что, с целью расширения области использования путем реализации свободного доступа к каналам при коррекции режима их опроса и адресного опроса каналов, дополнительно

5 введены блок свободного доступа, блок выбора режима, элемент ИЛИ и формирователь одиночного импульса, вход которого соединен с выходом таймера, а выход - с шестым входом таймера и входом элемента

0 ИЛИ, второй вход которого подключен к выходу Д-триггера последнего канала, а выход - к информационному входу Д-триггера первого канала, при этом второй вход формирователя одиночного импульса соединен с

5 вторым выходом блока формирования адреса канала и первым входом блока свободного доступа, группа вторых входов которого подключена соответственно к группе вторых входов таймера, третий вход соединен

0 с синхронизирующими входами Д-триггеров каналов, четвертый - с первым входом управления устройства, пятый - с первым выходом блока выбора режима, второй выход которого соединен с входом адреса блока формирования адреса канала, а первый, второй и третий входы - соответственно с входом адреса устройства, вторым и третьим входами управления устройства, а группа четвертых входов - соответственно с группой первых выходов блока свободного

доступа, группы вторых и третьих выходов которого подключены соответственно к входам установки и входам сброса Д-триггеров каналов, а четертый выход - к седьмому входу таймера.

2.Коммутатор по п. 1, о т л и ч а ю щ и йс я тем, что блок свободного доступа содержит элементы И, ИЛИ, а также по числу каналов логические элементы ЗАПРЕТ, вторые, третьи, четвертые элементы И,вторые, третьи, четвертые, пятые элементы ИЛИ, элементы задержки и блоки сравнения входы которых соединены между собой и с пятым входом блока свободного доступа, вторые входы-с выходами пятых элементов ИЛИ, входы которых соединены между собой и первым входом блока свободного доступаД вторые входы - с выходами HeTBepftJx элементов ИЛИ, входы которых подключены к выходам третьих элементов И, входы которых соединены между собой и

с третьим входом блока свободного доступа, четвертый вход которого соединен с входами четвертых элементов И, выходы которых через элементы задержки соединены с вторыми входами четвертых элементов ИЛИ, а вторые входы - с вторыми входами третьих элементов И, выходами соответствующих блоков сравнения и одноименными входами третьих элементов ИЛИ, за исключением одноименного третьего элемента ИЛИ, выходы которых соединены с входами элементов ЗАПРЕТ и вторых элементов И, вторые входы которых связаны между собой и четвертым входом блока совбодного доступа, а выходы - с первыми входами вторых элементов ИЛИ, вторые входы которых соединены между собой и с первым входом блока свободного доступа, третьи входы - с выходами элементов ЗАПРЕТ, при этом вторые входы блока свободного доступа связаны с инверсными входами соответствующих элементов, первые выходы его соединены с выходами соответствующих блоков сравнения и соответствующими входами элемента ИЛИ, выход которого подключен к входу элемента И, второй вход которого связан с четвертым входом блока свободного доступа, вторые выходы которого соединены с выходами соответствующих четвертых элементов ИЛИ, третьи выходы - с выходами соответствующих вторых элементов ИЛИ, а четвертый выход подключен к выходу элемента И.

3.Коммутатор по п. 1, о т л и ч а ю щ и йс я тем, что блок выбора режима содержит элементы ИЛИ-НЕ. ИЛИ, первый элемент

И, первый и второй элементы И-НЕ, а также группы вторых и третьих элементов И, причем входы 1-го элемента И в группе подключены к 1-му разряду первого входа блока выбора режима, вторые входы вторых элементов И подключены к выходу первого элемента И, а вторые входы третьих элементов И подключены к выходу второго элемента И-НЕ, вход которого соединен с входом первого элемента И и выходом элемента ИЛИ, а второй вход соединен с выходом первого элемента И-НЕ, вход которого соединен с вторым входом первого элемента И и выходом элемента ИЛИ-НЕ, второй вход соединен с третьим входом блока выбора режима и входом элемента ИЛИ, второй вход которого подключен к второму входу яблока выбора режима, при этом входы элемента ИЛИ-НЕ подключены соответственно к четвертым входам блока выбора режима, выходы 1-го второго элемента И в группе подключены к 1-му разряду первого выхода блока выбора режима, а выходы i-ro третьего элемента И в группе подключены к 1-му разряду второго выхода блока выбора режима.

4. Коммутатор по п. 1,отличающийс я тем, что таймер содержит группы элементов ИЛИ и Д-триггеров, дешифратор, первый и второй элементы ИЛИ, элемент И, элемент задержки, триггер режима, а также группы регистров, элементов задержки, вторых элементов ИЛИ, ключевых элементов и ждущих мультивибраторов, входы которых соединены соответственно с вторыми входами таймера, а выходы - с первыми входами ключевых элементов, вторые входы которых подключены к выходам соответствующих регистров, а одноименные разряды выходов ключевых элементов соединены с входами соответствующих элементов ИЛИ, выходы которых подключены к входу дешифратора в соответствии с номерами разрядов на входах элементов ИЛИ, при этом первые входы таймера соединены с соответствующими входами сброса регистров и через элементы задержки - с входами записи регистров, информационные входы которых соединены между собой и с пятым входом таймера, третий вход которого соединен с первым входом элемента И и синхровходами Д-триггеров, выходы которых соединетны с информационными входами последующих Д-триггеров, за исключением последнего, а их входы сброса соединены с выходами соответствующих вторых элементов ИЛИ, первые входы которых соединены между собой и с седьмым входом таймера, вторые входы вторых элементов ИЛИ соединены между собой, с четвертым входом таймера и с входом установки триггера режима, вход сброса которого соединен с шестым входом таймера, а выход - с вторым входом элемента И, выход которого соединен с входом первого элемента ИЛИ, выход которого подключен к выходу таймера,, а второй вход соединен с выходом последнего Д-триггера и через элемент задержки - с третьим входом второго элемента ИЛИ, соответствующего последнему Д-триггеру, при этом

разряды выхода дешифратора в порядке убывания номеров подключены к входам установки Д-триггеров. кроме последнего, так, что старший разряд выхода подключен к входу установки первого Д-триггера, а младший - к входу установки предпоследнего Д-триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1988 |

|

SU1541764A1 |

| Многоканальный коммутатор | 1989 |

|

SU1661986A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2001 |

|

RU2195774C2 |

| Устройство для сопряжения ЭВМ с магистралью | 1988 |

|

SU1605242A1 |

| СИСТЕМА РАДИОСВЯЗИ С ПОДВИЖНЫМИ ОБЪЕКТАМИ | 2003 |

|

RU2263401C2 |

| Устройство для сопряжения цифровых вычислительных машин с каналами связи | 1985 |

|

SU1287171A1 |

| Система радиосвязи с подвижными объектами | 1986 |

|

SU1401626A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1462341A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

Изобретение относится к радиоэлектронике, в частности .к злектронной коммутационной технике. В многоканальном коммутаторе реализуется свободный доступ к каналам при коррекции режима их опроса и адресного опроса каналов. Многоканальный коммутатор содержит один блок формирования адреса канала, один таймер, один генератор тактовых импульсов, в каждом канале один Д-триггер, а также один формирователь одиночного импульса, один элемент ИЛИ, один блок свободного доступа и один блок выбора режима. 3 з. п. ф. и 8 ил.

фиги

L.

Григ. Л

а

12f

Г Л

1Ш

PW2.4

YY

г 7

29 Фиг. e

| Многоканальный коммутатор | 1984 |

|

SU1226644A2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1992-12-07—Публикация

1991-05-12—Подача