Изобретение относится к вычнслительнон технике и может быть иснользовано в качестве формировате.тя прямоугольных импульсов в устройствах автоматики и вычислительной техники.

Известен формирователь импульсов, содержащий «-потенциальных инверторов, соединенных между собой последовательно, параллельно одному из которых подключен времязадающий конденсатор.

Предлагаемый формирователь отличается от известного тем, что в него введены два дополнительных элемента «НЕ-И транзисторно-транзисторной логики, каждый из которых содержит два выхода, эмиттерный и коллекторный выходы и вход одного из них подключен соответственно к коллекторному и эмиттерному входу и выходу другого, вход первого и выход последпего л-потенциальных инверторов подключены ко в.ходам и эмиттерным выходам упомянутых дополнительных элементов «НЕ-И траизисторно-транзисториой логики.

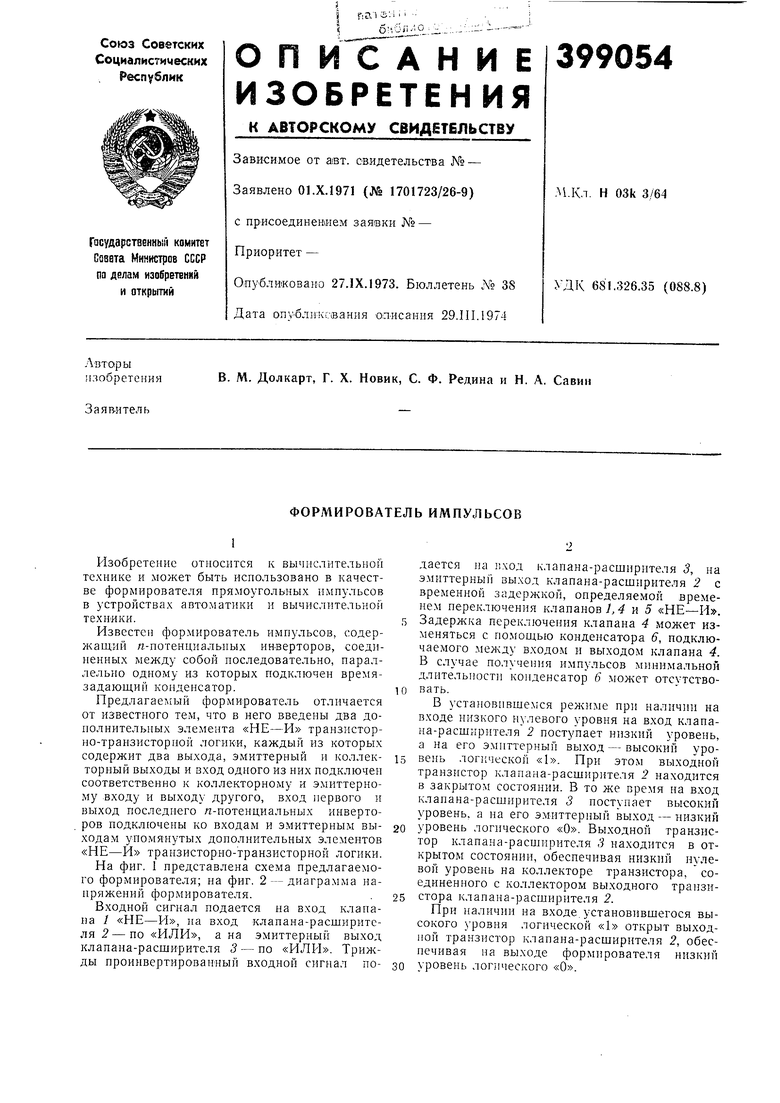

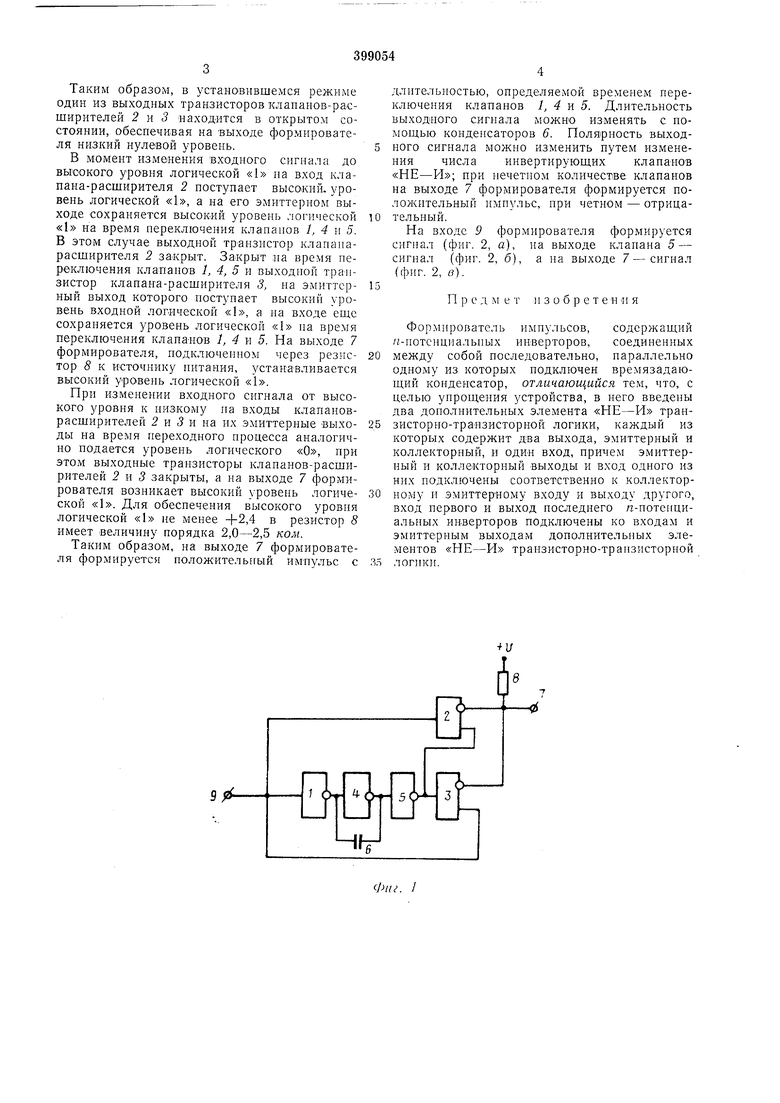

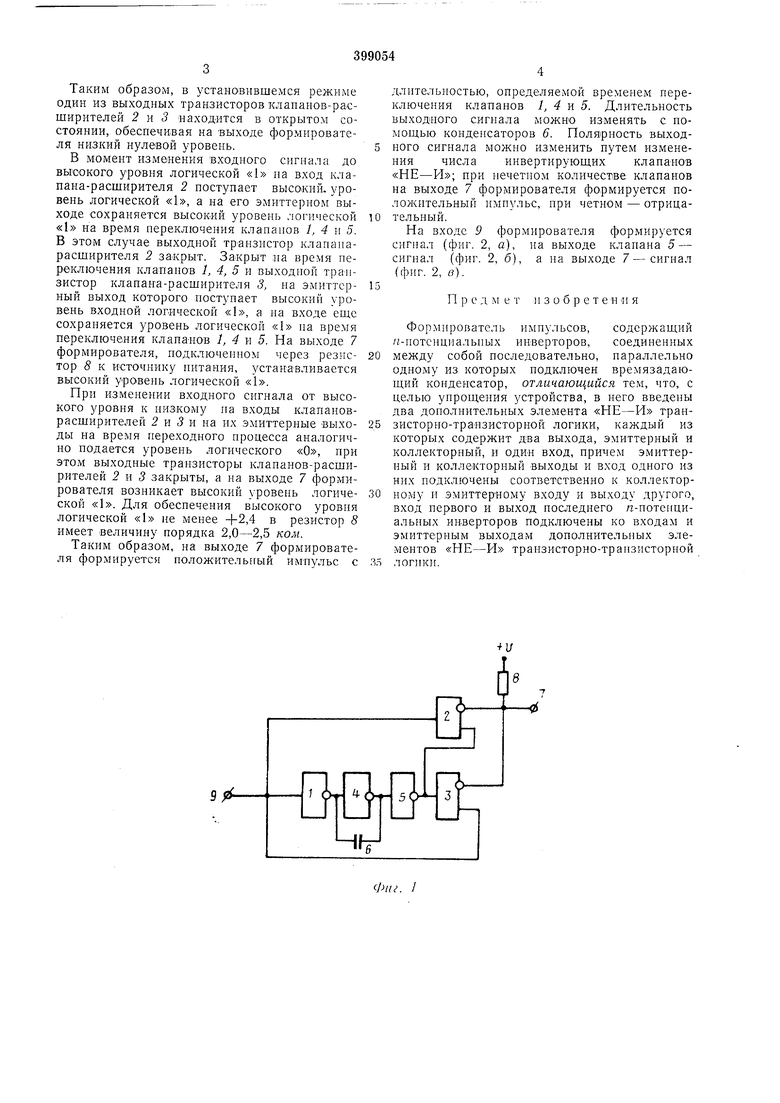

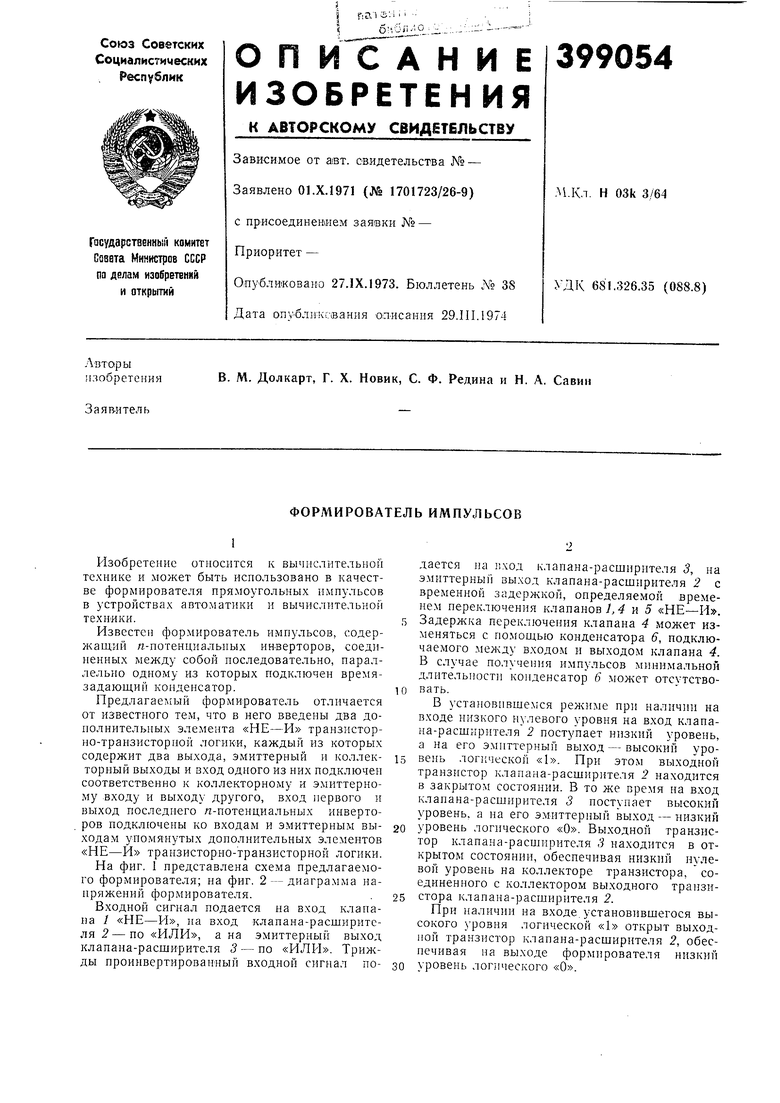

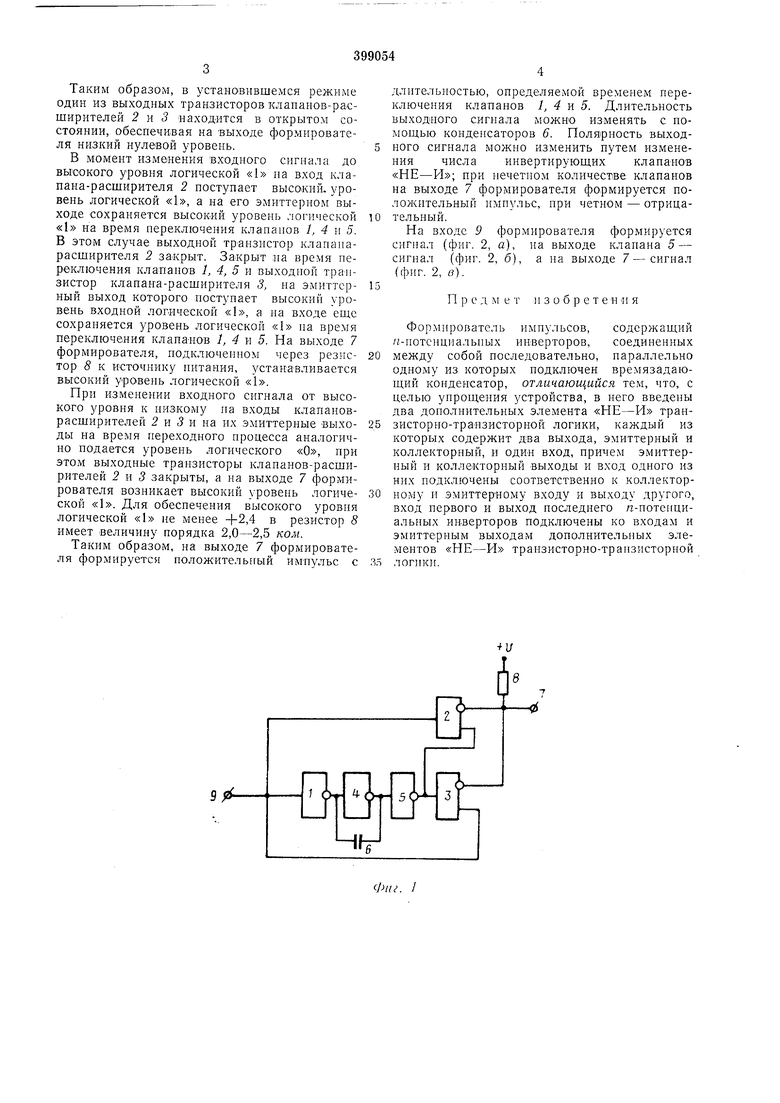

На фиг. 1 представлена схема предлагаемого формирователя; на фиг. 2 - диаграмма напряжений формирователя..

Входной сигнал подается на вход клапана / «НЕ-И, ла вход клапана-расширителя 2 - по «ИЛИ, а на эмиттерный выход клапана-расширителя 3 - по «ИЛИ. Трижды ироиивертированный входной сигнал подается на иход клапана-расширителя 3, на эмиттерный вы.ход клапана-расширителя 2 с временной задержкой, определяемой временем переключения клапанов Л и 5 «НЕ-И. Задержка переключения клапана 4 может изменяться с помощью конденсатора 6, подключаемого между входом и выходом клапана 4. В случае получения импульсов минимальной длительности конденсатор 6 может отсутствовать.

В установившемся режиме при наличии на входе низкого нулевого уровня на вход клапана-расширителя 2 поступает низкий уровень, а на его эмнттерный выход - высокий уровень логической «I. При этом выходной транзистор клапана-расширителя 2 находится в закрытом состоянии. В то же время на вход кланана-расширителя 3 поступает высокий уровень, а на его эмиттерный выход - низкий уровень логического «О. Выходной транзистор клапана-расширителя 3 находится в открытом состоянии, обеспечивая низкий нулевой уровень на ко.тлекторе транзистора, соединенного с коллектором выходного транзистора клапана-расширителя 2.

При наличии на входе, установившегоея высокого уровня логической «1 открыт выходной транзистор клапана-расширителя 2, обеспечивая на выходе формирователя низкий уровень логического «О.

Таким образом, в установившемся режиме один из выходных транзисторов клапанов-расширителей 2 и 3 находится в открытом состоянии, обеспечивая на выходе формирователя низкий нулевой уровень.

В момент изменения входного сигнала до выоокого уровня логической «1 на вход клапана-расширителя 2 поступает высокий, уровень логической «1, а на его эмиттерном выходе сохраняется высокий уровен логической «1 на время переключения клапанов /, 4 и 5. В этом случае выходной транзистор клапанарасширителя 2 закрыт. Закрыт на время переключения клапанов 1, 4, 5 и выходной транзистор клапапа-расширителя 3, на эмиттсрный выход которого поступает высокий уровень входной логической «1, а на входе еш,е сохраняется уровень логической «1 па время переключения клапанов 1, 4 и 5. На выходе 7 формирователя, подключенном через резистор 8 к источнику питания, устанавливается высокий уровень логической «1.

При изменении входного сигнала от высокого уровня к низкому па входы клапановрасширителей 2 и 3 н на их эмиттерные выходы на время переходного процесса аналогично подается уровень логического «О, при этом выходные транзисторы клапанов-расширителей 2 11 3 закрыты, а на выходе 7 формирователя возникает высокий уровень логической «1. Для обеснечения высокого уровня логической «1 не менее +2,4 в резистор 8 имеет величину порядка 2,0-2,5 ком.

Таким образом, на выходе 7 формирователя формируется положительный импульс с

длительностью, определяемой временем переключения клапанов 1, 4 и 5. Длительность выходного сигнала можно изменять с помощью конденсаторов 6. Полярность выходного сигнала можно изменить путем изменения числа инвертирующих клапанов «НЕ-И ; при нечетном количестве клапанов на выходе 7 формнрователя формируется положительный импульс, при четном - отрицательный.

На входе 9 формирователя формируется сигнал (фиг. 2, а), на выходе клапана 5 - сигнал (фиг. 2, б), а на выходе 7 - сигнал (фиг. 2, в).

П р с д мет н 3 о б р е т е н н я

Формирователь имнульсов, содержащий /г-нотенциальных инверторов, соединенных

между собой последовательно, параллельно одному из которых подключен времязадающий конденсатор, отличающийся тем, что, с целью унрощения устройства, в него введены два дополнительных элемента «НЕ-И транзисторно-транзисторпой логики, каждый из которых содержит два выхода, эмиттерный и коллекторный, и один вход, причем эмиттерный и коллекторный выходы и вход одного из них подключены соответственно к коллекторному и эмиттерному входу и выходу другого, вход первого и выход последнего п-потепциальных инверторов подключены ко входам и эмиттерным выходам дополнительных элементов «НЕ-И транзисторно-транзисторной

логики.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Одновибратор | 1978 |

|

SU733088A1 |

| Ждущий генератор импульсов | 1980 |

|

SU894832A1 |

| Формирователь импульсов | 1981 |

|

SU1018213A1 |

| Генератор импульсных сигналов | 1978 |

|

SU780165A1 |

| Формирователь импульсов | 1979 |

|

SU841096A1 |

| Формирователь импульсов | 1978 |

|

SU750701A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ПРЯМОУГОЛЬНЫХ | 1973 |

|

SU372662A1 |

| Многоканальный селектор импульсов по длительности | 1972 |

|

SU444313A1 |

| Одновибратор | 1980 |

|

SU892665A1 |

л

Авторы

Даты

1973-01-01—Публикация