1

Изобретение относится к автоматике и вычислительной технике. Устройство предназначено для сдвига двоичных кодов, а для, преобразования последавательного двоичного кода в па|раллельный и обратно.

Известны сдвигающие регистры, каждый разряд которых содержит триггер, выходы которого через выходные ве1нтили соединены с соответствующими входами триггера последующего разряда.

Очередной разряд кода вводят в такие регистры не ранее чем за коичатся переходные процессы в разрядах регистра, .вызва)ные вводом предыдущего разряда кода, а отказ одного разряда .приводит к пеработоспособности всех дальнейших.

Предлагаемый сдвигающий регистр отличается тем, что управляющие входы выходных вентилей всех разрядов каждой группы и входных КЛ аланов той же группы сое.динены с соответствующим выходом распределителя, входы входных клапа.пов всех групп разрядов соединены с информационными вхо.да.чи устройства, выходы выходных вентилей последних разрядов всех групп соединены со входами соответствующих собирательных с-хем.

Это позволяет повысить быстродействие устр.ойстъа благодаря вводу и выводу, кода, период следования разря.дов котО(рого короче

переходных процессов в разрядах регистра, а также повысить его надежность (при отказе ОДНО.ГО разряда теряют работоспособность сле.дующие разряды лишь одной группы).

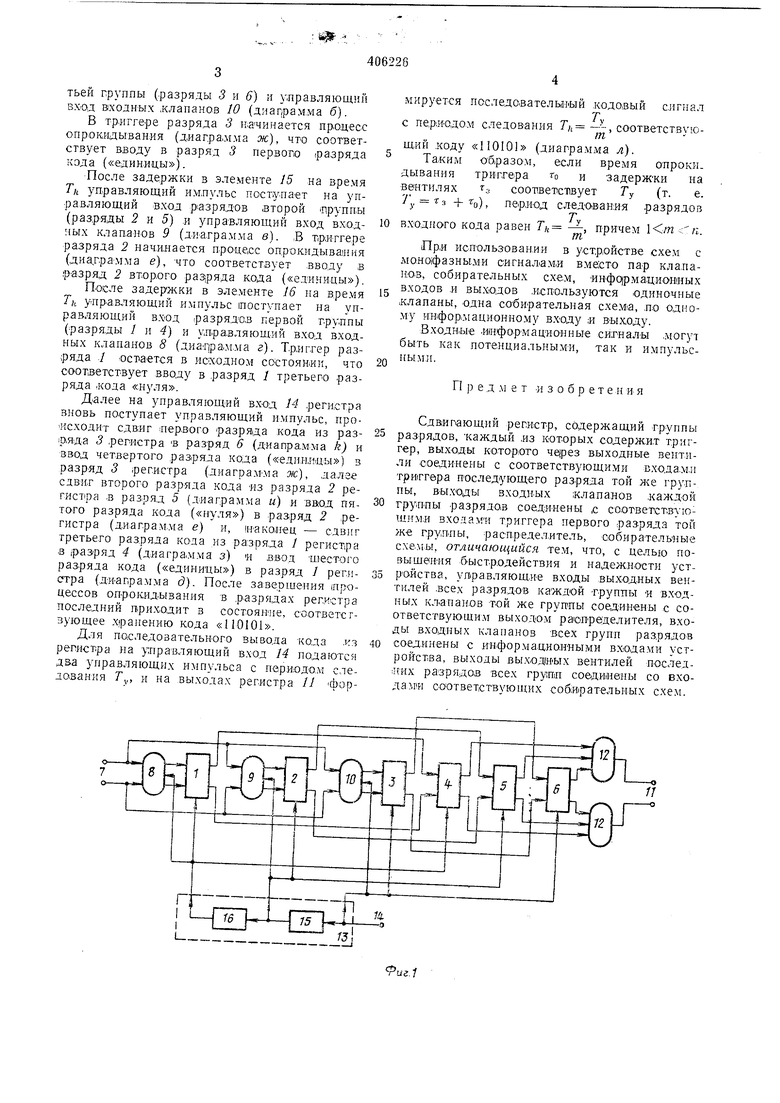

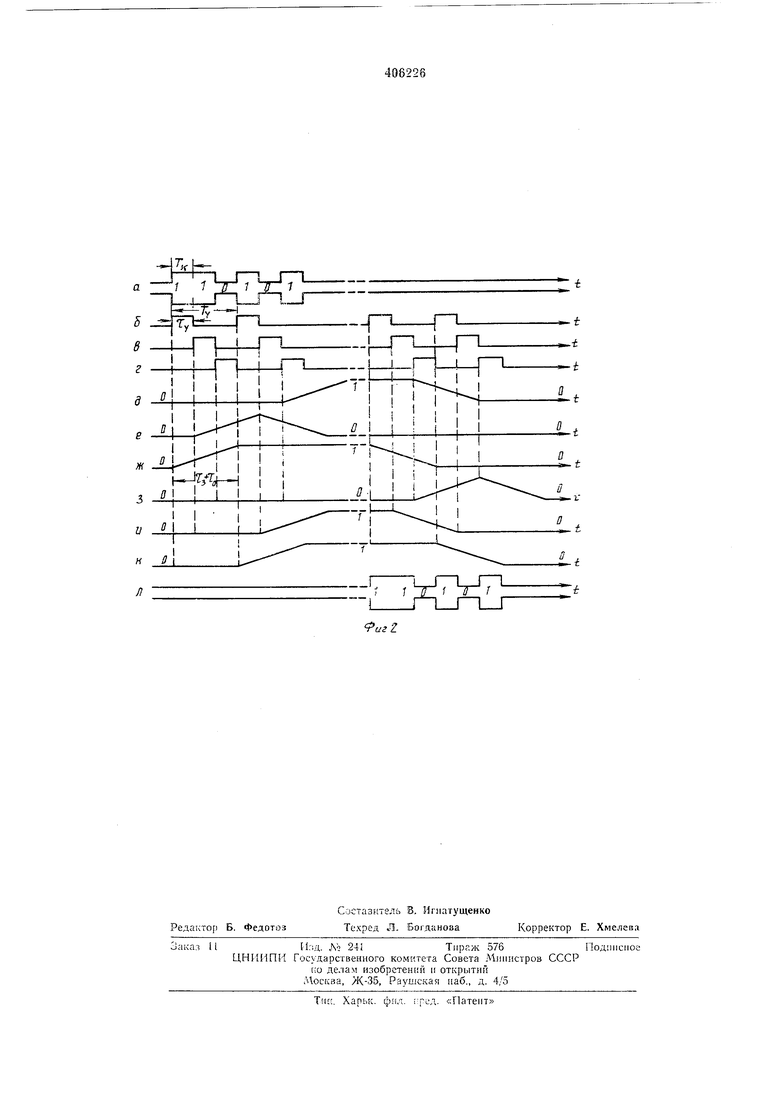

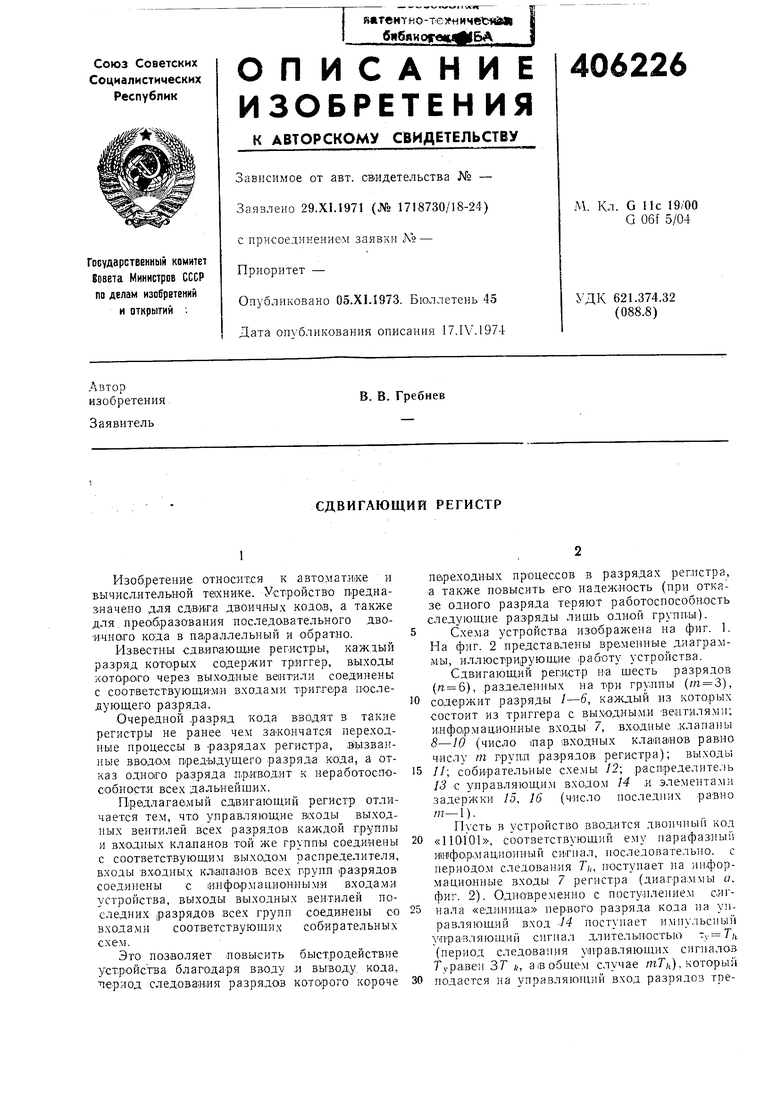

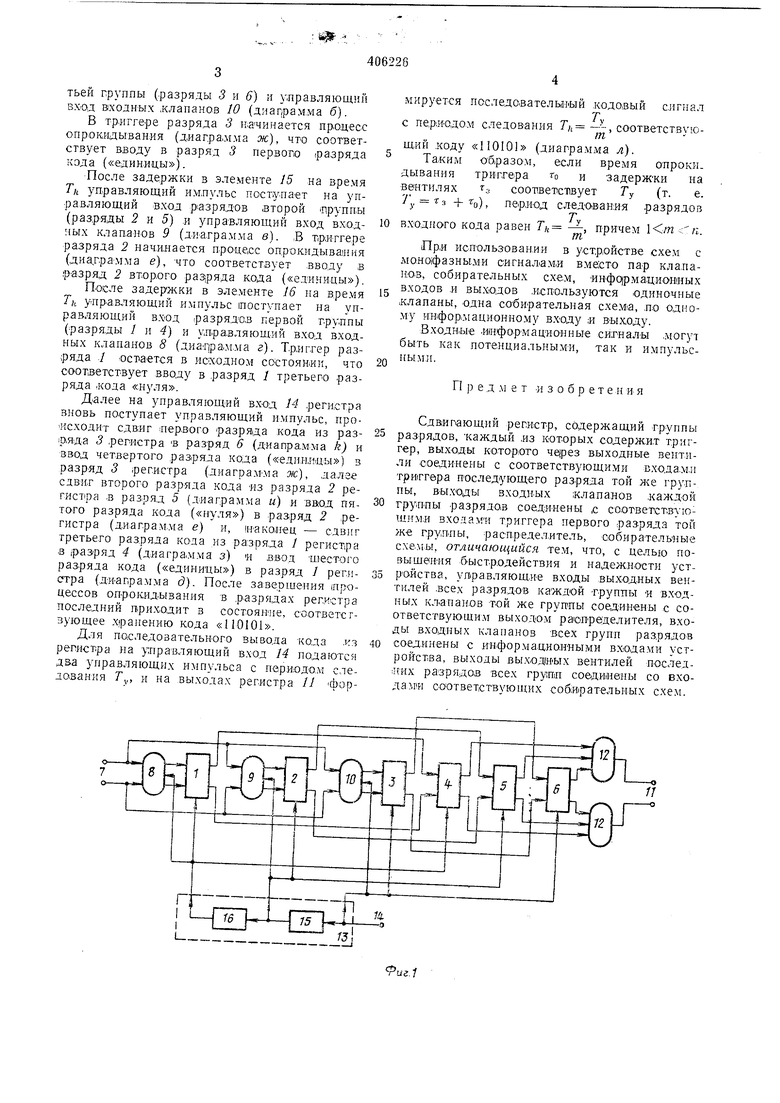

Схем.а устройства изображена на фиг. 1. На фиг. 2 пре.дставлены временные диаграммы, иллюстрирующие работу устройства.

Сдвигающ.ий регистр шесть разрядов (п б), раз.деленпых па три группы (т 3), содержит разряды 1-6, каждый из которых состоит из триггера с выходными Велгилямп; ииформацио.н.ные входы 7, входные .клапа ы 8-10 (число 1пар (В.ходных клапанов равно числу т групд разрядов регистра); выходы /У; собирательные схемы 12; распределитель 13 с управляющи.м входом 14 .и элементами задержки 15, 16 (число последних равно т).

Пусть в устройство ВВО.Д.ИТСЯ КО.Д

«11Q101, соответствующий ему парафазныГ; и1Н форл1аци.онный сигнал, носледовательпо. с периодом следов ания Г/,, поступает па информационные входы 7 регистра (диагра.ммы а. фиг. 2). Одновременно с постунле)ие.м сигнала «единица первого разряда кода на управляющий вход 14 поступает импульсный управляющий сигнал длительностью (период следования учнравляющих сигналов Туравеи ЗГ , а IB общем случае ), который по.дается на управляюнип вхо.д разрядов третьей группы (.разряды 3 и 6) и управляющий BXiQ,i входных ,клапанов 10 (диапрамма б).

В тр.игг&ре разряда 3 кйчинается пр оцесс опрокидывания (диаграмма ж), что соответствует вводу в разряд 3 первого .разряда кода («единицы).

После задержки в элементе 15 на время ГА управляющий имлульс псстулает на управляющий вход р азрядов .второй 1Г,рупиы (разряды 2 н 5) я управляющий вход входных клааанов 9 (диаграмма в). В триггере разряда 2 нач,и,нается процесс опрокндываякя (диаграмма е), что соответствует .вводу в разряд 2 BT.op.oro разряда кода («единицы). По.сле задержки в элементе 16 на время TI, упр.авляющий импульс поступает па управляющий вХОд разрядов первой группы (разряды / и 4) и упра.вляющий вход вхо.дных клапанов 8 (диагралг.ма г). Триггер разряда / в исходном состоянии, что соответствует вводу в разряд / третьего разряда .кода «нуля.

Далее на управляющей вход 14 регистра вновь поступает управляющий импульс, происходит сдвиг лер.вого разряда кода из раз1ряда 3 регистра В разряд 6 (диапрамма k) и ввод четвертого разряда кода («еди.Екаы) в разряд 3 регистра (днаграмма ж), далее сдвиг второго разряда кода -из разряда 2 регистра .в разряд 5 (диаграмма и) и ваод пятого разряда кода («нуля) в разряд 2 регистра (диаграм.ма е) и, in-aKOweu - сдвиг третьего разряда кода из разря.да / регистра в разряд 4 (диагра.мма з) и ввод uiecToro разряда кода («единицы) в разряд / регистра (диаграмма д). После завершения (процессов опрокидывания в разрядах регистра последний приходит в состояш е, соответсгзующее хранению кода «110101.

Для последовательного вывода кода .из регистра на у;правляющий вход 14 подаются два управляющих импульса с периодом следования Г,, и на выходах регистра 11 формируется последо.ватель/НЫЙ .кодовый сигнал с периодом следов ания , соответствуюiTL

щ.ий .коду «110101 (диаграмма л).

образом, если время опрокиТакимтриггера fo и задержки на дывания

(т.

е.

соотаетствует вентилях ; 7, -Сз + fa),

пер.иод следования разрядов Т,

входного кода равен Г/, - причем Km п.

Пр,и использовании в устройстве схем с монофазными сигнал.амй вместо пар кла.панов, собирательных схем, инфqpмa.ци. входов .и выходов ,исп.о.льзуются одиночные .клапаны, о.дна собирательная cxeMia, .по одному ивфор.мационному входу и выходу.

Входные .ииформационные сигналы .могут быть как потенциальными, так и импульсными.

П р е .д м е т .изобретен и я

Сдвигающий регистр, содержащий группы

разрядов, каждый ,из которых содерж.ит триггер, выходы которого выходные вентили соединены с соответствующими входа.м.и триггера последующего разряд.а той же гр}п пы, выходы входных клапанов .каж.дой

труппы разрядов соединены ,с соответствую шим;и входами триггера первого разряда той же гру.п.пы, распредел.итель, собирательные схемы отличающийся тем, что, с целью повыщен ия быстродействия и надеж.н.ости устройства, управляющ.Ие входы .выходных вентилей .всех разрядов каждой -группы и входных клапанов той же группы соединены с соответствующим выходом распределителя, входы входных клапанов всех групп разрядов

соединены с информацио.ниыми входами устройства, выходы выходИЫХ вентилей по.след;них разрядов всех групп соединены со входам и соответ,ствуюи1их собирательных схем.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД | 1970 |

|

SU271917A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1971 |

|

SU317082A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР С ЗАПОЛНЕНИЕМ ОПОРНОГО СЧЕТЧИКА МНОГОРАЗРЯДНЫМИ КОДАМИ | 1968 |

|

SU206911A1 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Устройство задержки | 1990 |

|

SU1750036A1 |

| Устройство задержки | 1981 |

|

SU997240A1 |

| Преобразователь код-сдвиг фазы | 1972 |

|

SU439917A1 |

| Устройство для обмена с накопителями на магнитных дисках | 1973 |

|

SU737984A1 |

| Устройство для декодирования манчестерского кода | 1986 |

|

SU1383510A1 |

| Устройство для умножения двоичных чисел | 1973 |

|

SU482741A1 |

Авторы

Даты

1973-01-01—Публикация