Изобретение относится к об.пасти передачи naiiuw x и предназначено для испол1: зования в сетях передачи данных .

Целью изобретения является повы- шение достоверности устройства.

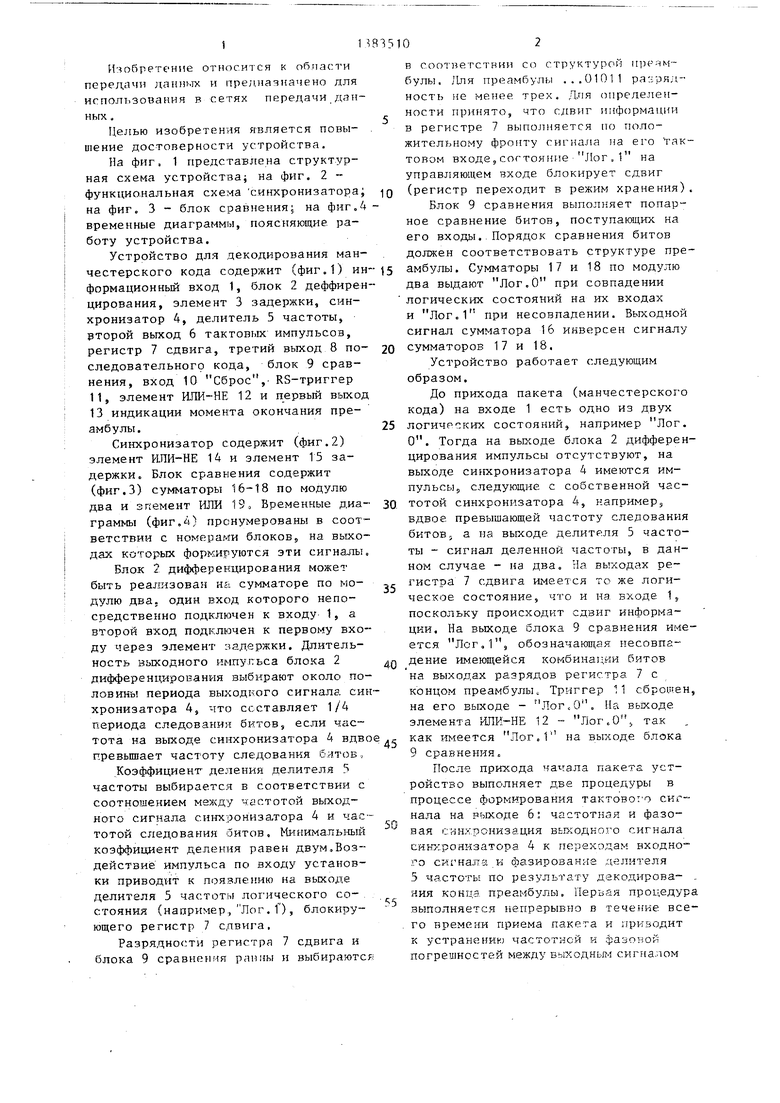

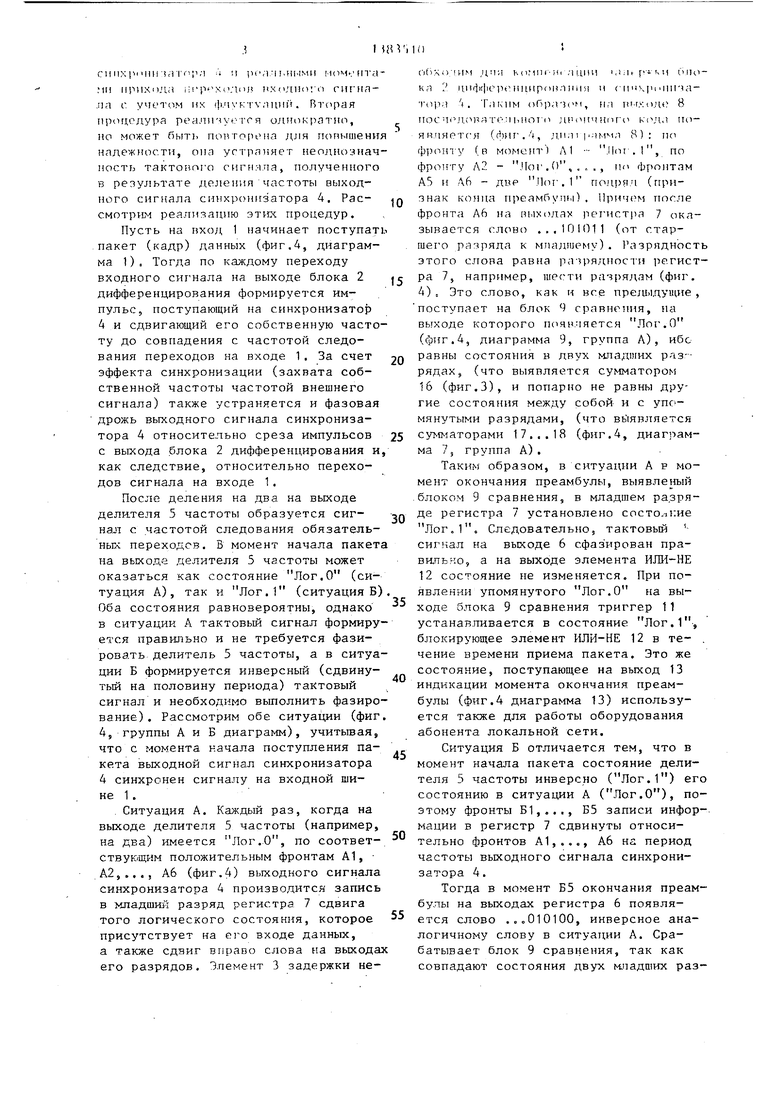

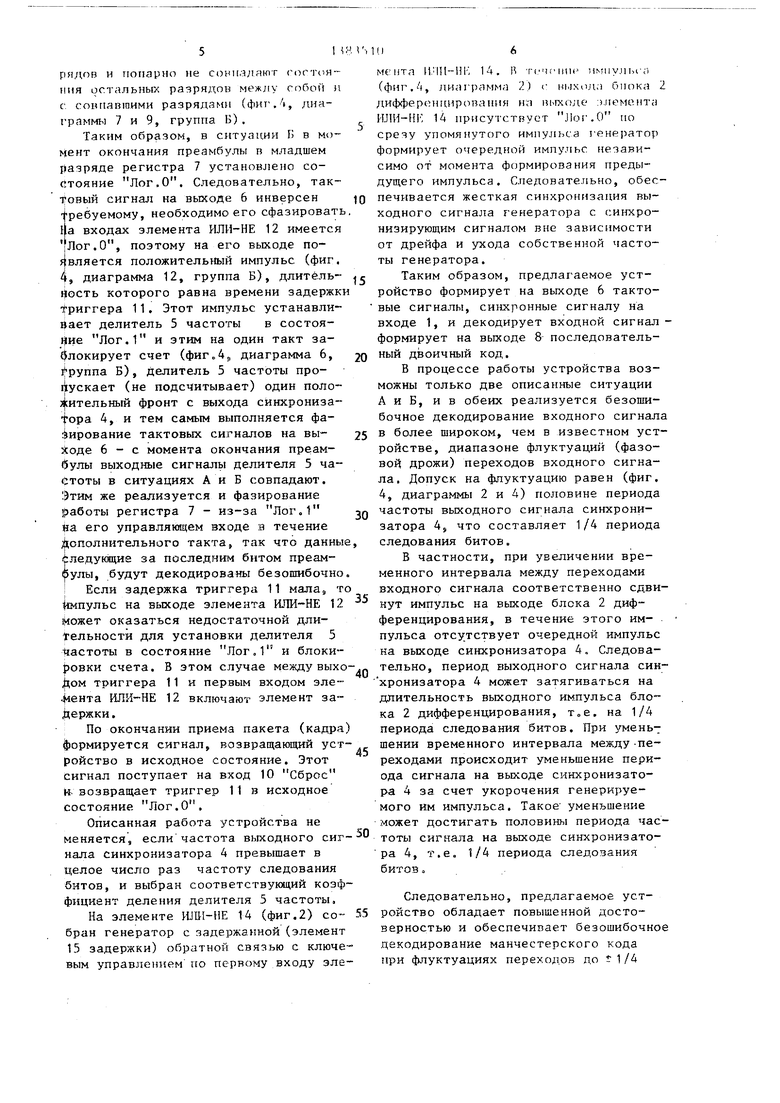

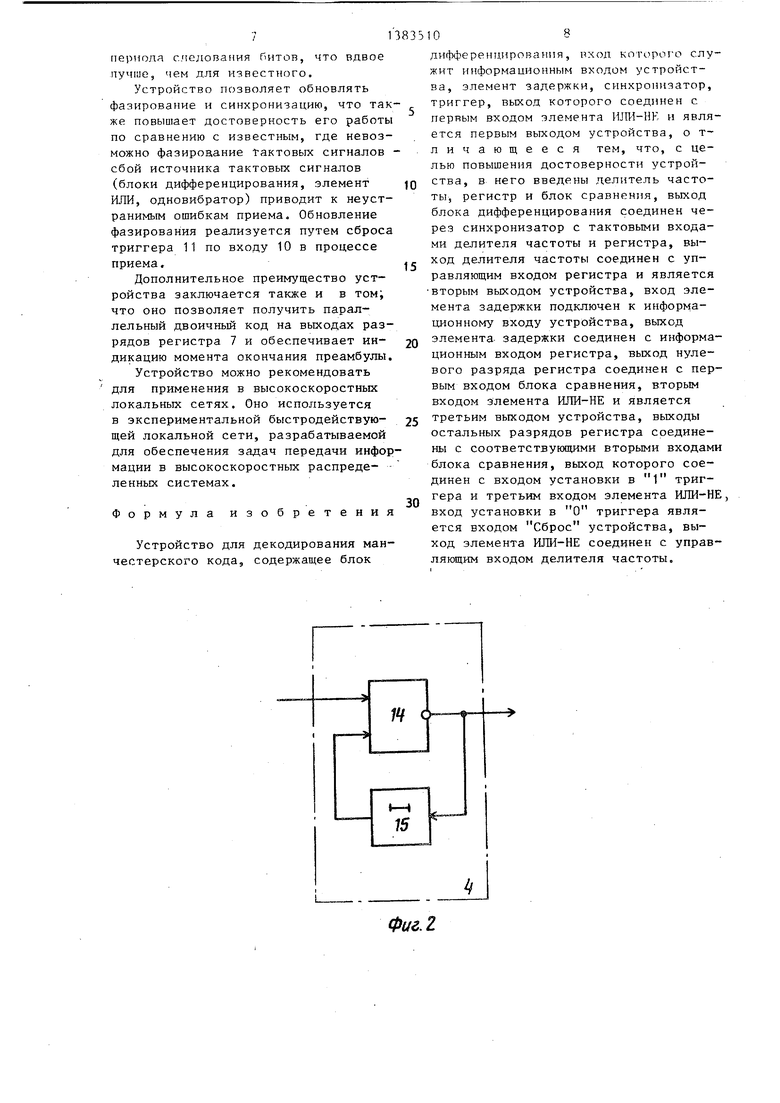

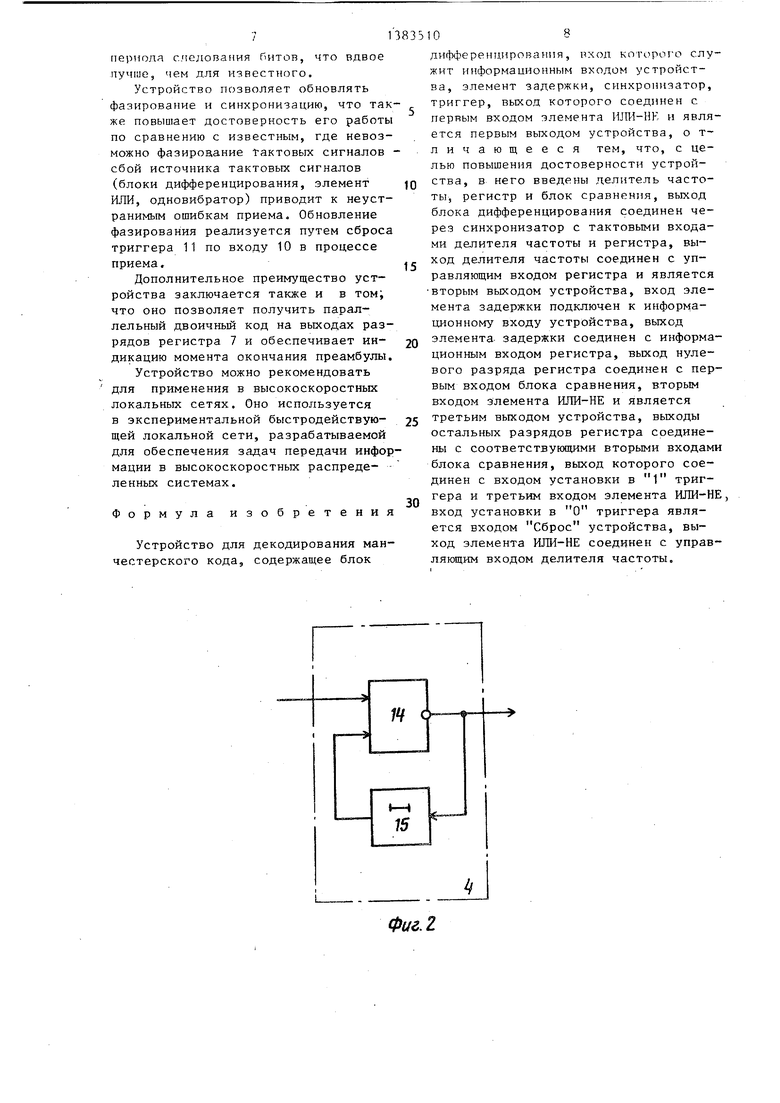

На фиг. 1 представлена структурная схема устройства; на фиг, 2 - функцио.нальная схема синхронизатора; на фиг, 3 - блок сравнения; на фиг,4 временные диаграммы, поясняющие работу устройства.

Устройство для декодирования манчестерского кода содержит (фиг,1.) информационный вход 1, блок 2 деффирен циррвания, элемент 3 задержки, синхронизатор 4, делитель 5 частоты, зторой выход 6 тактовых импульсов, регистр 7 сдвига, третий выход 8 последовательного кода, блок 9 сравнения, вход 10 Сброс,- RS-триггер 11, элемент ИЛИ-НЕ 12 и первый выход 13 индикации момента окончания преамбулы.

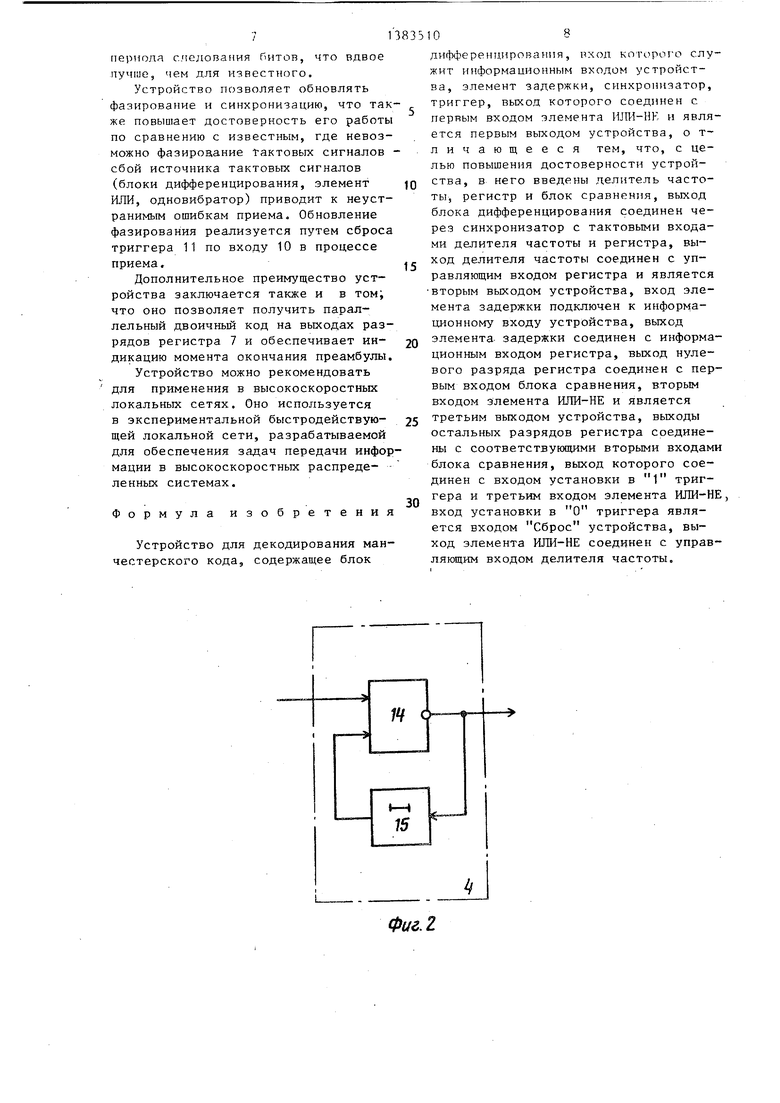

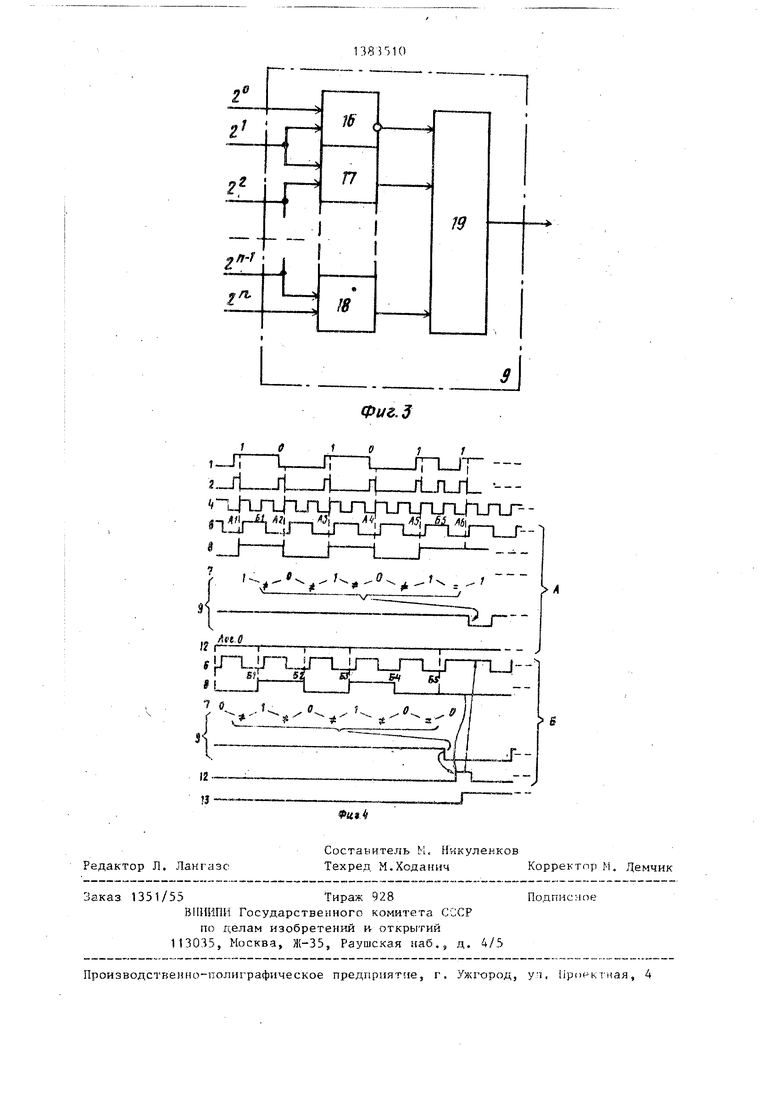

Синхронизатор содержит (фиг,2) элемент ИЛИ-НЕ 14 и элемент 15 задержки. Блок сравнения содержит (фиг,3) сумматоры 16-18 по модулю два и зпемент ИЛИ 19, Временные диа- граммьт (фиг,Д) пронумерованы в соответствии с нo 5epaми блоковs на вьпсо- дах которых формируются эти сигналы,

Блок 2 дифференцирования может быть реализован на сумматоре по модулю два. один вход которого непосредственно подключен к входу- 1, а второй вход подключен к первому входу через элемент задержки. Длительность выходного импульса блока 2 дифференцироЕЗния выбирают около половины периода выходного сигнала синхронизатора 4, что составляет 1/4 периода следования битов, если частота на выходе синхронизатора 4 вдво превьшает частоту следования битов..

Коэффициент деления делителя частоты выбираете. в соответствии с соотношением между частотой выходного сигнала синхронизатора 4 и частотой следования битов. Минимальный коэффициент деления равен двум,Воздействие импульса по входу установки приводит к поя.злению на выходе делителя 5 частоты лог ического со- , стояния (например, Лог, 1), блокирующего регистр 7 сдвига.

Разрядности регистра 7 сдвига и блока 9 сравнения раины н выбираются

0

5

0

5

0

5

0

5

0

5

в соот етствни со структурой црряи- булы. Для преамбулы ,..01011 разрядность не менее трех. Для определеи- ности принято, что сдвиг ниформаиии в регистре 7 выполняется по положительному фронту сигнала на его YaK- товом входе,согтояние Лог.1 на управляющем входе блокирует сдвиг (регистр переходит в режим хранения).

Блок 9 сравнения выполняет попарное сравнение битов, поступающих на его входы. Порядок сравнения битов должен соответствовать структуре преамбулы , Сумматоры 17 и 18 по модулю два выдают Лог,0 при совпадении логических состояний на их входах и Лог,1 при несовпадении. Выходной сигнал сумматора 16 инверсен сигналу сумматоров 17 и 18,

Устройство работает следующим образом,

До прихода пакета (манчестерского кода) на входе 1 есть одно из двух логических состояний, например Лог. О, Тогда на выходе блока 2 дифференцирования импульсы отсутствуют, на выходе си гхронизатора 4 имеются импульсы, следующие с собственной частотой синхронизатора 4, например, вдвое превышающей частоту следования битовJ а на выходе делителя 5 частоты - сигнал деленной частоты, в данном случае - на два. На выходах регистра 7 сдвига имеется то же логическое состояние, что и на входе 1, поскольку происходит сдвиг информации. На выходе блока 9 сравнения имеется Лог,, обозначающая несовпадение имеющейся комбинаг ии битов на выходах разрядов регистра 7 с концом преамбулы. Триггер 11 сброшен, на его выходе - Лог«О, На выходе элемента ИЛК-НЕ 12 - Лог.О, так как имеется Лог,1 на выходе блока 9 сравнения.

После прихода начала пакета устройство выполняет две процедуры в процессе формирования тактовот о сигнала на рыходе 6: частотная и фазовая синхронизацил вькодного сигнала сишсронизатора 4 к переходам входного сигнала и фазирование делителя 5 частоть по результату декодирова- .. ния конца преамбулы. Первая процедура выполняется 1епрерывно в течеь ие всего времени приема пакета и приводит к устранении) частотней и фазовой погрешностей между вькодньш сигналом

ciinxpniiii ягг ; . 1 --t и рс.ч. п.иыми . fn a- МП прихода i;i p xo;iii ii.(b nic ;-n гигил- ла с учетом их (ji.fU KTvniuin. Вт(1рая прог1сдура реаличус-ггя однократно, но может быт1 noivroptMia для попышения надежности, она устраняет иеод.и)знач- ность тактового с нгр|.чла, полученного в результате деления частоты выходного сигнала синхронизатора 4. Рас- CMOTpiLM реализацию этих процедур.

Пусть на пход 1 начинает поступать .пакет (кадр) данных (фиг.4, диаграмма 1). Тогда по каждому переходу входного сигнала на выходе блока 2 дифференцирования формируется импульс, поступающий на синхронизатор 4 и сдвигающий его собственную частоту до совпадения с частотой следования переходов на входе 1, За счет эффекта синхронизации (захвата собственной частоты частотой внешнего сигнала) также устраняется и фазовая дрожь выходного сигнала синхронизатора 4 относительно среза импульсов с выхода блока 2 дифференцирования и, как следствие, относительно переходов сигнала на входе 1,

После деления на два на выходе дели.теля 5 частоты образуется сигнал с частотой следования обязательных переходов. В момент начала пакета на выходе делителя 5 частоты может оказаться как состояние Лог,О (ситуация А), так и Лог.1 (ситуация Б) Оба состояния равновероятны, однако в ситуации А тактовый сигнал формируется правильно и не требуется фазировать делитель 5 частоты, а в ситуации Б формируется инверсный (сдвинутый на половину периода) тактовый сигнал и необходимо выполнить фазирование) . Рассмотрим обе ситуации (фиг. 4, группы А и Б диаграмм), учитьгоая, что с момента качала поступления пакета выходной сигнал синхронизатора 4 синхронен сигналу на входной шине 1 .

. Ситуация А. Каждый раз, когда на выходе делителя 5 частоты (например, на два) имеется Лог..О, по соответствующим положительным фронтам А1, А2,..., А6 (фиг.4) выходного сигнала синхронизатора 4 производится запись в младший разряд регистра 7 сдвига того логического состояния, которое присутствует на входе данных, а также сдвиг вправо слова на выходах его разрядов. Элемент 3 задержки не0

5

0

5

(|t)Xi) ДП-,1 К(1МПГ-И| Л ЦИЧ MHtp-tKM IMIOкя 1 nn4 |it P пиирои л 1п1я II гипкр, .||ича- | о) 1 . Таким оПрлк м, нл .1,( 8

FIOC ЧСДСЧ ЯТС-Л ЬИОТ О ЛРНИЧНОГО К(ЧЛ ПОяи.ияется (фиг . (, ДМЛ1 8) : по фронту (в момент) Л1 - .Mot., по фронту Л2 Лог .0, , , . , п фронтам А5 и - ДВР Лог-.1 подря.г (признак конца преамГ у1и.|) , Причом после фронта А6 на выходах регистра 7 оказывается гл(1во .,.101011 (от старшего разряда к миадшему). Разрядность этого слова равна iia-н ядности регистра 7, например, шести разрядам (фиг. 4) , Это слово, как и все предыдуи|,ие , поступает на блок Ч сравнения, на выходе которого .чяется Лог. О (фиг.4, диаграмма 9, группа А), ибо равны состояния в двух младших разрядах, (что выявляется сумматором 16 (фиг.З), и попарно не равны другие состояния между собой и с упомянутыми разрядами, (что выявляется сумматорами 17...18 (фиг.4, диаграмма

группа А).

0

5

0

5

0

5

Таким образом, в ситуации А Р момент окончания преамбулы, выявленый .блоком 9 сравнения, в младшем разряде регистра 7 установлено состо, Лог,. Следовательно, тактовый - сигнал на выходе 6 сфаз ирован правильно, а на выходе элемента ИЛИ-НЕ 12 состояние не изменяется. При появлении упомянутого Лог.О на выходе блока 9 сравнения триггер 11 устанав.ливается в состояние Лог., блокирующее элемент ИЛИ-НЕ 12 в те- . чение времени приема пакета. Это же состояние, поступающее на выход 13 индикации момента окончания преамбулы (фиг.4 диаграмма 13) используется также для работы оборудования абонента локальной сети.

Ситуация Б отличается тем, что в момент начала пакета состояние делителя 5 частоты инверсно (Лог.1) его состоянию в ситуации А (Лог.О), поэтому фронты Б1,..., Б5 записи инфор-. мации в регистр 7 сдвинуты относительно фронтов А1,..., А6 на период частоты выходного сигнала синхронизатора 4.

Тогда в момент Б5 окончания преамбулы на выходах регистра 6 появляется слово ...010100, инверсное аналогичному слову в ситуации А. Срабатывает блок 9 сравнения, так как совпадают состояния двух м.падших разрядов и попарно не сони. гогтоя- нчя остальных разрядов межлу co6oii и с- сонпавгаими разрядами (фит-. , диа- 1 раммы 7 и 9, группа Б) .

Таким образом, в ситуации В в ми- Мент окончания преамбулы в младшем разряде регистра 7 установлено состояние Лог,О. Следовательно, тактовый сигнал на выходе 6 инверсен требуемому, необходимо его сфазировать

а входах элемента ИЛИ-НЕ 12 имеется

Лог.О, поэтому на его выходе по- 5|вляется положительный импульс (фиг. 4, диаграмма 12, группа Б), длительность которого равна времени задержки Триггера 11, Этот импульс устанавливает делитель 5 частоты в состоящие Лог.1 и этим на один такт заблокирует счет (фиг„4„ диаграмма 6, ifpynna Б), делитель 5 частоты пропускает (не подсчитывает) один поло- ительный фронт с выхода сйнхрониза- fopa 4, и тем самым выполняется фа- ирование тактовых сигналов на выходе 6 - с момента окончания преамбулы выходные сигналы делителя 5 частоты в ситуациях Аи Б совпадают. Этим же реализуется и фазирование 1 аботы регистра 7 - из-за Лог.1 на его управляющем входе в течение Дополнительного такта, так что данные Следующие за последнем битом преам- 9Улы, будут декодированы безошибочно Если задержка триггера 11 мала, то |1мпульс на выходе элемента ИЛИ-НЕ 12 Может оказаться недостаточной длительности для установки делителя 5 Частоты в состояние Лог,1 и блокировки счета. В этом случае между выхо триггера 11 и первым входом эле- -Иента ИЛИ-НЕ 12 включают элемент задержки.

По окончании приема пакета (кадра) формируется сигнал, возвращающий устройство в исходное состояние. Этот сигнал поступает на вход 10 Сброс К- возвращает триггер 11 в исходное состояние Лог.О.

Описанная работа устройства не меняется, если частота выходного сигнала синхронизатора 4 превышает в целое число раз частоту следования битов, и выбран соответствующий коэффициент деления делителя 5 частоты.

На элементе ШШ-НЕ 14 (фиг.2) собран генератор с задержанной (элемент 15 задержки) обратной связью с ключевым управлением по первому входу элеМ€ ИТЛ И, 1И-ЦК 14. fi Tl , UN I VJl I.l П

(фиг.), диаграмма 2) с пыхола биока 2 диффер«нцир(1ва11ия и а выходе :)лемемт;) И.ПН-НК U прясутствуст Лог.О по срезу упомянутого импульса генератор формирует очередной импульс независимо от момента формирования предыдущего импульса. Следовательно, обес0 печивается жесткая синхронизация выходного сигнала генератора с синхронизирующим сигналом вне зависимости от дрейфа и ухода собственной частоты генератора.

5 Таким образом, предлагаемое устройство формирует на выходе 6 такто- вые сигналы, синхронные сигналу на входе 1, и декодирует входной сигнал - формирует на выходе 8- последователь0 ный двоичный код.

В процессе работы устройства возможны только две описанные ситуации А и Б, ив обеих реализуется безошибочное декодирование входного сигнала

5 в более широком, чем в известном устройстве, диапазоне флуктуации (фазовой дрожи) переходов входного сигнала. Допуск на флуктуацию равен (фиг. 4, диаграммы 2 и 4) половине периода

0 частоты выходного сигнала синхронизатора 4, что составляет 1/4 периода

следования битов.

В частности, при увеличении временного интервала между переходами входного сигнала соответственно сдвинут импульс на выходе блока 2 дифференцирования, в течение этого импульса отсутствует очередной импульс на выходе синхронизатора 4. Следовательно, период выходного сигнала син- хронизатора 4 может затягиваться на длительность выходного импульса бло ка 2 дифференцирования, т„е. на 1/4 периода следования битов. При уменьшении временного интервала между -переходами происходит уменьшение периода сигнала на выходе синхронизатора 4 за счет укорочения генерируемого им импульса. Такое уменьшение может достигать половины периода частоты сигнала на выходе синхронизато- ра 4, т.е., 1/4 периода следования битов.

Следовательно, предлагаемое уст- 5 ройство обладает повышенной достоверностью и обеспечивает безошибочное декодирование манчестерского кода при флуктуациях переходов до t1/4

5

0

5

0

периода следования битов, что вдвое nyMiuc, чем для известного.

Устройство позволяет обновлять фазирование и синхронизацию, что также повышает достоверность его работы по сравнению с известным, где невозможно фазирование Тактовых сигналов сбой источника тактовых сигналов (блоки дифференцирования, элемент ИЛИ, одновибратор) приводит к неустранимым ошибкам приема. Обновление фазирования реализуется путем сброса триггера 11 по входу 10 в процессе приема.

Дополнительное преимущество устройства заключается также и в том; что оно позволяет получить параллельный двоичный код на выходах разрядов регистра 7 и обеспечивает индикацию момента окончания преамбулы.

Устройство можно рекомендовать для применения в высокоскоростных локальных сетях. Оно используется в экспериментальной быстродействующей локальной сети, разрабатываемой для обеспечения задач передачи информации в высокоскоростных распреде- ленных системах.

Формула изобретения

Устройство для декодирования манчестерского кода, содержащее блок

0

5

0

5

0

дифференцирования, вход служит информационным входом устройства, элемент задержки, синхронизатор, триггер, выход которого соединен с первым входом элемента ИЛИ-НЕ и является первым выходом устройства, о т- ли чающееся тем, что, с целью повышения достоверности устройства, в него введены делитель частоты, регистр и блок сравнения, выход блока дифференцирования соединен через синхронизатор с тактовыми входами делителя частоты и регистра, выход делителя частоты соединен с управляющим входом регистра и является вторым выходом устройства, вход элемента задержки подключен к информационному входу устройства, выход элемента задержки соединен с информационным входом регистра, выход нулевого разряда регистра соединен с первым входом блока сравнения, вторым входом элемента ИЛИ-НЕ и является третьим выходом устройства, выходы остальных разрядов регистра соединены с соответствукндими вторыми входами блока сравнения, выход которого соединен с входом установки в 1 триггера и третьим входом элемента ИЛИ-НЕ, вход установки в О триггера является входом Сброс устройства, выход элемента ИЛИ-НЕ соединен с управляющим входом делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| Цифроаналоговый преобразователь | 1987 |

|

SU1503072A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство для контроля информации в многоканальной локальной вычислительной сети | 1987 |

|

SU1446622A1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

| Цифровой синтезатор частот | 1986 |

|

SU1497704A1 |

| Преобразователь сдвига фазы в код скорости и ускорения | 1986 |

|

SU1358096A1 |

| Устройство для приема биимпульсных сигналов | 1988 |

|

SU1598191A1 |

| Устройство для контроля многоканальных импульсных последовательностей | 1989 |

|

SU1732332A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

Изобретение относится к областей передачи данных и предназначено для декодирования манчестерского кода в высокоскоростных локальных сетях передачи данных. Цепью изобретения является повышение достоверности. Устройство декодирует сигнал манчестерского кода, поступающий на информационный вход 1, выдает его в последовательном коде на выход 8, формирует тактовые импульсы на выходе 6 и сигнал окончания преамбулы на выходе 13. Устройство содержит блок 2 дифференцирования, элемент 3 задержки, синхронизатор 4, делитель 5 частоты, регистр 7 сдвига, блок 9 сравнения, вход 10 Сброс, триггер 11, элемент ИЛИ-НЕ 12 и выход 13 индика- а О дни момента окончания преамбулы. 4 ил.

Фиг. 2

Фиг.

1 в 101

П 1П 1Р-I

f-Ji Ц-1| I I-

п. J-1, jnJ-UriJ Lrinjl.f

, ,l,ii Аг ,™ Ji, - А, „М

g,4,i ii ( , («;

«--.JLh-L.

ft

,0.

,

s f-T..г 5

L.1

/

s

,J--

| Формирователь опорной частоты | 1972 |

|

SU457183A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Патент ФРГ № 3230836, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1988-03-23—Публикация

1986-10-30—Подача