1

Изобретение относится к вычислительной технике, а именно к вычитающим устройствам для нахождения разности последовательных двоичных кодов.

Известны устройства для получения разности двух чисел, представленных последовательными кодами, начиная со старших разрядов. Они состоят из преобразователей последовательных кодов в параллельные с последующим суммированием полученных чисел на параллельном сумматоре.

Однако известные устройства характеризуются большим объемом оборудования и недостаточно широкими функциональными возможностями.

Целью изобретения является сокращение объема оборудования и расширение функциональных возможностей устройства.

Для этого первый вход устройства подключен к первому входу первой схемы И и к первому входу схемы равнозначности, а через инвертор - к первому входу второй схемы И и ко второму входу схемы равнозначности, другой вход устройства соединен со вторым входом второй схемы И и с третьим входом схемы равнозначности, а через инвертор со вторым входом первой схемы И и с четвертым входом схемы равнозначности, выход первой схемы И подключен к одному из входо:в первой схемы ИЛИ и к единичному входу первого триггера, нулевой выход которого подключен к третьему входу второй схемы И, выход которой соединен с другим входом первой схемы ИЛИ и с единичным входом второго триггера, нулевой выход которого подключе 1 к третьему входу первой схемы И, выход первой схемы ИЛИ соединен с первыми входами каждой из Л схем И первой группы, выход схемы равнозначности подключен к первым

входам каждой из Л схем И второй группы, единичные выходы первого и второго триггеров через вторую схему ИЛИ подключены к первому входу третьей схемы И, второй вход которой соединен с третьим входом устройства, выход третьей схемы И соединен с единичным входом третьего триггера, единичный выход которого подключен ко вторым входам каждой из Л схем И первой и второй групп и к первому входу четвертой схемы И, третьи

входы каждой из Л схем И первой и второй групп соединены соответственно с V управляющими щинами устройства, второй вход четвертой схемы И соединен с (Л-f 1)-ой управляющей шиной, выход первой схемы И

первой группы соединен с первым выходом устройства, а выходы остальных схем И первой группы соединены соответственно с первыми входами {N-1) схем ИЛИ, вторые входы которых соединены с выходами соответствуюHUIX схем И второй группы, а входы N-ой схемы ИЛИ соединены с выходом Л-ной схемы И второй группы и выходом четвертой схемы И.

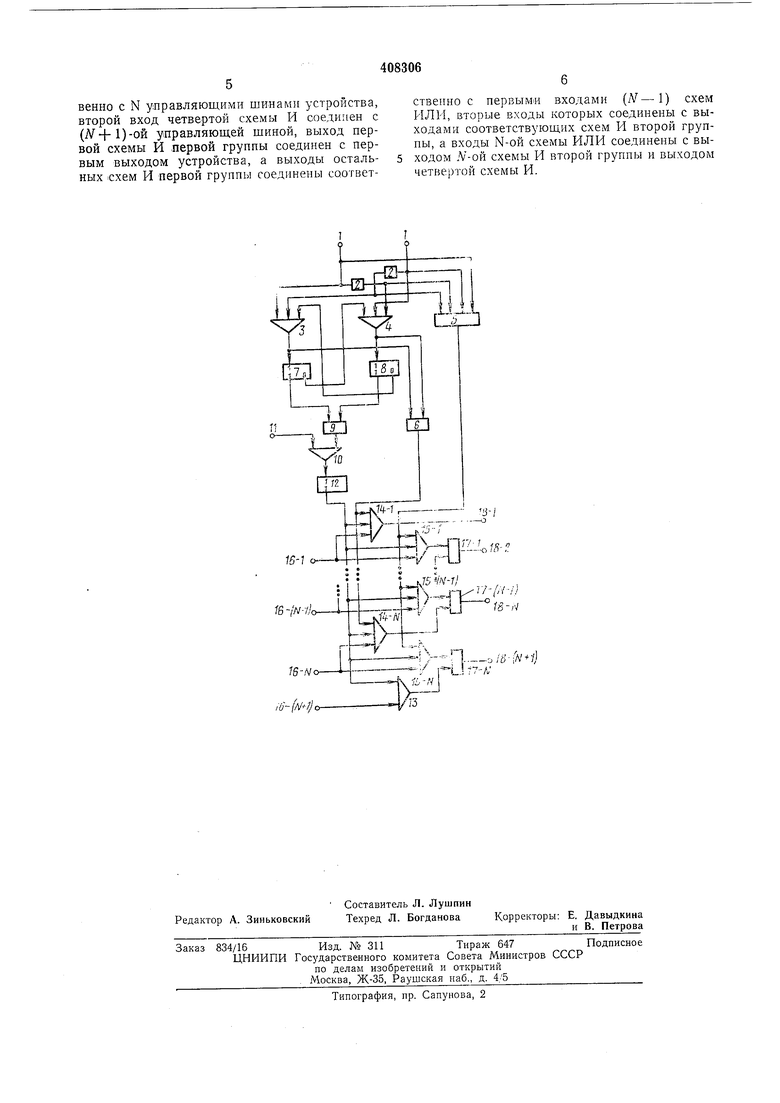

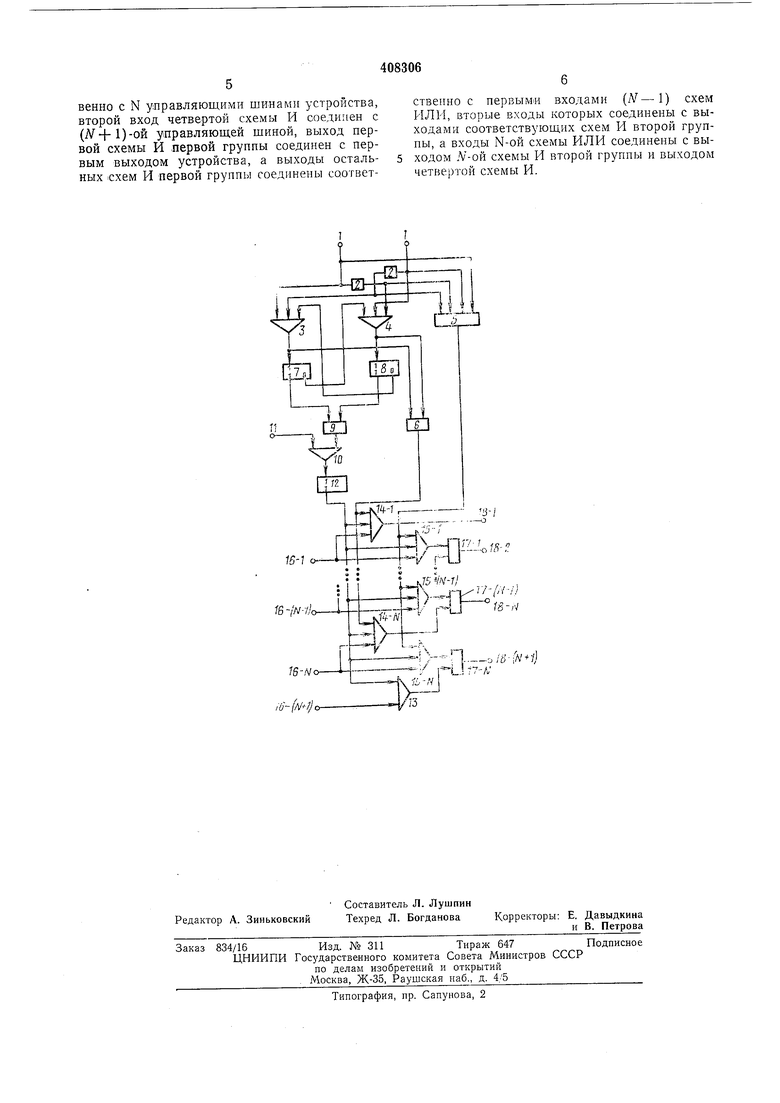

На чертеже приведена функциональная схема устройства.

Вычитающее устройство содержит входы 1, инверторы 2, схему И 3 анализа единиц, схему И 4 анализа нулей, схему равнозначности 5, схему ИЛИ 6, триггер 7 зацрета анализа нулей, триггер 8 запрета анализа единиц, схему ИЛИ 9, схему И 10 задержки, вход 11 тактового импульса, триггер 12, схему И 13 занесения дополнения, группу, состоящую «з Л схем И 14-1 - 14-N, формирующую разности по несовпадению, группу схем И 15-1-15-Л, формирующую разности по равенству, входы тактовых импульсов 16-1 - 6(Я+1), группы схем ИЛИ 17-1-17-jV, выходы устройства 18-1-18().

Устройство работает следующим образом.

В исходном состоянии триггеры 7, 8 установлены в нулевое состояние, на их нулевых выходах присутствует высокий потенциал, тем самым схемы И 3, 4 по запрещающему входу открыты. Триггер 12 также установлен в нулевое состояние, на его единичном выходе сигнал отсутствует и поэтому все схемы И 14, 15 закрыты.

Числа А и В поступают на входы 1 последовательно старшими разрядами вперед. В случае равенства сравниваемых разрядов сигнал с выхода схемы равнозначности 5 через закрытые схемы И 15 не проходит на выходы 18-2-18-Л. При появлении первого несовпадения в разрядах чисел сигнал с выхода схемы И 3 либо схемы И 4, которые вместе с инверторами 2 реализуют функции AjBj и AjBj соответственно, поступит на единичный вход триггера 7 либо триггера 8 и установит его в единичное состояние. Тем самым схема И 4 либо схема И 3 закроется по запрещающему )Входу. Кроме того, сигнал с единичного выхода триггера 7 либо триггера 8 через схему ИЛИ 9 и схему И 10 по совпадению с тактовым импульсом, поступающим по входу 11, поступит на единичный вход триггера 12, который установится в единичное состояние и откроет по соответствующему входу схемы И 14 и 15. Тактовый импульс по входу 11 в каждом цикле обработки одной пары разрядов чисел подается с отставанием от тактовых импульсов, поступающих по входам 16-1 - 16-jV. Этим исключается формирование ложного разряда разности при первом несовпадении.

Допустим, что после первого несовпадения незапрещенной осталась схема И 3, т. е. на триггере 7 сохраняется несовпадение Л 1, 5fe О, где k - номер несовпавшего разряда.

Если в дальнейшем в i-ых разрядах чисел окажется несовпадение типа А , 5 0, то сигнал с выхода схемы И 3 через схему ИЛИ 6 и открытую тактовым импульсом по входу

16-г схему И I4-t, а также через схему ИЛИ 17-f-1 поступит на выход 18-f-1. Если в i-ый разрядах чисел будет несовпадение типа j 0, 5,, то ни на одном из выходов 18-1 - 18-Л

сигнала не будет, так как схема И 4 закрыта. При равенстве г-ых разрядов чисел сигнал с выхода схемы равнозначности 5 через схему И 15-1 и схему ИЛИ 17-i поступит на выход I8-i. Если в триггерах запрета 7 или 8 хранится первое несовпадение, то после окончания анализа последних разрядов чисел в (ггН-1)-м цикле через схему И 13 и схему ИЛИ 17-yV по совпадению с тактовым импульсом по входу на выход поступит единица младшего разряда разности. Таким образом, на выходах устройства 18-1 - - 18-Л +1 в каждом цикле обработки разрядов чисел будет присутствовать код в виде всех нулей либо в виде всех нулей и единицы

в одном из разрядов. Эти коды представляют собой приращения к разности и должны суммироваться с ранее накопленными разностями на каком-либо суммирующем устройстве, например двоичном счетчике.

Предмет изобретения

Вычитающее устройство, содержащее схемы

И, ИЛИ, инверторы и триггеры, отличающееся тем, что, с целью сокращения объема оборудования и расширения функциональных возможностей, лервый вход устройства подключен к первому входу первой схемы И и к

первому входу схемы равнозначности, а через инвертор - к первому входу второй схемы И и ко второму входу схемы равнозначности другой вход устройства соединен со вторыу входом второй схемы И и с третьим входом

схемы равнозначности, а через инвертор - со вторым входом первой схемы И и с четвертым входом схемы равнозначности, выход первой схемы И подключен к одному из входов первой схемы ИЛИ и к единичному входу первого триггера, нулевой выход которого подключен к третьему входу второй схемы И, выход которой соединен с другим входом первой схемы ИЛИ и с единичным входом второго триггера, нулевой выход которого подключен к

третьему входу первой схемы И, выход первой схемы ИЛИ соединен с первыми входами каждой из N схем И первой группы, выход схемы равнознач.ности подключен к первым входам каждой из Л схем И второй груипы, единичные выходы первого и второго триггеров через вторую схему ИЛИ подключены к первому входу третьей схемы И, второй вход которой соединен с третьим входом устройства, выход третьей схемы И

соединен с единичным вхйдом третьего триггера, единичный выход которого подключен ко вторым входам каждой из V схем И первой и второй групп и к первому входу четвертой схемы И, третьи входы каждой из N схем И

первой и второй групп соединены соответственно с N управляющими шинами устройства, второй вход четвертой схемы И соединен с (ЛГ4-1)-ой управляющей щиной, выход первой схемы И первой группы соединен с первым выходом устройства, а выходы остальных схем И первой группы соединены соответственно с первыми входами (N-1) схем ИЛИ, вторые входы которых соединены с выходами соответствующих схем И второй группы, а входы N-ой схемы ИЛИ соединены с выходом Л-ой схемы И второй группы и выходом четвертой схемы И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля схем сравнения | 1985 |

|

SU1297057A1 |

| Устройство для поиска чисел в заданном диапазоне | 1981 |

|

SU993250A1 |

| Устройство для определения разностидВуХ п-РАзРядНыХ чиСЕл | 1979 |

|

SU824208A1 |

| Устройство для сравнения -разрядных двоичных чисел | 1977 |

|

SU746502A1 |

| Устройство для сравнения двоичных чисел | 1989 |

|

SU1633390A1 |

| Устройство для распознавания образов | 1988 |

|

SU1575211A1 |

| Многоканальный цифровой коррелятор кодовых символов | 1977 |

|

SU691867A1 |

| Устройство для сравнения двоичных чисел | 1979 |

|

SU964629A1 |

| Устройство для моделирования сетевых графов | 1981 |

|

SU1013965A1 |

| Устройство для сложения и вычитания чисел в фазо-импульсной форме | 1976 |

|

SU595732A1 |

Авторы

Даты

1973-01-01—Публикация