1

Устройство относится к области автоматики и выч1 слительной техники н мо:кет быть использовано при реализации технических средств цифровой автоматики и цифровых электроизмср1Гсльных нриберов.

Р1звесткы устройства, выполняющие операции сложения и вычитания.

Известное устройство для определения разности двух чисел, содержащее счетчик уменьшаемого, счетчик вычитаемого, счетчик абсолютной разности, триггер знака, схему сравнения, генератор импульсов и элементы И, выполняет операцию вычнтаНИЯ двух Л разрядных чисел путем добавления единичных имнульсов в счетчик, содержащий меньщее из двух чисел, до момента их равенства. Однако это устройство не выполняет операции сложения, кроме того, имеет ограниченное быстродействие, повыщение которого возможно лишь применением более высокочастотных счетчиков. Применение двух счетчиков, используемых для вычисления, также является недостатком этого устройства 1.

Известное устройство для слолсения выполняет операцию сложения цифр, представленных десятичным фазо-импульсным кодом, и содержит преобразователь фазы цифры в число импульсов, матрицу сло кения, пороговую и логическую схемы, два регистра и счетчик. Однако это устройство не осуществляет операции вычитания и не может быть использовано для сложения jV-разрядных чисел 2.

Из известных устройств наиболее близким по технической сущности к изобретению является устройство для сложения и вычитания чисел в фазо-имиульсной форме, содержащее два элемента ЗИ-ИЛИ, блок сравнения разрядов, накапливающий счетчик, блок переключения разрядов, блок преобразования фазы цифры .в число импульсов, триггер запуска, элемены И и ИЛИ, причем выходы элементов ЗИ-ИЛИ соединены соответственно с первым и вторым информационными входами блока сравнения разрядов, выход первого

элемента ЗИ-ИЛИ подключен также к первым входам первого и второго элементов И, к вторым входам которых подключены соответственно шина разрешения сложения и щина разрешения вычитания. Выход первого

элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с запускающим входом блока преобразования фазы цифры в число импульсов, выход второго элемента И соединеи с первым входом второго элемента ИЛИ, выход которого соединеи со стоповым входом блока преобразования фазы цифры в число импульсов, тактовый вход которого подключен к первому тактовому входу устройства, управляющие входы -

к выходам блока переключения разрядов, а

информационные выходы - к соответствующим входам накапливающего счетчика. Другие выходы блока переключения разрядов соединены с входами элементов ЗИ-ИЛИ, другие входы которых нодключеив соотзстствеино к входам разрядов вычитаемого и к зходам разрядов умеиьшаемого. Тактовый вход блока переключения разрядов подключен к выходу третьего элемента И, нервый вход которого подключен к второму тактовому входу устройства, устаповочные входв блока переключения разрядов подключены к щ1П1ам разрещепня сложения и вычитаиня. Шина разрсщеиия вв1читання подключена также к управляющему входу блока сравнения разрядов, вход запуска устройства подключеп к едпиичиому входу триггера запуска, нулевой вход которого подключеп к выходу блока иереключеппя разрядов, а вв1ход---к второлау входу третьего элемента И 3.

Однако это устройство ироизводнт операции сложения и вычитания лишь с одним деСЯТИЧНЫЛ1 разрядом, а для оиераций с Л-разряднымн чиелами требуетея его Л-кратпое повторение, что существенно уеложняет и удорожает устройство.

Цель изобретения - унрощеине устройства для сложения и вычитания Л-разрядных десятичных чисел, нредставленных в фазо-нмпульспой форме.

Это достигается тем, что в иредлагаемое устройство введены блок уиравлегп-ш фазой умепьщаемого п четвертый элемепт И, первый вход которого подключеп к выходу блока сравиення разрядов, второй - к третьему тактовому входу устройства, третий - к третьему входу третьего элемеита И и к инвереному контрольному выходу блока нреобразовання фазы цифры в число пмнульеов, а выход - к первому входу блока управления фазой уменьшаемого, второй вход которого соединен с входом сброса блока сравнепия разрядов, вторым входом второго элемента и выходом третьего элемеита И, третий вход блока уиравлення фазой умепьщаемого еоединен с прямым контрольным выходом блока преобразования фазы цифры в чиело имиульсов, четвертый вход - с вторым тактовым входом устройства, пятый вход - с выходом второго элемента ЗИ-ИЛИ, а выходы подключены к второму и третьему входам нервого элемента ИЛИ.

Кроме того, блок управления фазой уменьшаемого содержит два триггера, три элемента И и элемент задержки, нрнчем первый вход блока подключен к единичному входу нервого триггера, единичный и нулевой выходы которого соединены с первымн входами соответственно первого н вторОго элементОВ И, вторые входы которых соединены е пятым входом блока, а третьи входы - с нулевым выходом второго триггера, нулевой вход которого подключен к второму входу блока, а единичный - к выходу третьего элемента И, входы которого иодключены к третьему и четвертому входам блока. Выход нервого элемента И через элемент задержки подключен к нулевому входу первого триггера. Выходы второго э.темеита И и элемента задержки являютея ;ь ходами блока.

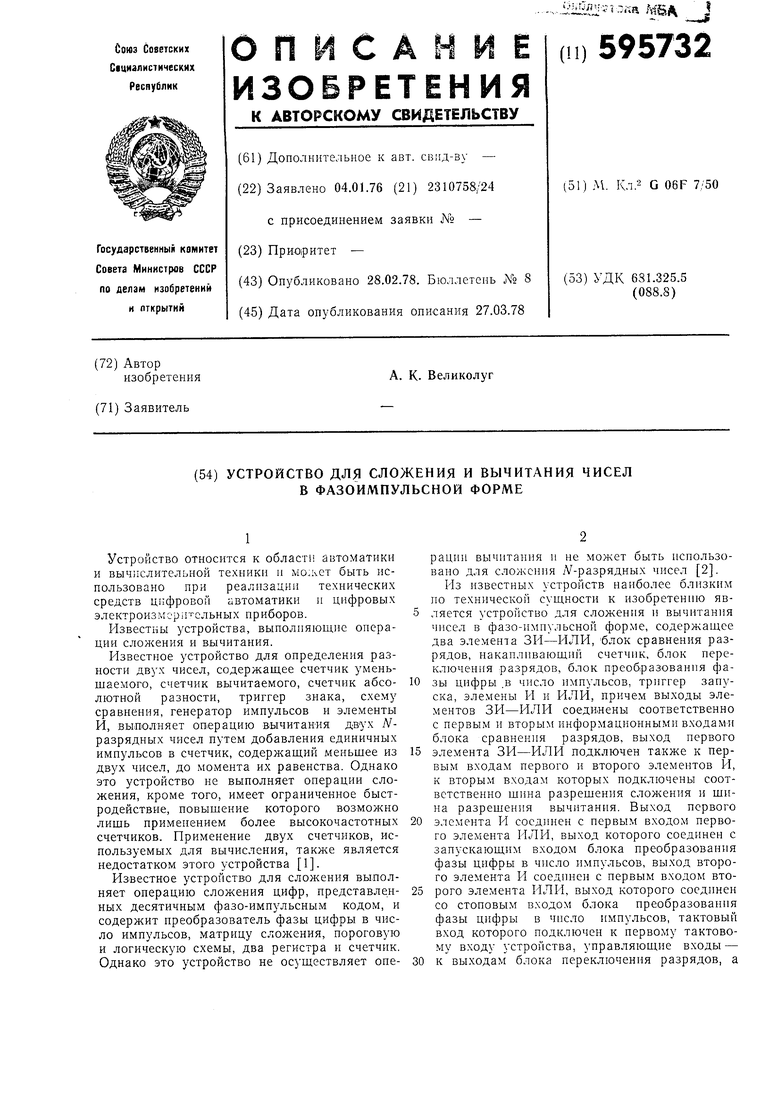

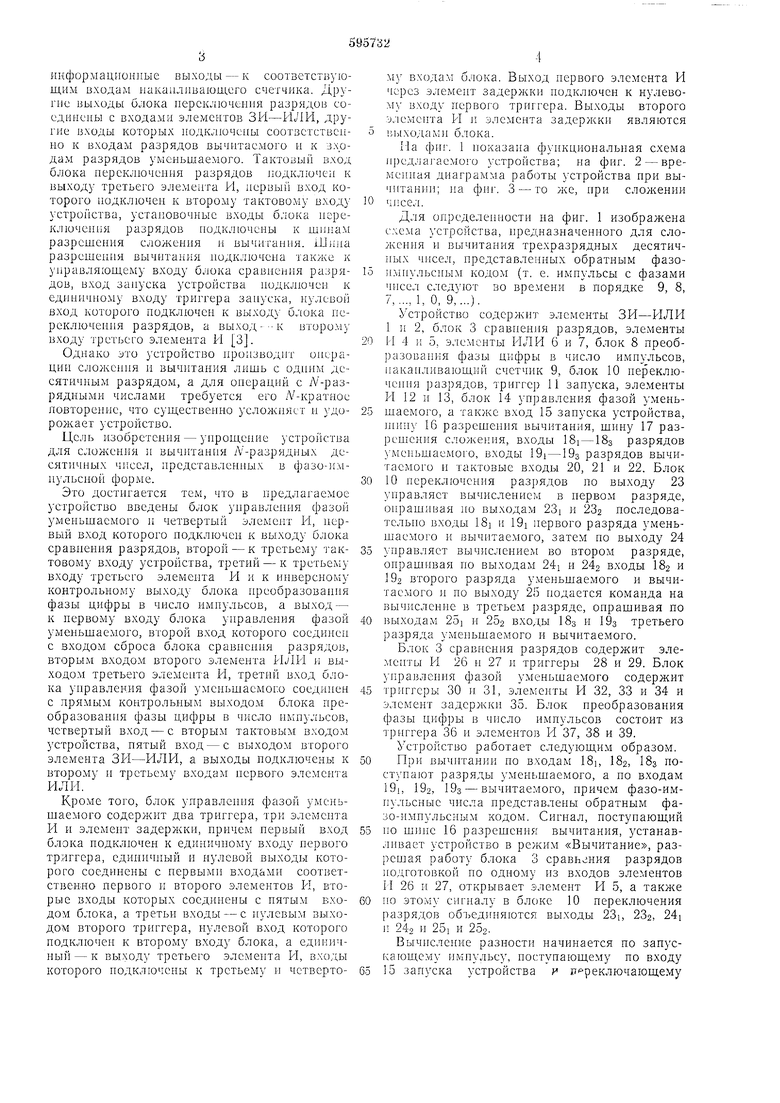

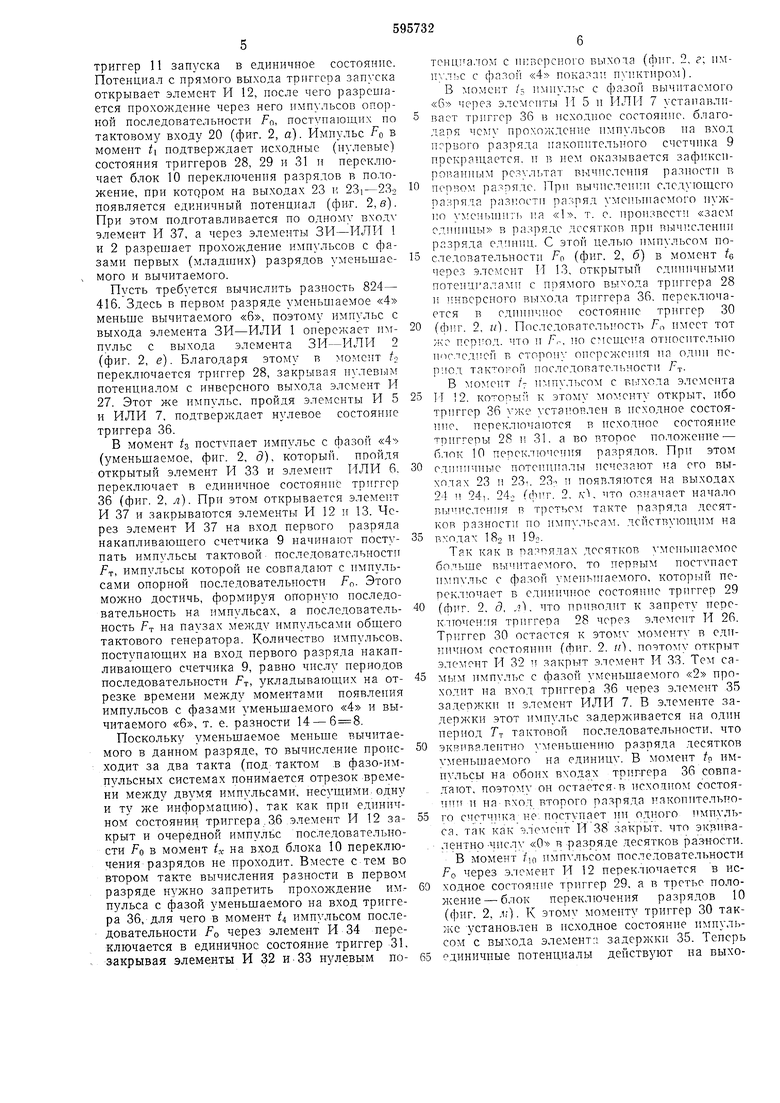

Ма фиг. 1 показапа фупкциональная схема п)едлагаемого устройства; на фиг. 2 - времеииая диаграмма работы устройства при вычитании; иа фиг. 3 - то же, ири сложении чисел.

Для онределеииости на фиг. 1 изображена схема }стройства, нредназначенного для сложення н вычитания трехразрядных десятичных чисел, иредставлепных обратным фазоимнульсным кодом (т. е. импульсы с фазами чпсел следуют во времени в порядке 9, 8, 7,..., 1, О, 9,...).

Устройство содержит элементы ЗИ-ИЛИ 1 и 2, блок 3 сравнения разрядов, элементы 1-1 4 и 5, элемситы ИЛИ 6 и 7, блок 8 преобразоваиия фазы цифры в число имиульсов, иакаиливающий счетчик 9, блок 10 иереключеиня разрядов, тригге) И запуска, элементы PI 12 и 13, блок 14 управления фазой уменьшаемого, а также вход 15 запуска устройства, игнпу 16 разрешения вычитания, щину 17 разрешения сложения, входы 18i - 18з разрядов уменьшаемого, входы 19i-19з разрядов вычитаемого п тактовые входы 20, 21 и 22. Блок 10 переключения разрядов по выходу 23 уиравляет вычнелением в первом разряде, опрашивая ио выходам 23i и 232 последовательио входы 18i и 19i первого разряда уменьшаемого и вычитаемого, затем но выходу 24 управляет вычиелепием во втором разряде, опрашивая ио выходам 24, и 242 входы 182 и 192 второго разряда уменьшаемого и вычитаемого и ио выходу 25 подается команда на вычисление в третьем разряде, оирашнвая по выходам 25 и 252 входы 18з и 19з третьего разряда уменьшаемого и вычитаемого.

Блок 3 еравнения разрядов содержит элементы И 26 п 27 н триггеры 28 и 29. Блок уиравлепня фазой уменьшаемого содержит триггеры 30 и 31, элементы И 32, 33 и 34 и элемепт задержкп 35. Блок преобразования фазы цифры в число импульсов состоит из триггера 36 и элементов И 37, 38 и 39.

Устройство работает еледующим образом.

Ири вычитании по входам 18i, 182, 18з поступают разряды уменьшаемого, а по входам 19ь 192, 19з - вычитаемого, причем фазо-имиульеные чпела предетавлены обратным фазо-импульсным кодом. Сигнал, поступающий ио Ш1и;е 16 разрешенпя вычитания, устанавливает устройство в режим «Вычитание, разрешая работу блока 3 сравнения разрядов подготовкой по одиому из входов элементов И 26 п 27, открывает элемент И 5, а также по этому сигналу в блоке 10 переключения разрядов объединяютея выходы 23i, 232, 24i и 242 и 25i н 252.

Вычиеление разности начинается по запускающему пмнульсу, ноступающему по входу 15 запуска устройства и гт -реключающему

триггер 11 запуска в единичное состояние. Потенциал с прямого выхода триггера запуска открывает элемент И 12, после чего paspeniaется прохождение через него импульсов опорной последовательиости fo, поступающих по тактовому входу 20 (фиг. 2, а). Импульс F в момент t подтверждает исходные (нулевые) состояния триггеров 28, 29 и 31 и переключает блок 10 переключения разрядов в положение, при котором на выходах 23 и 23i-232 появляется единичный потенциал (фиг. 2, в). При этом подготавливается по одному элемент И 37, а через элементы ЗИ-ИЛИ 1 и 2 разрешает прохождение импульсов с фазами первых (младших) разрядов уменьшаемого и вычитаемого.

Пусть требуется вычислить разность 824- 416. Здесь в первом разряде уменьшаемое «4 меньше вычитаемого «6, поэтому импульс с выхода элемента ЗИ-ИЛИ 1 опережает импульс с выхода элемента ЗИ-ИЛИ 2 (фиг. 2, е). Благодаря этому в момент /г переключается триггер 28, закрывая пулевыл потенциалом с инверсного выхода элемент И 27. Этот же импульс, пройдя элементы И 5 и ИЛИ 7, подтверждает нулевое состояние триггера 36.

В момент tz иостунает импульс с фазой «4- (уменьшаемое, фиг. 2, д), который, пройдя открытый элемент И 33 и элемент ИЛИ 6. переключает в единичное состояние триггер 36 (фиг. 2, л. При этом открывается элемент И 37 и закрываются элементы И 12 и 13. Через элемент И 37 на вход первого разряда накапливаюшего счетчика 9 начинают поступать импульсы тактовой последовательности .FT, импульсы которой не совпадают с импульсами опорной носледовательностн FC,. Этого можно достичь, формируя опорную иоследовательность на импульсах, а последовательность FT на паузах между импульсами обшего тактового генератора. Количество импульсов, поступающих иа вход первого разряда накапливающего счетчика 9, равно чнслу периодов последовательности FT, укладывающих на отрезке времени между моментами появления импульсов с фазами уменьшаемого «4 и вычитаемого «6, т. е. разности 14 - .

Поскольку уменьшаемое меньше вычитаемого в даииом разряде, то вычисление происходит за два такта (под тактом в фазо-импульсных системах понимается отрезок времени двумя импульсами, несущими, одну и ту же информацию), так как при единичном состояния триггера .36 элемент И 12 закрыт и очередной импульс последовательиости FO в момент tx на вход блока 10 переключения разрядов не проходит. Вместе с тем во втором такте вычисления разности в первом разряде нужно запретить прохождение импульса с фазой уменьшаемого на вход триггера 36, для чего в момент t импульсом последовательности FO через элемент И 34 переключается в единичное состояние триггер 31. закрывая элементы И 32 и-33 нулевым потенциалом с ni:BepcHoro выхота (фпг. 2, ; ИМПУЛЬС с фазой «4 показпп пупктпром)В MOMei-гг /5 импульс с фазой вычитаемого «6 через элемотггы И 5 п 1-1ЛИ 7 устаиавли5 васт триггер 36 в исходное состояние, благолапя чему прохождение имиульсов на вход первого разряда накопительного счетчика 9 ирекраи1,ается. п в )1ем оказывается зафиксированным результат вычислення разности в

0 первом разряде. При вычислении следующего разряда разряд уменьшаемого нужно , иа «1. т. е. произвести «заем единицы в разряде десятков прп Шзршслеиип разряда едги-п Ц. С этой целью импульсом ио5 следовательности FO (фиг. 2, б) в момент fo через элемент И 13, открытый единичными потепшалами с прямого вывода триггера 28 п инверсного выхода триггера 36. переключается в едипичпое состояние триггер 30

0 (Аиг. 2, и. Последовательность FO имеет тот ко период, что и Г,-, но смещена опгосителыю тюслсдпей в сторои-; опсреженпя па один период такто1оГ| последовательности FT.

В момент /7 импульсом с вьтхола элемента

5 И 12. котопый к этому моменту открыт, ибо триггер 36 уже установлен в исходное соетояипе, переключаются в неходкое состояние триггеры 28 1 31. а во второе положеиие - блок 10 переключения разрядов. При этом

0 одипичпые потептитпльт исчезают на его выхолах 23 и 23.. 23;i и появляются на выходах 24 24;. 24; (фиг. 2. я , что означает начало пт тчислоиия в тpeтьe t такте разряда десятков разности по импульсам, дсйствуюпим на

5 входах 18, и 192.

Так как в пазпядах десятков уменьшаемое больше вычитаемого, то первым постлиает илтульс с фазой )мепьп1аемого, который переключает в едпнпчпое состояние триггер 29

0 (сЬиг. 2. д, .), что приводит к заирету переключеиия триггера 28 через элемент И 26. Триггер 30 остается к ЭТОМУ моменту в едттиичиом состояиии (фиг. 2. //), поэтол у открыт элемент И 32 ly закрыт элемент И 33. Тем самым ИМПУЛЬС с фазой уменьшаемого «2 проходит иа вход триггера 36 через элемент 35 задержки и элемент ИЛИ 7. В элементе задержки этот импульс задерживается на один период T тактовой последовательности, что

0 эквивалеитно уменьшению разряда десятков yмeньцIae foгo на единицу. В момент ta имиульсьт иа обоих входах триггера 36 совпадают, поэтому он остается, в исходном состоятитт и на-вход второго разряда иакопптельпо5 го счетч11ка ь:е. поступает пи одного пмп.ульса. так как элемент И 38 закрьтт. что эквивалентно-числл «О в разряд,е десятков разности. В момент /10 имплльсом последовательности FO через элемент И 12 иереключается в исходное состояние триггер 29, а в третье положение- блок переключения разрядов 10 (фиг. 2, .1;). К этому моменту триггер 30 также установлен в исходное состояние импульсом с выхода элемент;; задержки 35. Теперь

5 единичные потенциалы действуют на выходах 25 и 25ь 252, благодаря чему подготавливается по одному входу элемент И 39 и разрешается прохождение разрядов сотен уменьшаемого и вычитаемого через элементы ЗИ- ИЛИ 1 и 2 по входам 18з и 19з, т. е. с момента /10 начинается вычисление разряда сотен разности.

В моменг tn импульсом с фазой уменьшаемого «8 через элемент И 33 и ИЛИ 6 переключается в единичное состояние триггер 36, а в момент /i2 он устанавливается в исходное .состояние импульсом е фазой вычитаемого. За время нахождения триггера 36 в единичном состоянии на вход третьего разряда иаконительного счетчика 9 через элемент И 39 иостунает количество импульеов, равное разности 8 - 4 4. В момент ii схема устройства устанавливается в исходное состояние, при этом в блоке 10 переключения разрядов формируется импульс, поступающий па вход установкп к нуль триггера 11 .,В резvльтaтe в накопительны счетчик 9 оказывается добавленной разность 824 - 416 408.

Величина задержки т, KOTOpyjo претерпевает н.мпульс, проходящий через элемент задержки 35, не является жесткой и может меняться в иределах ,57т.

При сложеини па шине 17 разрещеиия елол ения должен действо5ать единичный потенциал, а на щине 16 разрешения вычитания - нулевой. При этом в операции сложения не учаетвует блок 3 сравнения, а блок 14 у.ряг,ления фазой уменьщасмого пропускает нмпульсы е фазами одного из слагаемых, не изменяя их временного положения, ПОСКОЛЬКУ элемент И 13 постоянно закрыт н левым потенциалом с выхода триггера 28. Зто делает невозможным срабатывание триггера 30, а триггер 36 иереключается в нулевое соетояние веегда в моменты .а,ейетвия импульса последовательности Ff,, который подтверждает исходное состояние триггера 31. поэтому на выходе элемента И 34 импульс появиться не может, т. е. триггер 31 также постоянно находится в исходном (нулевом) состоянии. Кроме того, по сигналу по шине 17 разрешения сложения, блок 10 переключения разрядов устанавливается в , при котором длительности импульсов на выходах 23, 24 и 25 составляют два такта, а нл выходах 23ь 232; 24|, 240; 25, 252 - один такт.

Эпюры, поясняюшие работу устройства в режиме сложения, приведены на фиг. 3. Сигналы, представляющие собой фазы слагаемых, поступают по входам 18i, 182 и 18з и 19ь 192 и 19з.

После запуска устройства импульс последовательности FO в момент / через элемент И 12 устанавливает блок переключения разрядов в первое положение, при котором на выходе 23 появляется сигнал, иоказачньй ьт фиг. 3, б, а на выходе 23i - изгнал, фиг. 3. е.

Пусть требуется вычислить сумму 2894-346. В течение первого такта разрешается ппохождение сигналов первого (младшего) разряда первого слагаемого через элемент ЗИ- ИЛИ 2. В момент iz (фиг. 3, д} импульс с фазой первого слагаемого «9 через элемент И 33 и ИЛИ 6 переклгочает в единичное состояние триггер 36 (фиг. 3,е). После этого через элемент И 37 на вход первого разряда накапливающего счетчика 9 начинают поступать импульсы последовательности FT (фиг. 3,м). В момент /3 триггер 36 устанавливается ИМПУЛЬСОМ последовательности FQ через элемент ИЛИ 7 в нулевое состояние, одновременно переключается во второе положение блок 10 переключения разрядов. За отрезок /з-4 на первый вход накапливающего счетчика 9 проходит девять нмпул)Сов. Сигнал с выхода 232 (фиг. 3,г) разрешает теперь прохождение через элемент ЗИ-ИЛИ 1 имиульса с фазой первого разряда второго слагаемого «6, котопый Переключает в момент t. (фиг. 3, е) через элемеиты И 4 и ИЛИ 6 триггер 36 вновь в (u I и 1 i ч н О со с т о я н и е.

Во втором такте импульсы последовательности РГ также проходят на вход первого разряда иакапливлюпгего счетчика 9, суммируясь с ранее постхпивЩИми импульса ти первого слагаемого. Если суммарное количество импульсов, на вход одного и того же разряда накапливаюшего ечетчика. 9 больше десяти, то в нем Еэзникает импульс пере1юса, поступающий на вход счетчика более старгигго гязрядр. В момент is триггеп 36 ппзвпячтаетгя р иллевое состояние, блок 10 тгереключения пазрядов устанавливается в третье состояние, на выходе 24 появляется сигнал, показанный на Лиг. 3. ж. на выходе 24i-сигнал, показанный на фиг. 3. я и начинается вычисло1гие суммы чисел во ВТОРЫХ пазоялях сляг.яемых. В дальн йите.т работа прптекярт янялогично описанной.

Таким образом, суммироватие Л -разрядных чисел происходит всегла зп отр.зо времени, равный 2N тактов. Вычисление же разности Л-разря тных чисел осуществляется максимум за 2.V-1 такт, минимум за Л тактов.

Предложенное устройство наиболее эффективно использовать в системах, в которых числа представлены в обратном фазо-импульспом коде. Оно итожет быть применено также при прямом фазо-импульспом коде и при двоичном коде, если ввести дополнительно на информационных входах преобразователь кодов.

Формула изобретения

1. Устройство для сложения и вычитания чисел в фазоимпульсной форме, содержащее два элемента ЗИ-ИЛИ, блок сравнения разрядов, накапливаюший счетчик, блок переключ и я р-зрядов, блок преобразования фазы цифры в число импульсов, триггер запуска, элеАТенты И и ИЛИ, причем выходы элементов ЗИ-ИЛИ соединены соответственно с первым и вторым информационными входами блока сравнения разрядов, выход первого элемента ЗИ-ИЛИ подключен к первым входам первого и второго элементов И, к вторым входам которых подключены соответственно шина разрешения сложения и ииша разрешения вычитания, выход первого элемента И соединен с первым входом первого элемента ИЛИ, выход которого соединен с запускаюпдим входом блока преобразования фазы цифры в число импульсов, выход второго элемента И соединен с первым входом второго элемента ИЛИ, выход которого соединен со стоповым входом блока преобразования фазы цифры в число импульсов, тактовый вход которого подключен к перпо у тактовому входу устройства, управляюш,ие входы - к выходам блока переключения разрядов, а информационные выходы - к соответств}юш,им входам накапливающего счетчика, другие выходы блока переключения разрядов соединены с входами элементов ЗИ-ИЛИ, другие входы которых подключены соответственно к входам разрядов вычитаемого и к входам разрядов умеиьшаемого, тактовый вход блока переключения разрядов подключен к ВЫХОДУ третьего элемента И, первый вход которого подключен к второму тактовому входу устройства, установочные входы блока переключения разрядов иодключены к шиням разрешения сложения и вычитания, шипа разрешения вычитания подключена также к управляюшему входу блока сравнения разрядов, вход запуска устройства подключен к единичному входу триггера запуска, нулевой вход которого подключен к выходу блока переключения разрядов, а выход - к второму входу третьего элемента И, о т л i-; ч а ю щ е е с я тем, что, с целью упрошения устройства, в него введены блок управления фазой уменьшаемого и четвертый элемент И, первый вход которого подключен к выходу блока сравнения разрядов, второй - к третьему тактовому входу устройства, третий-к третьему входу третьего элемеита И и к инверсному контрольному выходу блока преобразования фазы цифры в число импульсов, а выход - к цервому входу блока управления фазой уменьшаемого, втопой вход которого соединен с входом сброса блока сравнения разрядов, вторым входом второго элемента ИЛИ и выходом третьего элемента И, третий вход блока управления фазой уменьшаемого соединен с прямым контрольным выходом блока преобразования фазы цифры в число импульсов, четвертый вход - с вторым тактовым входом устройства, пятый вход - с выходом второго элемента ЗИ-ИЛИ, а выходы подключены к второму и

третьему входам первого элемента ИЛИ.

2,Устройство по п. 1, отличаю ш,ееся тем, что блок управления фазой уменьшаемого содержит два триггера, три элемента И и элемент задержки, причем первый вход блока подключен к единичному входу первого триггера, единичный и нулевой выходы которого соедииены с первыми входами соответст г :но первого и второго элементов И, вторые входы которых соединены с пятым входом блока, а третьи входы - с нулевым выходом второго триггера, нулевой вход которого подключен к второму входу блока, а еднинчный - к выходу третьего элемента И, входы которого подключены к третьему и четвертому входам блока, выход первого элемента И через элемент задержки подключен к нулевому входу первого триггера, выходы второго элемента И и элемента задержки являются выходами блока.

РТсточники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР №341031, кл. G 06F 7/02, 1970.

2. Авторское свидетельство СССР №370606, кл. G 06F 7/385, 1970.

3.Авторское свидетельство СССР №365704, кл. G 06F 7/50, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения и деленияпОСлЕдОВАТЕльНО-пАРАллЕльНОгОдЕйСТВия | 1979 |

|

SU817703A1 |

| Вычитающее устройство | 1979 |

|

SU771668A1 |

| Генератор радиоимпульсов со случайной начальной фазой | 1977 |

|

SU684726A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕСЯТИЧНЫЙ СУММАТОР | 1965 |

|

SU169891A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Реверсивный двоично-десятичный счетчик | 1974 |

|

SU525251A1 |

| Устройство для вычисления разности двух чисел | 1980 |

|

SU879585A1 |

Авторы

Даты

1978-02-28—Публикация

1976-01-04—Подача