(54) МНОГОКАНАЛЬНЫЙ ЦИФРОВОЙ КОРРЕЛЯТОР КОДОВЫХ СИМВОЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1975 |

|

SU590752A1 |

| Многоканальный цифровой коррелятор | 1981 |

|

SU1019459A1 |

| Многоканальный цифровой коррелятор | 1976 |

|

SU634287A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Способ передачи и приема дискретных сообщений в комплексе декаметровой радиосвязи | 2020 |

|

RU2743233C1 |

| Комплекс декаметровой радиосвязи | 2020 |

|

RU2737763C1 |

| УСТРОЙСТВО АДАПТИВНОГО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2001 |

|

RU2194366C2 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1997 |

|

RU2116004C1 |

| Устройство для обслуживания запросов | 1988 |

|

SU1571588A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1292006A1 |

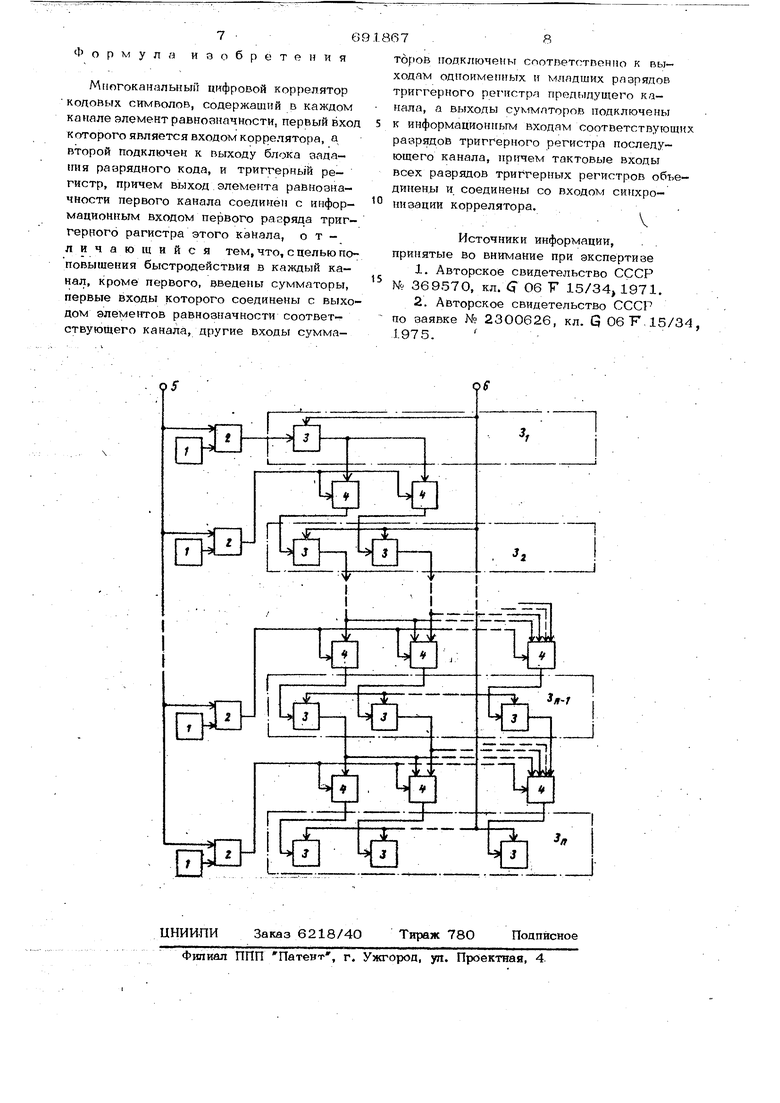

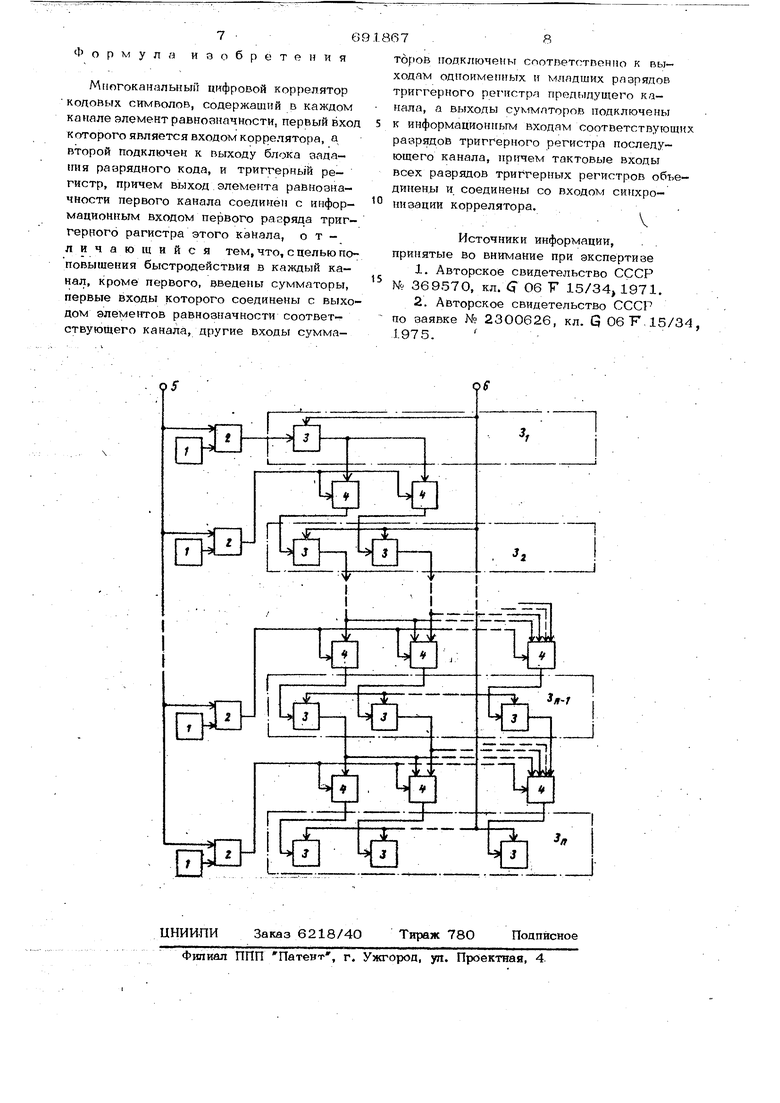

Изобретение относится к области циф ровых систем .передачи и автоматической обработки данных. Предполагаемое изобретение может быть использовано, в частности, при разработке цифровых теле метрических систем или цифровых систем связи с использованием для синхройиза- ции кодов большой длины. Известно устройство, позволяющее получать значения автокорреляционной функции в выполненное на дискретных элементах. Это устройство содержит блоки задания разрядного кода, триггерный регичтр разрадные схемы совпадения и несовпадения с линиями задержки, счетчики числа совпадений или несовпадений разрядов принимаемой кодовой комбинации с заданной 1 . Такие корреляторы обладают ни ЁЖИМ быстродействием, обусловленным наличием линий задержки или необходимостью выполнять за один такт принимаемой КОДОВОЙ комбинации некоторое число операций. . Известен также цифровой коррелятор, в котором формирование значения корреляционной функции осуществляется последовательно за п тактов принимаемой кодовой комбинации. По своей технической сущности д1анный коррелятор является наиболее близким к изобретению. Он содержит в каждом канале элемент равнозначности, первый вход которого является входом коррелятор, а второй подключен к выходу блока задания разрядного кода, и триггерный регистр, причем выход элемента равнозначности первого канала соединен с информационным входом первого разряда триггерного регистра, 2 Недостаткам прототипа является необходимость выполнения элементами устройства двух операций за один такт принимаемой кодовой комбинации, а нмевно, добавление очередного результата сравнения к числу, накопленному в соответствующем счетчике и сдвига чисел из одного счетчика в другой. Это требует ot элементов устройства двойного быстродействия по отношению к тактовой частоте принимаемого сигнала. В настоящее время известны системы передачи данных со скоростями до нескольких десятков и даже сотен Мбт/сек. При этом длительность кодовых элементов составляет десятки или . единицы н.с. В этих условиях от элементов коррелятора требуется чреявычайно высокое быстродействие. Целью предлагаемого изобретения является повышение быстродействия коррелятора. Поставленная цель достигается тем, что в цифровой коррелятор введейы сумматоры, первые входы которых соединен|л с выходом элементов равнозначности соответствующего канала, другие входы сумматоров Подключены соЬтвётЬТЪеино к выходам одноименных и младших разрядов тригге змого регистра предыдущего канала, а выходы - к информационным входам соответствующих разрядов триггерного регистра последующего канала, причём тактовые взводы всех разрядо1в триггерных регистров объединены и соединены со входом синхронизации коррелятора. На чертеже представлена блок-схема многоканального цифрового коррелятора кодовых символов. Цифровой коррелятор содержит, блоки 1 задания значений разрядного кода, элементы 2 равнозначности (эквивалент . кости), триггерные регистры Э,З.-.-Ьп, с триггерами 3, числЬ которых равно числу кодовых элементов в заданной ком бинации, а также сзмматоры 4. Блок 1 задания значений paepsafHord кода соединен с первым входом элемент 2 равнозначности, второй вход которого соединен с входной шиной 5 текущей ко довой последовательности, а выход подключён к первым входам всех суглйаторов 4 для данного канала. Последующие входьт сумматоров устройств соединены с одноименными и всеми младшими разрядами триггеного регистр(а предыдущего канала. Выходы сушлаторов соеди нены с информационными входами соотв ствующих триггеров 3 данного триггерного регистра, а тактовые входы триггеров 3 соединены с шиной 6 тактовой частоты - входом синхронизации коррё- jiiSTOpa.. 67-4 С .целью сокращения оборудования риггерные регистры имеют неодинаков вое число разрядов, которое зависит от номератриггерного регистра К и равно целой части выражения K + i . Таким образом, первый триггерный регистр имеет один разряд, второй -- два разряда, третий - тоже два, четвертьй, пятый, шестой и седьмой - по три разряда и т.д. Коррелятор работает следующим обраПри появлении на шине 5 очередного кодового символа, его значение сравнивается со значением всех кодовых символов заданной кодовой последовательности, поступающими на элементы 2 равнозначности с соответствующих блоков 1 задания разрядного кода. При совпадений значений текущего кодового символа с каким либо из заданных, а именно оба символа нули или оба символа единицы, с выхода соответствующих элементов 2 равнозначности на входы соответствующих сумматоров 4 поступает единичный потенциал. При этоти в первом канале, триггерный регистр 1 которого состоит из одного триггера 3, результат сравнения с элемента 2 равнозначности поступает непосредственно на информационный вход этого триггера. В остальных каналах каждый из сумматоров 4 в зависимости от числа, записанного в триггерном регистре предыдущего канала в предществующем такте, с учетом добавления к этому числу результата сравнения символов для данного канала на элементе 2 равнозначности определяет новое состояние соответствующего разряда триггерногр регистра. При поступлении очередного импульса тактовой частоть производится установка в это состояние триггера соответствующего, разрйда триггерного регистра данного канала. Эта операция производится одновременно для всех каналов. Выполнение указанной операции в каждом такте приводит к образованию в триггерном регистре последнего п -го канала текущего значения корреляционной функции. При поступлении на шину 5 последнего символа заданной кодовой комбинации в этом триггерном регистре будет накоплено максимальное число п , соответствующее пиковому значению корреляционной .функции,позволяющее точно определить момент поступления заданной кодовой комбинации. 56 Процесс образования значения корреляционной функции осушествляется сле дующим образом. . При поступлении первого символа заданной кодовой комбинации по шине 5 на элементе 2 равнозначности первого кана ла возникает единичный потенциал и при поступлении тактового импульса по шине б в триггер первого канала запишется единица. При поступлении второго кодового символа заданной комбинации единичный результат сравнения будет образован на элементе 2 равнозначности вто рого канала, который вместе с единицей первого канала поступит на входы соотI ветствующих логических Сумматоров. Вторым тактовым импульсом выходные значения этих сумматд ов будут поданы на триггерный регистр второго каиала, в котором запишется число 2. Очевидно, при поступлении т|эетьего. символа заданной кодовой комбинации в третьем- канале будет записано число три т.д., пока не появится последний символ кодовой комбинации, когда в f -м триггёрном регистре запишется число П , соответст вующее числу разрядов в заданной кодовой комбинации, В другие моменты вре. мени последний тркггермый регистр будет накапливать числа, меньшие п , соответствующие числу совпадений с п символа ми кодовой комбинации, поступившими до данного момента времени, с заданной. Сумматор 4 предназначеный для определения нового значения разрвда триг герного регистра при добавлении к npisдыдущему числу результата сравнения кодовых символов, должен работать следующим образом. Единичное значение на его выходе дол но образовываться: -когда результат сравнения равен нулю, а одноименный разряд предыдущего триггерного регистра находится е единичном состоянии; -когда результат сравнения равен единице, одновременный разряд предыдущего триггерного регистра находится в нулевом состоянии, а триггеры младших разрядов этого регистра находятся в единичном состоянии; - когда результат сравнения равен единице, одноименной разряд предыдущего триггерного регистра находится в еди- ничном состоянии, а среди триггеров младших разрядов этого регистра имегется хотя бы один, находящийся в нулевом состоянии. 67 Нулевое значение сумматора 4 должно образовываться во всех остальных случаях, а именно: -при нулевом результате сравнения и когда., одноименньй разряд предыдущего триггерного регистра находится в нулевом состойнии; -при единичном результате сравнения и когда одноименный разряд и все младшие разряды предыдущего триггерного регистра находятся в единичном состоянии;-при единичном результате сравнения и когда одноименный разряд предыдущего триггерного регистра находи1х;я в нулевом состоянии, а среди мл |дших разрядов этого регистра имеются разряды, находящиеся в нулевом состоянии. Обозначив результат сравнения 6 К -м канале логической переменной а состояние разрядов триггерного регистра предыдущего канала как Вк - 1, Вк -1, В, - 1 ...., где верхний индекс обозначает номер разряда, можно записать логическое выражение для значения переменной на выходе сумматора m-;ГО разряда или значения, соответствующего триггера в к-м канале: .С,С..Ч.,,.) Таким образом, логический сумматор весьма просто мoжet быть реализован с помощью логических схем И, ИЛИ, и НЕ. Введение новых элементов - логических суммирующих устройств позволяет повысить быстродействие предлагаемого цифрового коррелятора в два раза по отношению к указанному прототипу в связи с тем, что операций суммирования эквивалентна двум операциям, (сложение и сдвиг числа) прототипа. Это, в свою очередь, позволяет построить цифровой коррелятор ДЛИ передач ОС скоростью порядка 10О Мбоц на серийно выпускаемых интегральных микросхемах типа 100 серии, что невозможно осуществить с применением схемы прототипа. Кроме того, введение логических сумматоров рактически не увеличиЬает объем оборуования по отношению к прототипу, так ак в предлагаемом корреляторе исчеает необходимость- в блокировочных хемах между разрядами триггерных рёг;нстров. 7 6 Формула изобретения МпогоканальиыГ цифровой коррелятор кодовых символов, содержащий в каждом канале элемент равнозначности, первый вхо которого является входом коррелятора, а второй подключен к выходу блока задания разрядного кода, и триггерньш регистр, причем выход элемента равнозначности первого канала соединен с информационным входом первого раяряда триггерного регистра этого канала, отличающийся тем, что, с целью поповышения быстродействия в каждый каиал, кроме первого, введены сумматоры, первые входы которого соединены с выхо дом элементов равнозначности соответствующего канала, другие входы сумма05

Qf 67 торов подключены спответстпонпо к выходам одноименных т младших разрядов триггерного регистра предыдущего канала, а выходы сумматоров подключены к информацион гым входам соответствующих разрядов триггерного регистра последующего канала, причем тактовые входы всех разрядов триГгерных регистров объединены и соединены со входом синхронизации коррелятора. Источники информации, . . принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 369570, кл, 06 F 15/34,1971. 2.Авторское свидетельство СССР по заявке № 2300626, кл. G 06 F. 15/34, .1975.

Авторы

Даты

1979-10-15—Публикация

1977-07-05—Подача