1

Изобретение относится к области импульсной техники и может использоваться для синхронизации цифровых устройств и для контроля аппаратуры.

Известно устройство для синхронизации импульсов, содержащее триггер, подсоединенный одним входом к источнику входных импульсов, а другим через каскад задержки к выходу устройства, и комбинационную логическую схему, включенную между выходом триггера и выходом устройства.

Однако при работе таких устройств на выходе устройства появляются паразитные выборы с частотой следования синхронизирующих импульсов.

Целью изобретения является повыщение надежности устройства.

Это достигается тем, что в предлагаемом устройстве комбинационная логическая схема выполнена в виде синхронизированного триггера, состоящего из последовательно соединенных двухвходовой схемы совпадения и триггера со счетным входом. Выход схемы совпадения, подсоединенной одним из входов к источнику синхронизирующих импульсов, подключен к счетному входу триггера.

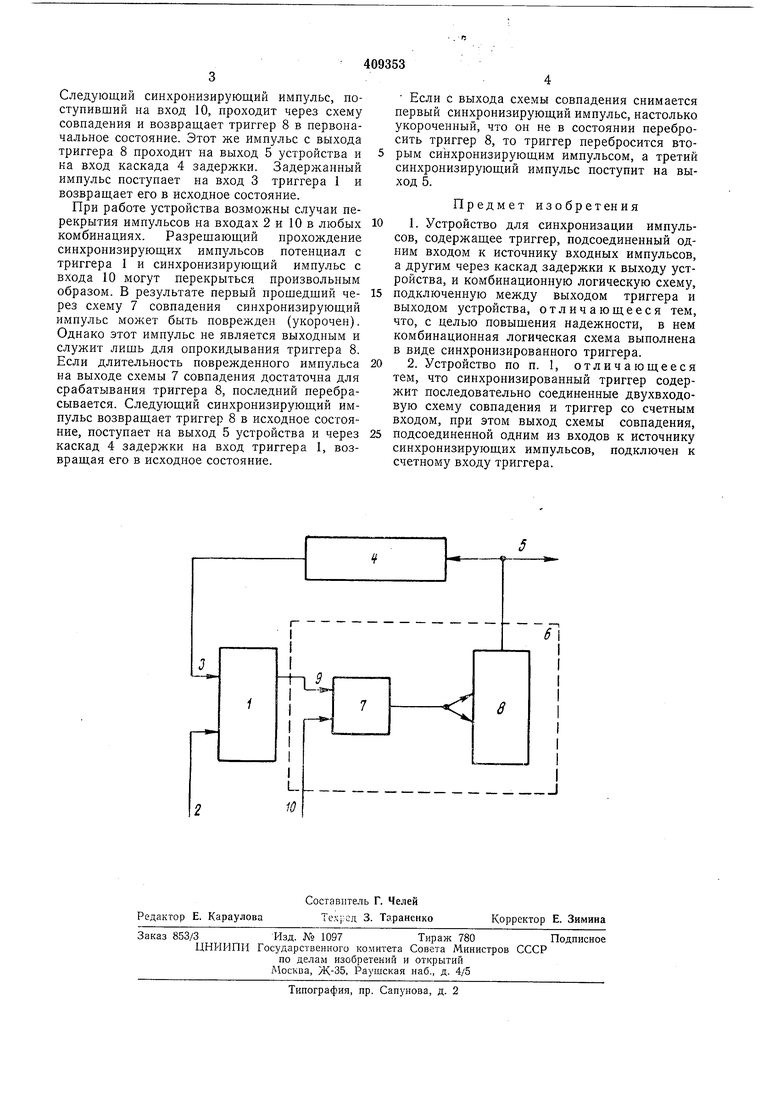

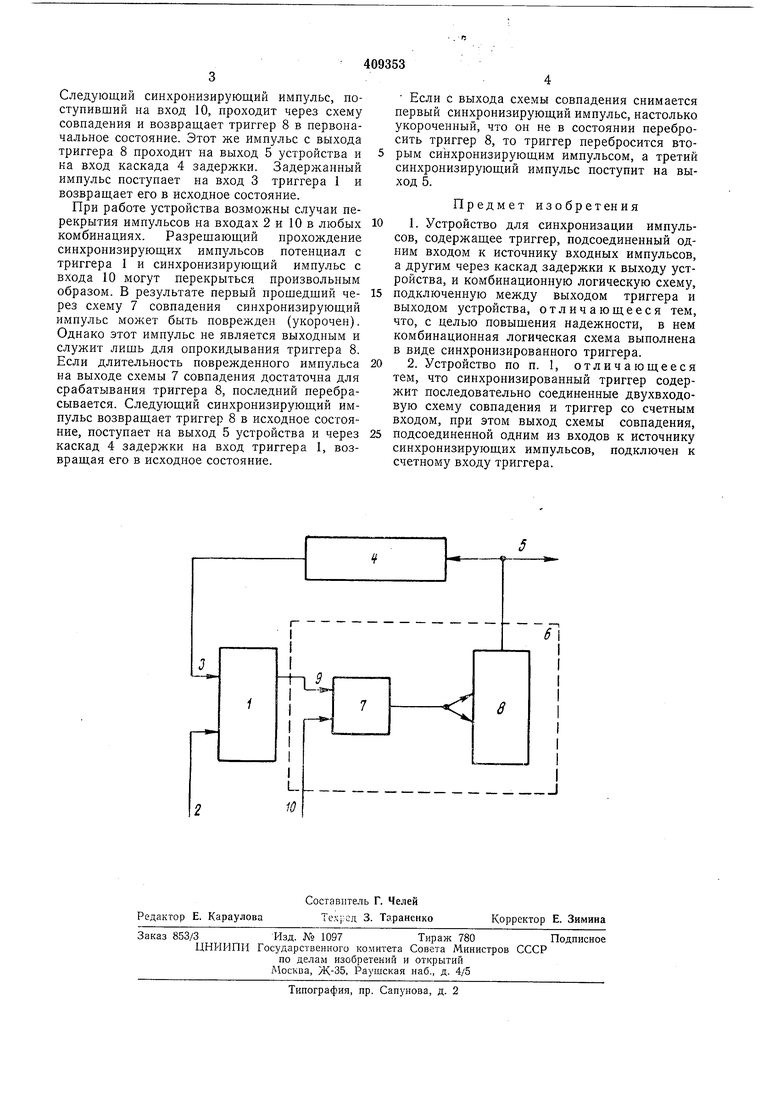

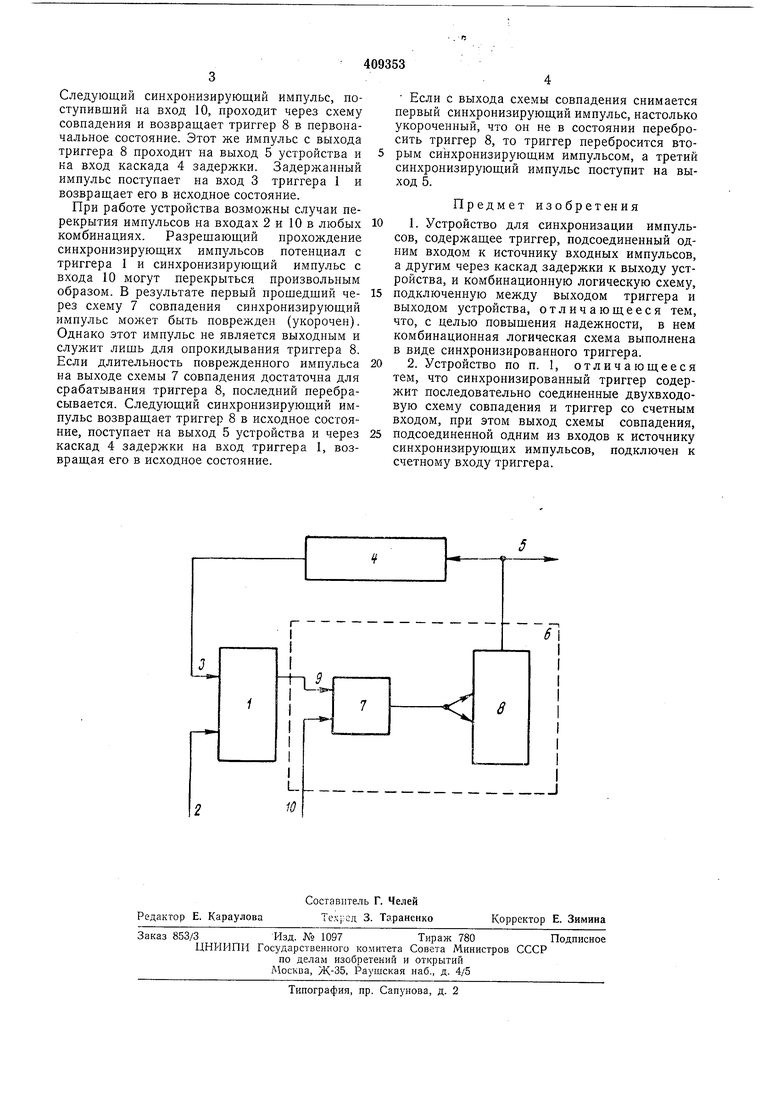

На чертеже приведена блок-схема предлагаемого устройства для синхронизации импульсов.

Оно содержит триггер 1, подсоединенный

входом 2 к источнику входных импульсов, а входом 3 через каскад 4 задержки к выходу 5 устройства, и комбинационную логическую схему 6, выполненную в виде синхронизированного триггера, состоящего из последовательно соединенных двухвходовой схемы 7 совпадения и триггера 8 со счетным входом. Комбинационная логическая схема 6 включена между выходом 9 триггера 1 и выходом 5

устройства. Выход схемы совпадения, подсоединенной входом 10 к источнику синхронизирующих импульсов, подключен к счетному входу триггера 8. Устройство работает следующим образом.

В исходном состоянии триггер 1 находится в состоянии «О, на выходе 9 триггера также нулевой потенциал, который поступает на вход схемы 7 совпадения. Независимо от потенциала на входе 10 схемы совпадения на ее выходе

поддерживается нулевой потенциал. Триггер 8 со счетным входом находится в исходном состоянии, и на выходе 5 устройства сигнал отсутствует.

При поступлении на вход 2 триггера 1 входного импульса последний опрокидывается, и «1 с выхода 9 триггера поступает на вход схемы 7 совпадения. Поступивщий вслед за этим на вход 10 импульс синхронизации проходит через схему совпадения, поступает на

счетный вход триггера 8 и опрокидывает его.

Следующий синхронизирующий импульс, поступивший на вход 10, проходит через схему совпадения и возвращает триггер 8 в первоначальное состояние. Этот же импульс с выхода триггера 8 проходит на выход 5 устройства и на вход каскада 4 задержки. Задержанный импульс поступает на вход 3 триггера 1 и возвращает его в исходное состояние.

При работе устройства возможны случаи перекрытия импульсов па входах 2 и 10 в любых комбинациях. Разрешающий прохождение синхронизирующих импульсов потенциал с триггера 1 и синхронизирующий импульс с входа 10 могут перекрыться произвольным образом. В результате первый прошедший через схему 7 совпадения синхронизирующий импульс может быть поврежден (укорочен). Однако этот импульс не является выходным и служит лишь для опрокидывания триггера 8. Если длительность поврежденного импульса на выходе схемы 7 совпадения достаточна для срабатывания триггера 8, последний перебрасывается. Следующий синхронизирующий импульс возвращает триггер 8 в исходное состояние, поступает на выход 5 устройства и через каскад 4 задержки на вход триггера 1, возвращая его в исходное состояние.

Если с выхода схемы совпадения снимается первый синхронизирующий импульс, настолько укороченный, что он не в состоянии перебросить триггер 8, то триггер перебросится вторым синхронизирующим импульсом, а третий синхронизирующий импульс поступит на выход 5.

Предмет изобретения

1. Устройство для синхронизации импульсов, содержащее триггер, подсоединенный одним входом к источнику входных импульсов, а другим через каскад задержки к выходу устройства, и комбинационную логическую схему,

подключенную между выходом триггера и выходом устройства, отличающееся тем, что, с целью повышения надежности, в нем комбинационная логическая схема выполнена в виде синхронизированного триггера.

2. Устройство по п. 1, отличающееся тем, что синхронизированный триггер содержит последовательно соединенные двухвходовую схему совпадения и триггер со счетным входом, при этом выход схемы совпадения,

подсоединенной одним из входов к источнику синхронизирующих импульсов, подключен к счетному входу триггера.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации импульсов | 1977 |

|

SU790225A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1972 |

|

SU355723A1 |

| Одноканальное устройство для управления вентильным преобразователем | 1978 |

|

SU714618A1 |

| Устройство для синхронизации импульсов | 1979 |

|

SU809532A2 |

| ДИСКРЕТНЫЙ ФАЗОВРАЩАТЕЛЬ | 1970 |

|

SU270064A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯХАРАКТЕРИСТИКИ ГРУППОВОГО ВРЕМЕНИЗАПАЗДЫВАНИЯ | 1972 |

|

SU428309A1 |

| Устройство для синхронизации импульсов | 1981 |

|

SU961125A1 |

| Устройство для синхронизации импульсов | 1973 |

|

SU488320A2 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1970 |

|

SU267687A1 |

| Генератор функций уолша | 1974 |

|

SU503355A1 |

8

L10

.I

Авторы

Даты

1973-01-01—Публикация