1

Изобретение относится к импульсной технике. Устройство может использоваться для контроля аппаратуры, для синхронизации цифровых устройств, в которых предъявляются жесткие требования к выработке одиночного выходного импульса независимо от длительности входного.

По основному авт. св. 409353 известно устройство для синхрОНизации импульсов, содержащее триггер, линию задержки и комбинационную логическую схему в виде последовательно соединенных двухвходовой схемы совпадения и триггера со счетны.м входом. Однако это устройство недостаточно надежно в работе.

В целях повышения надежности в работе в предлагаемом устройстве между нулевым выходОМ и единичным входом триггера включены последовательно соединенные дополнительный триггер и инвертор, а между единичным выходом триггера и входом комбинационной логической схемы включена схема И второй вход которой соединен с -входом miвертора.

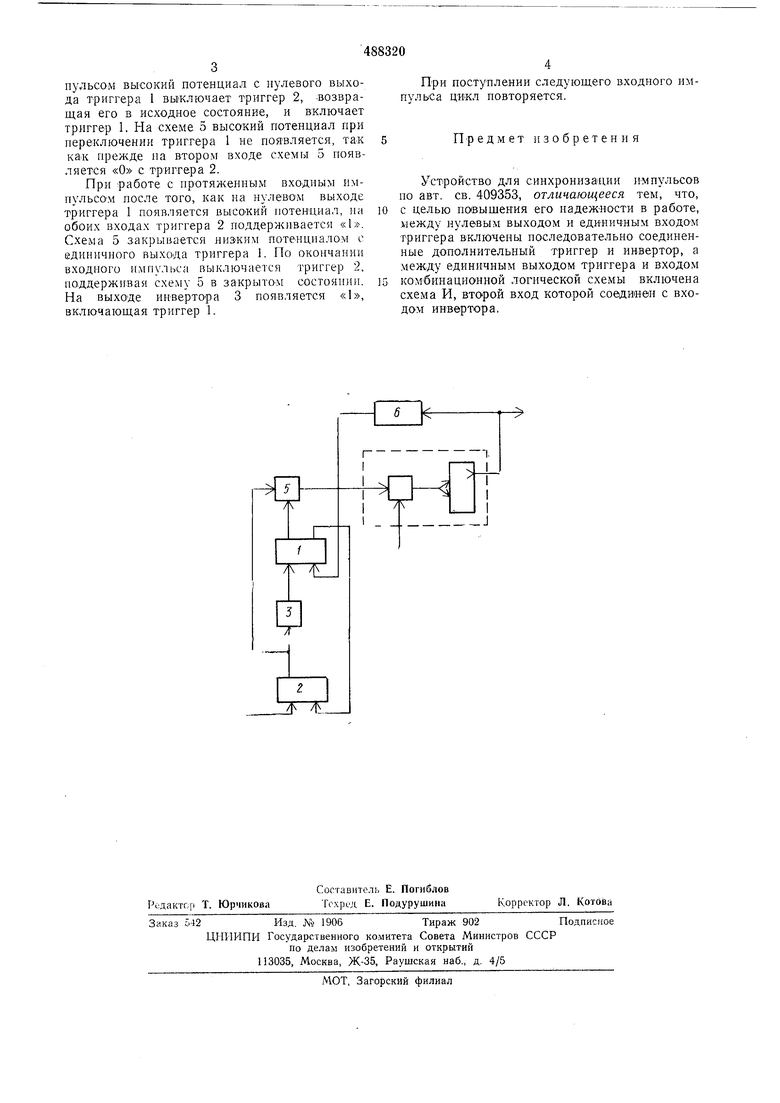

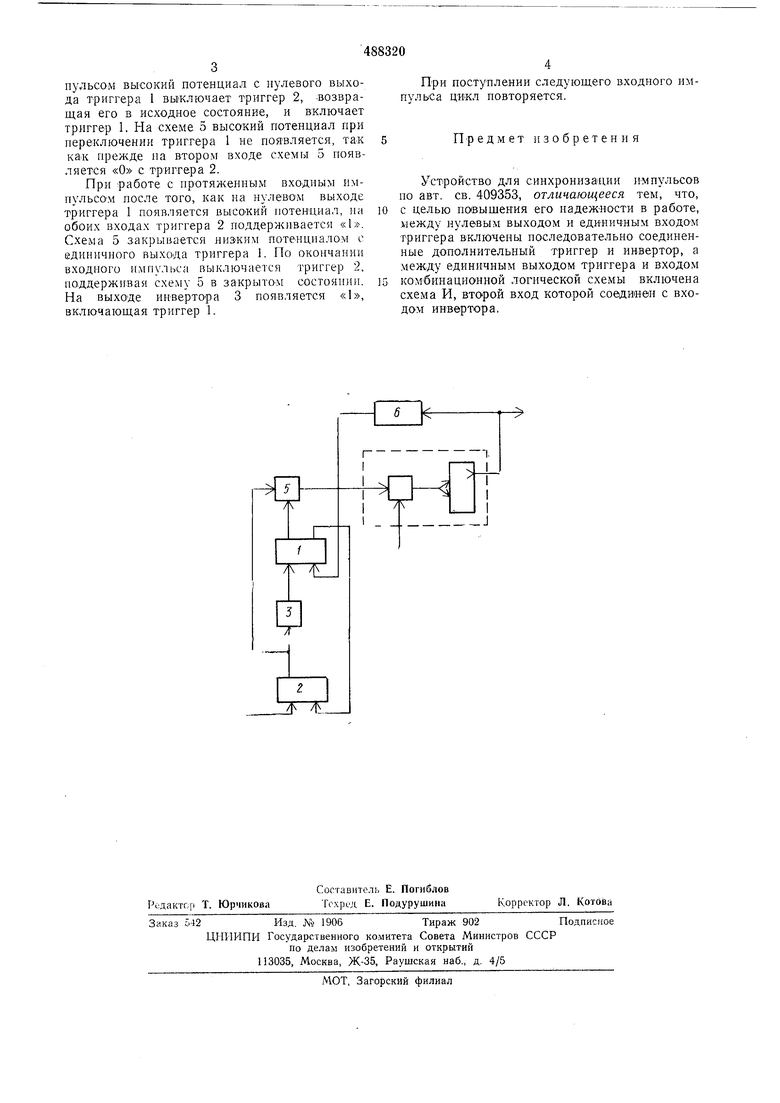

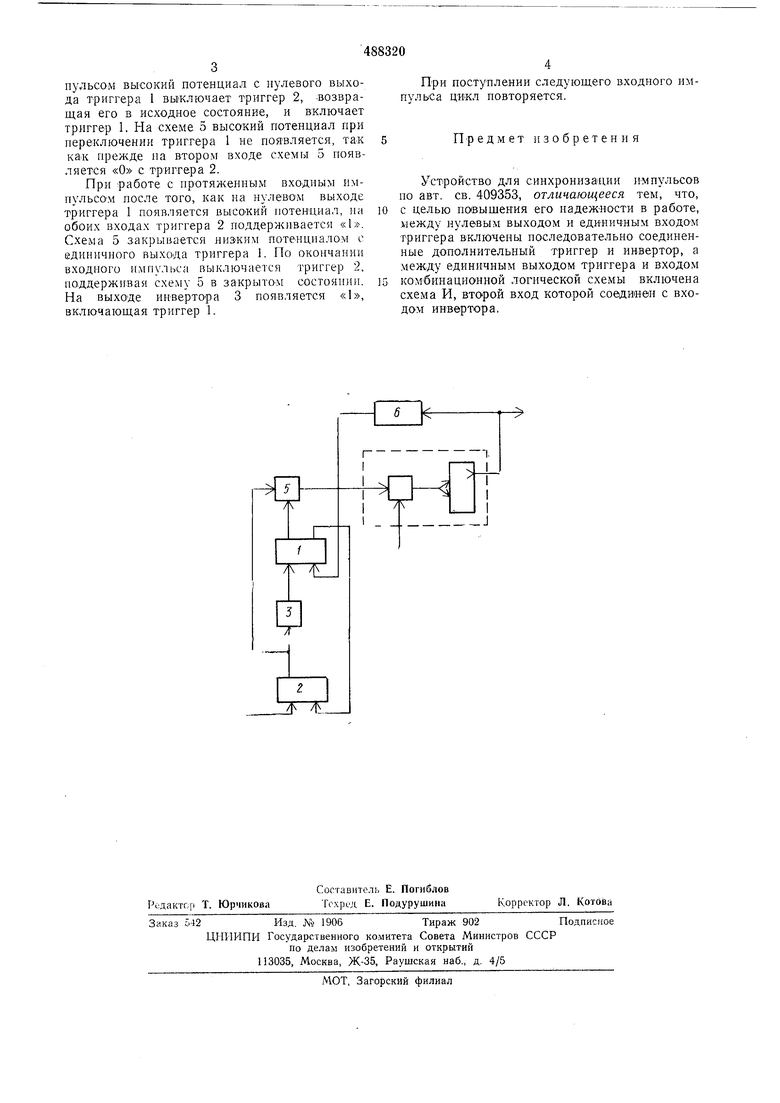

На чертеже приведена блок-схема устройства для синхронизации имнульсов.

Устройство содержит триггер 1, между нулевым выходом и единичным 1входом которого включены последовательно соединенные доиолнительный триггер 2 и инвертор 3. Между

единичным выходом триггера I и входом комбинационной логической схемы 4 включена схема II 5, второй вход которой соединен с входом инвертора. Нулевой вход триггера 1

соединен с линией задержки 6.

Устройство работает следующим образом.

В исходном состоянии триггер 2 включен,

так что на его единичном выходе имеется

низкий потенциал, который поступает на схему И 5 и в противофазе на единичный вход триггера 1, поддерживая на его единичном выходе высокий потенциал. Низкий потенциал с выхода схемы 5 запрещает прохождение импульсов синхронизации на вход комбннационной логической схемы 4.

Поступивший на вход устройства входной импульс включает триггер 2. Высокий потенциал с его выхода открывает схему 5, меняет фазу на выходе инвертора 3, освобождая

тем самым единичный вход триггера 1. Высокий нотенциа, со схемы 5 поступает на комбинационную логическую схему 4, на выходе которой вырабатывается импульс переноса. Он проходит на выход устройства и через лииию задержки 6 на нулевой вход триггера 1, на нулевом выходе которого появляется высокий потенциал, при этом на его еднннчном выходе наблюдается низкий потенциал, закрывающий схему 5.

В случае работы с коротким входным импульсом высокий потенциал с нулевого выхода триггера 1 выключает триггер 2, возвращая его в исходное состояние, и включает триггер 1. На схеме 5 высокий потенциал при переключении триггера 1 не появляется, так каК прежде па втором входе схемы 5 появляется «О с триггера 2.

При работе с протяженным входным импульсОМ после того, как на нулевом выходе триггера 1 появляется высокий потенциал, на обоих входах триггера 2 поддерживается «1. Схема 5 закрывается низким потенциалом о единичного выхода триггера 1. По окончании входного импульса выключается триггер 2, поддерживая схему 5 в закрыто м состоянии. Па выходе инвертора 3 появляется «1, включающая триггер 1.

При поступлении следующего входного импульса цикл повторяется.

Предмет изобретения

Устройство для синхронизации импульсов по авт. св. 409353, отличающееся тем, что, с целью по1вышения его надежности в работе, между нулевым выходом и единичным входом триггера включены последовательно соединенные дополнительный триггер и инвертор, а между единичным выходом триггера и входом ком бинационной логической схемы включена схема И, второй вход которой соединен с входом инвертора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство допускового контроля временных интервалов | 1978 |

|

SU669330A2 |

| Устройство формирования одиночного импульса | 1973 |

|

SU443468A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1973 |

|

SU409353A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для синхронизации случайных импульсов | 1975 |

|

SU544957A1 |

| Устройство для синхронизации импульсов | 1984 |

|

SU1228245A2 |

| Измеритель серии временных интервалов | 1980 |

|

SU898382A2 |

| Устройство тактовой синхронизации | 1978 |

|

SU764112A1 |

| Устройство тактовой синхронизации | 1978 |

|

SU748839A1 |

Авторы

Даты

1975-10-15—Публикация

1973-07-02—Подача