1

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразования угла поворота или величины перемещения в двоичный код, когда входная информапия представлена в виде сдвига фазы напряжения, а выходная информапия должна быть представлена в виде двух последовательностей импульсов.

Одним из основных требований, которому должен удовлетворять преобразователь фаза- последовательность импульсов ввиду невосполнимости потерь информации, является такое структурное построение, которое обеспечивает отсутствие лишних импульсов или потерю импульсов, несущих информацию, при случайных сбоях и помехах.

Одним из наиболее эффективных способов повышения помехозащищенности является построение схемы устройства в виде импульсной следящей системы, в которой выходной импульс является одновременно импульсом обратной связи.

В известном преобразователе фаза - последовательность импульсов, содержащем импульсный датчик, фазовый датчик, схему «ИЛИ, кольцевой делитель, схему «Запрет, формирователь выходных импульсов и схему задержки, импульсы с двух соседних элементов кольцевого делителя, равные по длительности периоду заполняющей частоты, поступают на схему «Запрет, причем предыдущий импульс записывает, а последующий - считывает информацию. Если импульс, сформированный от переднего фронта сигнала фазового

датчика, приходит во времени между импульсами кольцевого делителя, то выдачи сигнала на выходе схемы «Запрет нет.

Когда изменение фазы сигнала фазового датчика достигнет величины принятой

дискретности, импульс, сформированный по его переднему фронту, выйдет за пределы временного интервала, образованного импульсами делителя, и на выходе схемы «Запрет при очередном заполнении появится импульс.

Этот импульс проходит на выход устройства и одновременно через схему «ИЛИ в делитель, где, суммируясь с импульсами импульсного датчика, смещает импульсы упомянутых элементов кольцевого делителя на один период

частоты импульсного датчика, так, что импульс фазового датчика вновь окажется между ними.

Однако в известном устройстве, во-первых, обратная связь с выхода устройства на вход

кольцевого делителя через схему «ИЛИ обусловливает возможность сдвига импульсов кольцевого делителя только в одну сторону. Это, в свою очередь, дает возможность импульсам делителя следить за импульсом

фазового датчика с рассогласованием, эквивалентным выбранной днскретности, только при приращениях фазы одного знака. Приращение фазы противоположного знака даже при его величине, равной дискретности, вызовет появление на выходе устройства начки импульсов, причем число импульсов в пачке будет лишь на единицу меньше числа полностью заполняющих кольцевой делитель периодов частоты импульсного датчика. Указанное делает невозможным применение известного преобразователя непрерывного изменения фазы в системах управления, где возможны приращения фазы обоих знаков.

Кроме того, во-вторых, на выходе известного устройства и его цепи обратной связи импульсы появляются всякий раз, как только импульс фазового датчика оказывается вне временного промежутка между импульсами кольцевого делителя. Сбой же любого элемента кольцевого делителя неизбежно приводит к смещению его импульсов так, что импульс фазового датчика окажется вне промежутка между ними и на выходе появятся лищние импульсы. Иными словами, устройство для преобразования непрерывного сдвига фазы имеет низкую помехозащищенность по отнощению к случайным сбоям.

В третьих, импульсы кольцевого делителя отслеживают перемещение импульса фазового датчика на величину только одного периода заполняющей частоты импульсного датчика за период сигнала с выхода фазового датчика. Это означает, что сбой кольцевого делителя, вызвавший смещение его импульсов во времени на несколько периодов, обусловливает потерю устройством работоспособности в течение Л - п периодов напряжения фазового датчика: .(здесь Л - число периодов напряжения импульсного датчика, полностью заполняющих кольцевой делитель; п - число периодов напр51жения импульсного датчика, на которое произошло смещение импульсов кольцевого делителя).

В-четвертых, отсутствие блокировки цепи обратной связи и выхода устройства в момент совпадения имиульса фазового датчика с одним из импульсов кольцевого делителя является препятствием к использованию устройства для преобразования непрерывного изменения фазы и в системах с односторонним приращением фазы при малых скоростях ее изменения, так как даже в отсутствие приращения фазы на практике неизбежно явление дрожания фазового импульса вследствие помех и нестабильности работы формирователя фазового имиульса. Это дрожание в точках, кратных величине выбранной дискретности, эквивалентно двустороннему приращению фазы и приводит к сбоям, т. е. к потере информации.

Цель изобретения - повыщение помехоустойчивости и надежности работы устройства при восстановлении после случайного сбоя в течение одного периода питающего фазовый датчик напряжения и повыщение помехозащищенности устройства по отношению к случайным сбоям его логических элементов, а также повышение его помехозащищенности по отношению к электростатическим и электромагнитным помехам, вызывающим дрожание фазового импульса во времени.

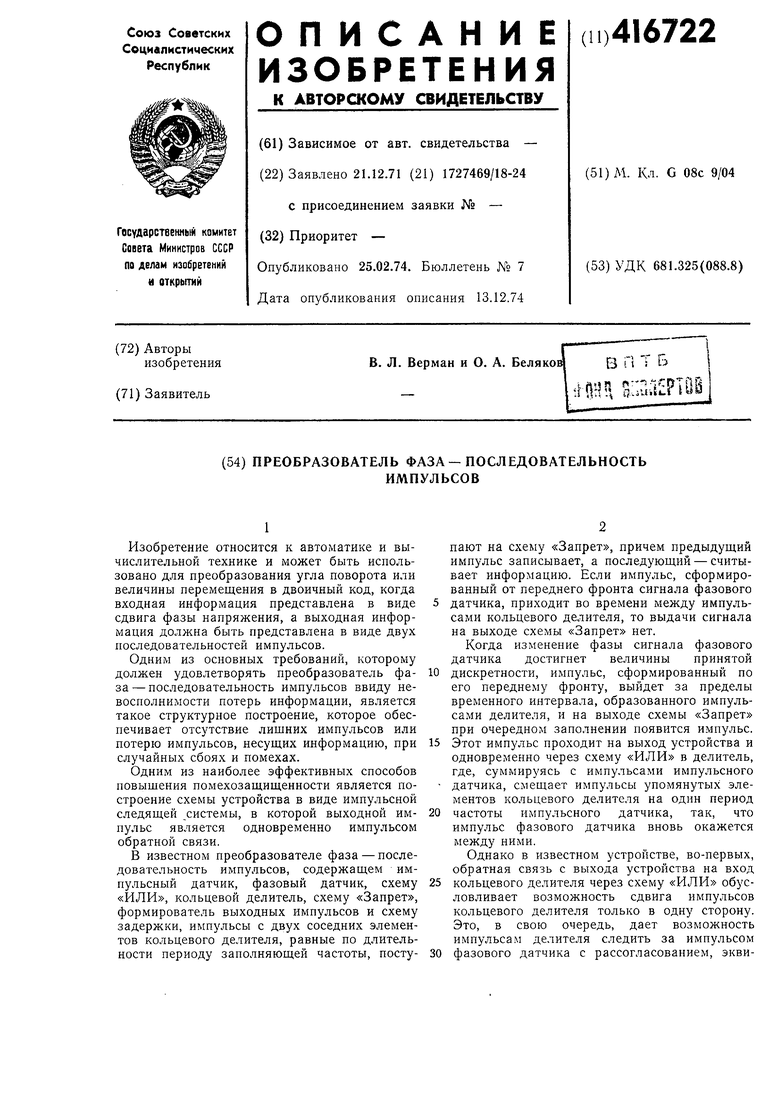

Это достигается тем, что в известное устройство введены следящий счетчик, синхронизатор, дешифраторы и две схемы «И, причем счетиый вход следящего счетчика соединен

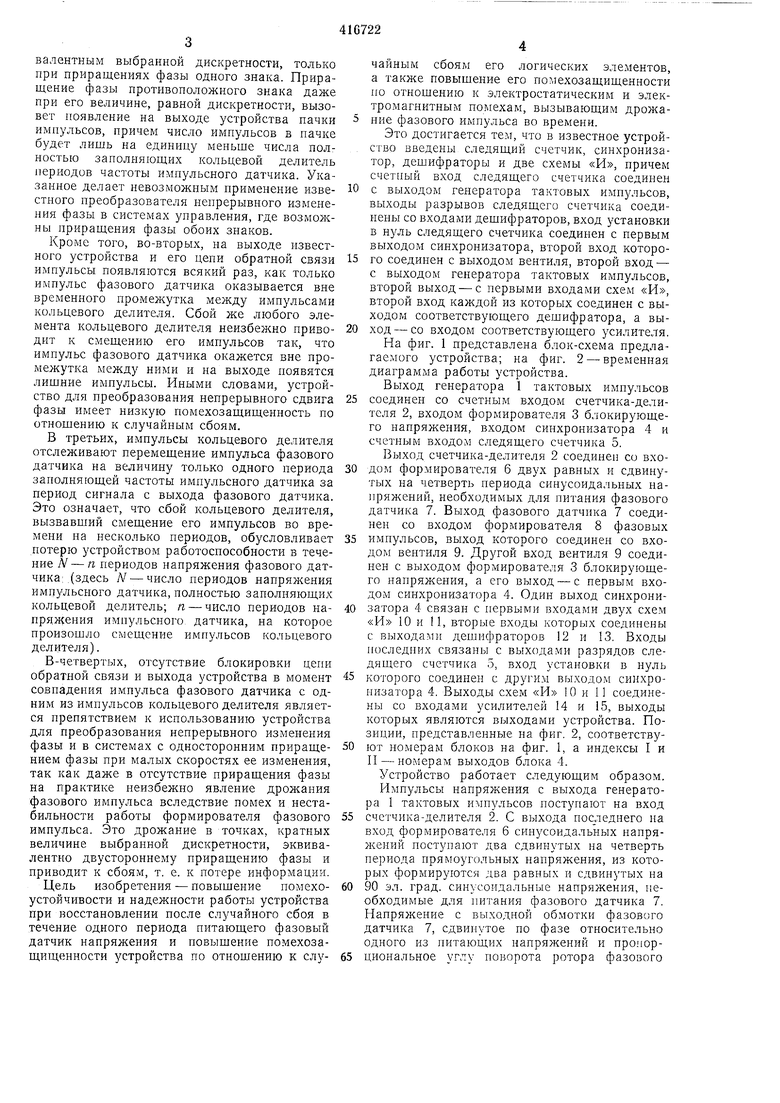

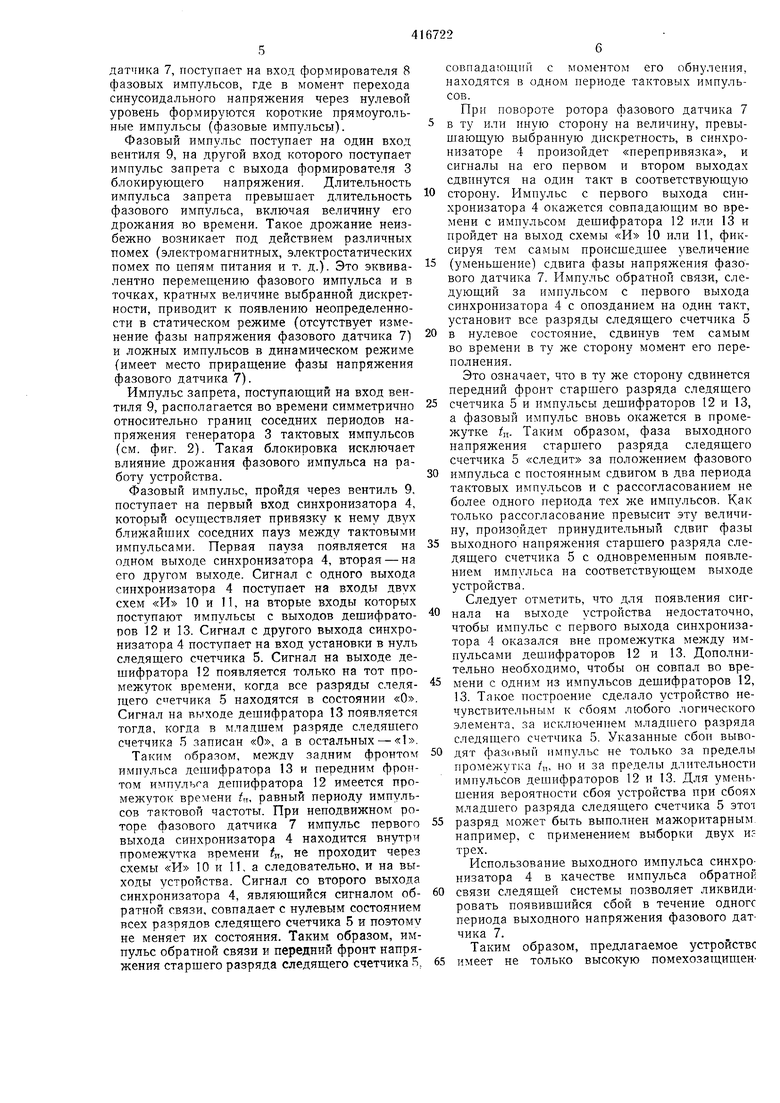

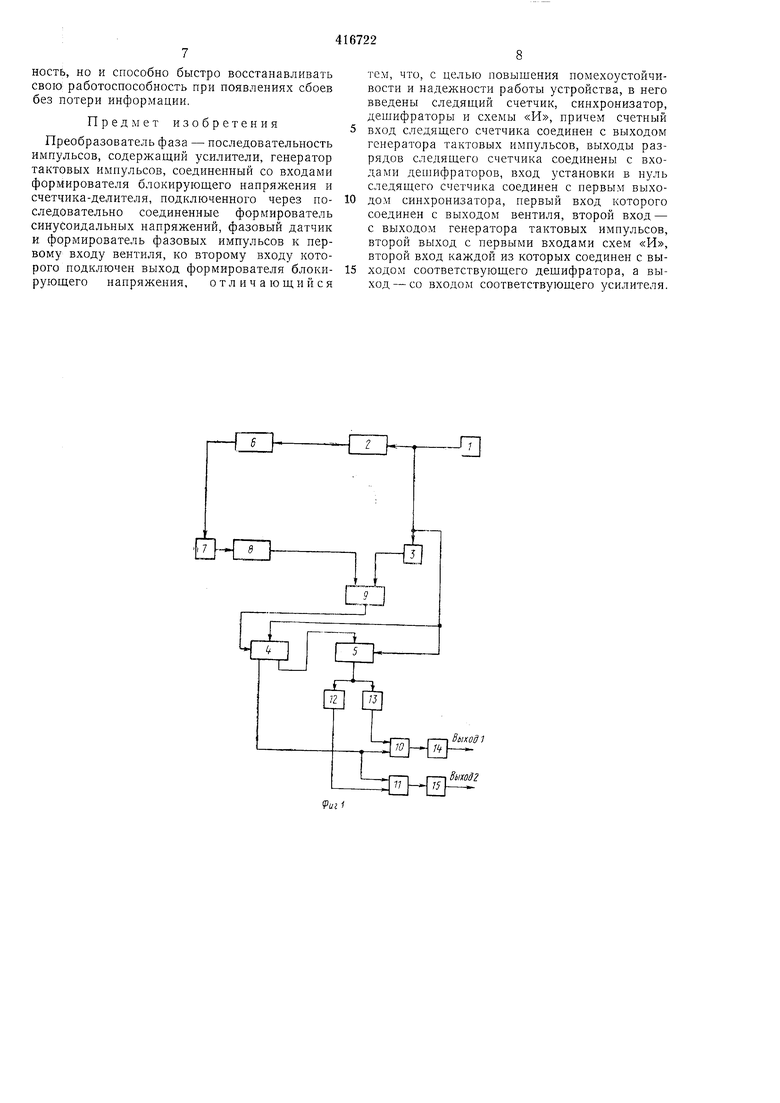

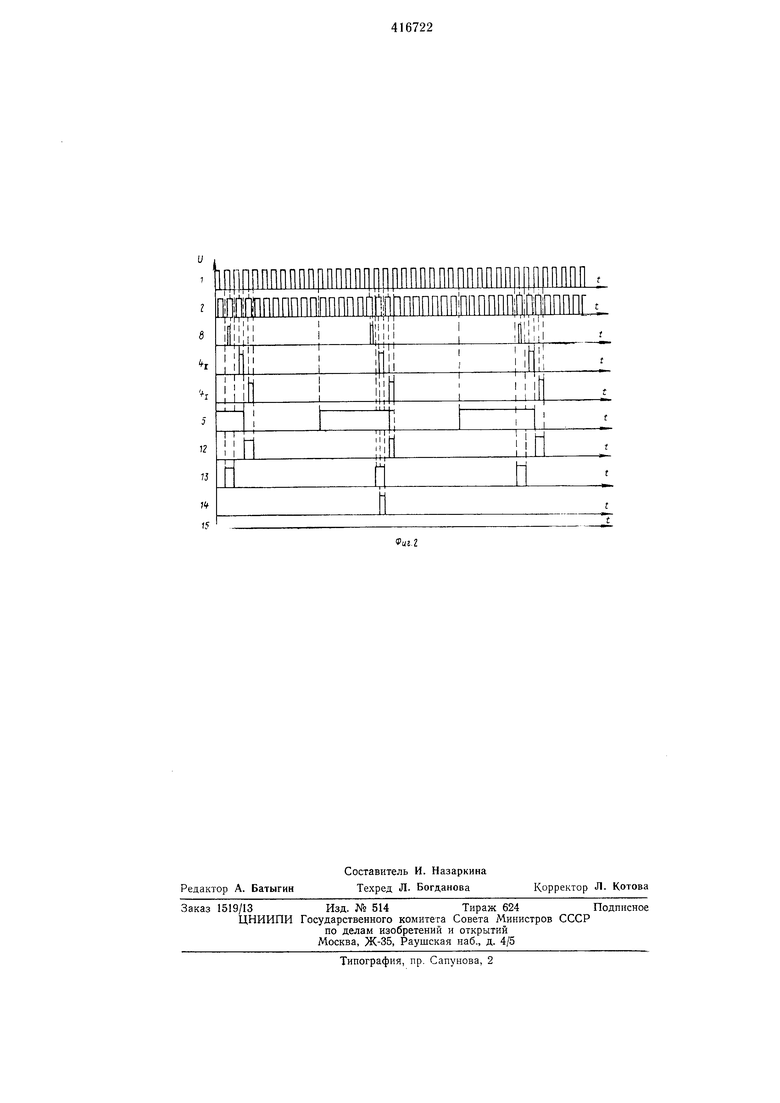

с выходом генератора тактовых импульсов, выходы разрывов следящего счетчика соединены со входами дещифраторов, вход установки в нуль следящего счетчика соединен с первым выходом синхронизатора, второй вход которого соединен с выходом вентиля, второй вход - с выходом генератора тактовых импульсов, второй выход - с первыми входами схем «И, второй вход каждой из которых соединен с выходом соответствующего дешифратора, а выход - со входом соответствующего усилителя. На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы устройства.

Выход генератора 1 тактовых импульсов

соединен со счетным входом счетчика-делителя 2, входом формирователя 3 блокирующего напряжения, входом синхронизатора 4 и счетным входом следящего счетчика 5.

Выход счетчика-делителя 2 соединен со входом формирователя 6 двух равных и сдвинутых на четверть периода синусоидальных напряжений, необходимых для питания фазового датчика 7. Выход фазового датчика 7 соединен со входом формирователя 8 фазовых

импульсов, выход которого соединен со входом вентиля 9. Другой вход вентиля 9 соединен с выходом формирователя 3 блокирующего напряжения, а его выход - с первым входом синхронизатора 4. Один выход синхронизатора 4 связан с первыми входами двух схем «И 10 и 11, вторые входы которых соединены с выходами дешифраторов 12 и 13. Входы последних связаны с выходами разрядов следящего счетчика 5, вход установки в нуль

которого соединен с другим выходом синхронизатора 4. Выходы схем «И 10 и II соединены со входами усилителей 14 и 15, выходы которых являются выходами устройства. Позиции, представленные на фиг. 2, соответствуют номерам блоков на фиг. 1, а индексы I и П - номерам выходов блока 4. Устройство работает следующим образом. Импульсы напряжения с выхода генератора 1 тактовых импульсов поступают на вход

счетчика-делителя 2. С выхода последнего на вход формирователя 6 синусоидальных напряжений поступают два сдвинутых на четверть периода прямоугольных напряжения, из которых формируются два равных и сдвинутых на

90 эл. град, синусоидальные напряжения, необходимые для питания фазового датчика 7. Напряжение с выходной обмотки фазового датчика 7, сдвинутое по фазе относительно одного из нитающих напряжений и пропорциональное углу поворота ротора фазового

датчика 7, поступает на вход формирователя 8 фазовых импульсов, где в момент перехода синусоидального напряжения через нулевой уровень формируются короткие прямоугольные импульсы (фазовые импульсы).

Фазовый импульс поступает на один вход вентиля 9, на другой вход которого поступает импульс запрета с выхода формирователя 3 блокирующего напряжения. Длительность импульса запрета превышает длительность фазового импульса, включая величину его дрожания во времени. Такое дрожание неизбежно возникает под действием различных помех (электромагнитных, электростатических помех по цепям питания и т. д.). Это эквивалентно перемещению фазового импульса и в точках, кратных величине выбранной дискретности, приводит к появлению неопределенности в статическом режиме (отсутствует изменение фазы напряжения фазового датчика 7) и ложных импульсов в динамическом режиме (имеет место приращение фазы напряжения фазового датчика 7).

Импульс запрета, поступающий на вход вентиля 9, располагается во времени симметрично относительно границ соседних периодов напряжения генератора 3 тактовых импульсов (см. фиг. 2). Такая блокировка исключает влияние дрожания фазового импульса на работу устройства.

Фазовый импульс, пройдя через вентиль 9. поступает на первый вход синхронизатора 4, который осуществляет привязку к нему двух ближайщих соседних пауз между тактовыми импульсами. Первая пауза появляется на одном выходе синхронизатора 4, вторая - на его другом выходе. Сигнал с одного выхода синхронизатора 4 поступает на входы двух схем «И 10 и И, на вторые входы которых поступают импульсы с выходов дешифраторов 12 и 13. Сигнал с другого выхода синхронизатора 4 поступает на вход установки в нуль следящего счетчика 5. Сигнал на выходе дешифратора 12 появляется только на тот промежуток времени, когда все разряды следящего счетчика 5 находятся в состоянии «О. Сигнал на выходе дешифратора 13 появляется тогда, когда в младшем разряде следящего счетчика 5 записан «О, а в остальных- «1.

Таким образом, между задним фронтом импульса дешифратора 13 и передним фронтом импулыа дешифратора 12 имеется промежуток времени п, равный периоду импульсов тактовой частоты. При неподвижном роторе фазового датчика 7 импульс первого выхода синхронизатора 4 находится внутри промежутка времени #„, не проходит через схемы «И 10 и 11, а следовательно, и на выходы устройства. Сигнал со второго выхода синхронизатора 4, являющийся сигналом обратной связи, совпадает с нулевым состоянием всех разрядов следящего счетчика 5 и ПОЭТОМУ не меняет их состояния. Таким образом, ил1пульс обратной связи и передний фронт напряжения старшего разряда следящего счетчика 5,

совпадающий с моментом его обнуления, находятся в одном периоде тактовых импульсов.

При повороте ротора фазового датчика 7

в ту или иную сторону на величину, превышающую выбранную дискретность, в синхронизаторе 4 произойдет «перепривязка, и сигналы на его первом и втором выходах сдвинутся на один такт в соответствующую

сторону. Импульс с первого выхода синхронизатора 4 окажется совпадающим во времени с импульсом дешифратора 12 или 13 и пройдет на выход схемы «И 10 или 11, фиксируя тем самым происшедшее увеличение

(уменьшение) сдвига фазы напряжения фазового датчика 7. Импульс обратной связи, следующий за импульсом с первого выхода синхронизатора 4 с опозданием на один такт, установит все разряды следящего счетчика 5

в нулевое состояние, сдвинув тем самым во времени в ту же сторону момент его переполнения.

Это означает, что в ту же сторону сдвинется передний фронт старшего разряда следящего

счетчика 5 и импульсы дешифраторов 12 и 13, а фазовый импульс вновь окажется в промежутке tn. Таким образом, фаза выходного напряжения старшего разряда следящего счетчика 5 «следит за положением фазового

импульса с постоянным сдвигом в два периода тактовых импульсов и с рассогласованием не более одного периода тех же импульсов. Как только рассогласование превысит эту величину, произойдет принудительный сдвиг фазы

выходного напряжения старшего разряда следящего счетчика 5 с одновременным появлением импульса на соответствующем выходе устройства.

Следует отметить, что для появления сигнала на выходе устройства недостаточно, чтобы импульс с первого выхода синхронизатора 4 оказался вне промежутка между импульсами дешифраторов 12 и 13. Дополнительно необходимо, чтобы он совпал во времени с одним из импульсов дешифраторов 12, 13. Такое построение сделало устройство нечувствительпь м к сбоям любого логического элемента, за исключением младшего разряда следящего счетчика 5. Указанные сбои выводят импульс не только за пределы промежутка /„, но и за пределы длительности импульсов дешифраторов 12 и 13. Для уменьшения вероятности сбоя устройства при сбоях младшего разряда следящего счетчика 5 этот

разряд может быть выполнен мажоритарным, например, с применением выборки двух и.трех.

Использование выходного импульса синхронизатора 4 в качестве импульса обратной

связи следящей системы позволяет ликвидировать появившийся сбой в течение одногс периода выходного напряжения фазового датчика 7.

Таким образом, предлагаемое устройстве имеет не только высокую помехозащищеН

7

ность, но и способно быстро восстанавливать свою работоспособность при появлениях сбоев без потери информации.

Предмет изобретения

Преобразователь фаза - последовательность импульсов, содержащий усилители, генератор тактовых импульсов, соединенный со входами формирователя блокирующего напряжения и счетчика-делителя, подключенного через последовательно соединенные формирователь синусоидальных напряжений, фазовый датчик и формирователь фазовых импульсов к первому входу вентиля, ко второму входу которого подключен выход формирователя блокирующего напряжения, отличающийся

тем, что, с целью повышения помехоустойчивости и надежности работы устройства, в него введены следящий счетчик, синхронизатор, дешифраторы и схемы «И, причем счетный

вход следящего счетчика соединен с выходом генератора тактовых импульсов, выходы разрядов следящего счетчика соединены с входами деп ифраторов, вход установки в нуль следящего счетчика соединен с первым выходом синхронизатора, первый вход которого соединен с выходом вентиля, второй вход - с выходом генератора тактовых импульсов, второй выход с первыми входами схем «И, второй вход каждой из которых соединен с выходом соответствующего дешифратора, а выход-со входом соответствующего усилителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угол-дискретное приращение фазы | 1977 |

|

SU710057A1 |

| Фазоимпульсный преобразователь | 1983 |

|

SU1161977A1 |

| Устройство для регулирования скорости электродвигателя | 1984 |

|

SU1267375A1 |

| Преобразователь углового перемещенияВАлА B КОд | 1979 |

|

SU842896A1 |

| Видеорегенератор для систем связи с импульсно-кодовой модуляцией | 1977 |

|

SU792603A1 |

| Датчик углового положения,скорости и ускорения вращения вала | 1983 |

|

SU1101740A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Следящий измеритель частоты | 1985 |

|

SU1298675A1 |

| Двухотсчетный преобразователь угла поворота вала в код | 1977 |

|

SU734776A1 |

| Устройство для управления следящим приводом | 1978 |

|

SU736052A1 |

гЧИ

i7

8t:IXOg 1

SbiwdZ

Даты

1974-02-25—Публикация

1971-12-21—Подача