1

Изобретение относится к автоматике и вь числительной технике и может быть использовано для уменьшения динамической ошибки и расширения динамического диапазона при умножении частоты следования импульсов.

Известно устройство умножения частоты следоваиия импульсов, основанное на обратно-пропорциональном преобразовании в частоту кода, пропорционального периоду входной частоты, уменьшенному в число раз, равное коэффициенту умножения и содержашее последовательно соединенные формирователь, блок умножения и нреобразователь кода 1.

Наиболее близким ПО технической сушности к данному изобретению является устройство умножения частоты следования импульсов, содержашее генератор оиорной частоты, блок управления, два делителя частоты, каждый из которых состоит из вычитаюшего счетчика и регистра памяти, соединенных через вентиль ввода кода, управляюший вход которого подключен к выходу вычитаюшего счетчика, и суммирующий счетчик, кодовый выход которого через вентиль переноса кода соединен с установленным входом регистра памяти первого делителя частоты, при этом выход генератора опорной частоты подключен ко входу вычитаюшего счетчика первого делителя частоты непосредственно, а к счетному входу

2

суммируюшего счетчика-через второй делитель частоты, установочный вход которого подключен к клемме источника входного сигнала 2.

Недостатками указанных устройств являются запаздывание на текущий период, ограниченная динамическая точность, уменьшающаяся с увеличением скорости изменения входного сигнала, и узкая динамическая область применения, в основном для медленно изменяющихся входных сигналов.

Целью изобретения является повыщение быстродействия и точности работы устройства.

Для этого в устройство введены два дополнительных делителя частоты, переключающий элемент, блок вычитания частот, умножитель частоты, блок суммирования частот, триггер и дополнительные вентили переноса кода, причем выход первого делителя частоты и выход первого дополнительного делителя частоты через переключающий элемент подключены ко входам блока вычитания частот, выход которого через триггер соединен с первым входом блока суммирования частот и через второй дополнительный делитель частоты с первым входом умножителя частоты, выход чоторого подключен ко второму входу блока суммирования частот, третий вход которого соединен с выходом переключающего элемеита, управляющий вход-со знаковым выходом блока вычитаяия частот, а выход является выходом устройства, при этом выход генератора опорной частоты подключен к импульсному входу ;первого дополнительного делителя частоты и ко второму входу умножителя частоты, а установочные входы дополпигельных делителей частоты подключены к кодовому выходу суммируюпцего счетчш-са через донолнптельные вентили нереноса кода, управляющие входы которых соединены с одними выходами блока управления, другие выходы которого подключены к управляющим входам умножителя частоты и переключающего элемента, к |Сбросовым входам суммирующего счетчика и регистров памяти первого и двух дополнительных делителей частоты.

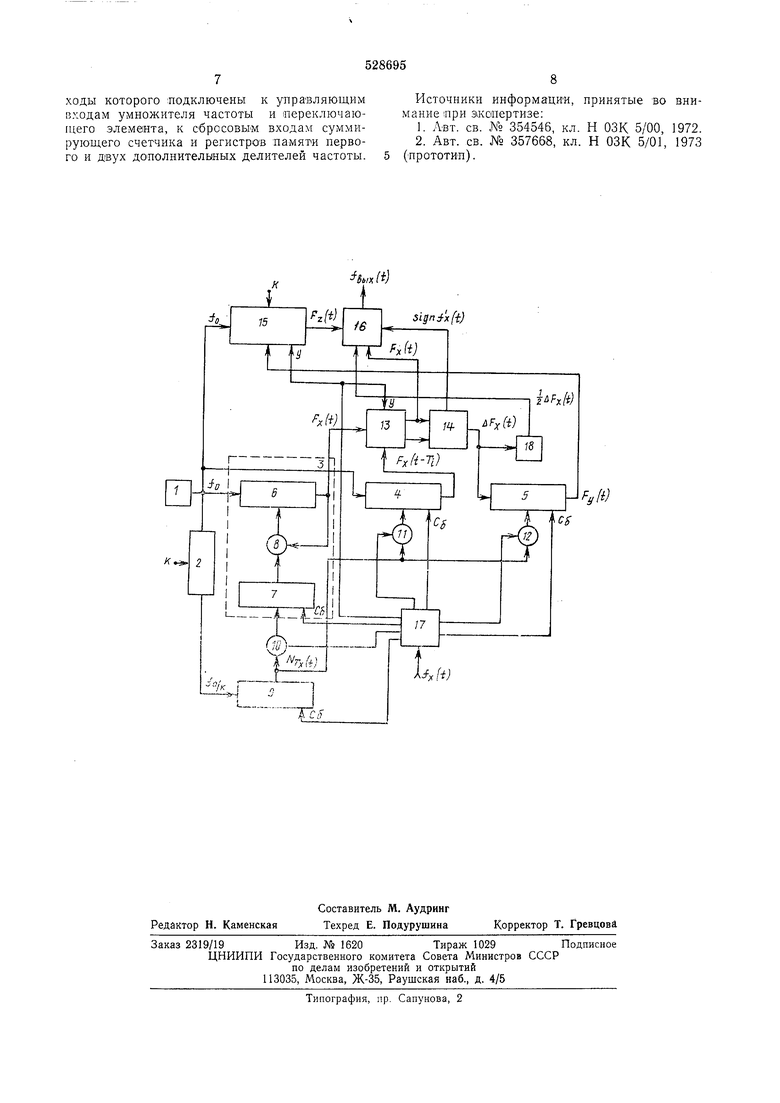

На чертеже показана структурная электрическая схема предлагаемого устройства.

Устройство содержит генератор 1 опорной частоты; четыре делителя частоты .2-5, ка;кдый из которых состоит из вычитающего счетЧИКа 6, регистра памяти 7 и вентилей 8 нереноса кода но числу разрядов счетчика и регистра, суммирующий счетчик 9 импульсов; eeHTH ii 10-12 переноса кода в делители частоты 3, 4, 5; переключающий элемент 13; блок 14 вычгГгапия частот; .умножитель 15 частот; блок 16 суммирования частот; блок 17 управления и триггер 18 со счетным входом.

Работает устройство следующим образом.

Выходные импульсы генератора 1, следующие с высокой частотой /о, поступают на входы вычитающих счетчиков в делителях частоты 2, 3 и 4, а также на вход счетчпка-делителя в умножителе 15, выполняющего роль интегратора частоты. В регистр памяти делителя частоты 2 введен код коэффициента умножения устройства К, являющийся для делителя частоты 2 Коэффициентом деления. На выходе делителя частоты 2 образуются импульсы, следующие с частотой

f /о

Эти импульсы Поступают на счетный вход суммирующего счетчика 9, на сбросовый вход которого поступают сигналы управлепия от блока 17 управления. В блоке управления из импульсов входной частоты /ж (О формируются сигналы, управляющие последовательностью работы всех блоков устройства. Сигналы сброса на суммирующий счетчик 9 поступают при приходе каждого имнульса входной частоты, в результате чего в суммирующем счетчике 9 подсчитываются импульсы входной частоты за время, равное периоду входной частоты, а на кодовых выходах счетчика к этим моментам образуется код, пропорциональный периоду входной частоты

.ИО-|--7.(0.

Этот код каждый раз перед сбросом суммирующего счетчика 9 по сигналам управления

от блока 17 переписывается в предварительно очищ,еппые регистры памяти делителя частоты о и одтаого из делителей частоты 3 или 4 в заиисимост; от того, в памяти какого из Них хранится код, пропорциональный предыдущему периоду. Если код предыдущего периода записан в памяти делителя частоты 4., то код очередного периода Лтг запищется в память делителей частоты 3 и 5. Обратный код Nil из регистра памяти 7 делителя частоты 3 каждым импульсом с выхода вычитающего счетчика 6 через вентили 8 записывается в этот счетчик, установленный первоначально в положение (п-число разрядов счетчика). После списания из вычитающего счетчика 6 записанного в него кода имнульсами входной частоты /о генератора 1,на выходе вычитающего счетчика 6 появляется новый импульс, повторяющий процесс деления. Импульсы па выходе вычитающего счетчика 6 будут появляться с частотой

FAti)..

(3)

Tl

Таким образом, на выходе делителя частоты 3 образуется частота, увеличенная щ К раз по сравнению с входной.

Для получения частоты, пропорциональной производной входного сигнала, в устройство

введен частотно-импульсный быстродействующий дифференциатор, образованный двумя делителями частоты 4, 5, вентилями 11, 12 ввода кода, переключающим элементом 13 и блоком 14 вычитания частот. Блок 17 управленпя управляет работой устройства так, что, если после «г-го такта умножения в памяти делителей частоты 3 и 5 введен код «г-го периода Лт;. Соответственно в следующий «г + + 1 такт умножения код «i+1 периода будет запнсаН в память делителей частоты 4 и 5. Благодаря такому управлению на выходе делителя частоты 3 и 4 всегда будут образовываться частоты, отстающие одна от другой на предыдущий период входной частоты. Так

после «г-го такта на выходе делителя частоты 3 изменится частоты и будет соответствовз ь выражению (3), а на выходе делителя частоты 4 останется прежняя частота, соответствующая «if-Ь периоду и равная

F(t,.i) - т,) .К-1, (h - г,). (4)

Импульсы с выходов делителей частоты 3 и 4 поступают через переключающий элемент 13 на входы блока вычитания частот.

Переключающий элемент 13 управляется от блока 17 таким образом, что в момент прихода очередного импульса входной частоты выходы блока 13 переключаются, меняясь местами, благодаря чему на одном из его выходов всегда будет опережающий по времени сигнал. На вход блока 13 вычитания частот подаются импульсы частот, задержанных один относительно другого на величину периода входной частоты. Как известно, нри вычитапии из исходного сигнала Fx(ti) задержанного Fx{ti-Ti), получается частота, пропорциональная первой произзоднор исходного сигнала и времени задержки: AF (ti) F ((, - F, (ti - Tt) F; (tf) ТI + + F:(T,)-n + ... F:,((i).Ti + + ,(, где R-cvMAia отброшенных членов ряда Тейлора, представляющая собой методическую ошибку и стремяшаяся к нулю при уменьшении времени задержки и малых значениях высших производных на этих интервалах. Чтобы получить частоту, не зависящую от периода изменения входной частоты, выходную частоту блока вычитания частот делят в делителе частоты 5 на код, пропорциональный «г-му периоду. Импульсы с частотой Fx(ti) поступают на импульсный вход делителя частоты 5, в память которого занесен код из суммирующего счетчика 9. На выходе делителя частоты 5 образуются импульсы, следующие С частотой .(.).), Ttу о т. е. пропорциональной только производной входного сигнала. Импульсы с частотой Fy(ti с выхода делителя частоты 5 поступают на вход счетчикаинтегратора умножителя частоты 15, на вход счетчика-делителя которого поступают импульсы с частотой /о с генератора (.Умножитель частоты выполняет роль частотного интегратора и запускается по сигналу управления с блока управления. На выходе умножителя частоты образуется частота t р. (ii} f f у (/) () (О где t - время, меняющееся от ti до i+i. Таким образом, на выходе умножителя частоты образуется частота, изменяющаяся липейно во времени с козффициентом, равным производ 1ой умпожепной частоты, т. е. осуществляется питегрировакие во времени частоты, пропорциональной производной умпоженпой частоты. На входы блока суммирования частот поступают ИМПУЛЬСЫ с выхода умножителя частоты с частотой fz(fi, с выхода переключающего элемента 13 с частотой Fx(ti) и с выхода блока 14 вычитания частот, поделенной на два в триггере 18 со счетным входом, с частотой (ti). Управляет работой блока суммирования частот знаковый сигнал sign/.,;(/,) с выхода блока вычитания частот, который характеризует знак приращения умноженной частоты и производной входного сигнала. В зависимости от этого знака к частоте Px(ti} прибавляются или из нее вычитаются частоты (ti) и ). Блок суммирования частот может быть построен на блоках вычитания частот по числу входных сигналов с вводом промежуточной частоты. Тогда она легко перестраивается с суммирования на вычитание частот. Частота на выходе блока суммирования частот для текущего «t+1-го периода будет равна /в« (Ti,i)K ) ± ± /;(/)-. Формула изобретения Устройство умножения частоты следования пмнульсов, содержащее генератор опорной частоты, блок управления, два делителя частоты, каждый из которых состоит из вычитающего счетчика и регистра памяти, соединенных через вентиль ввода кода, управляющий вход которого Подключен к выходу вычитающего счетчика, ц суммирующий счетчик, кодовый выход которого через вентиль переноса кода соединен с установочным входом регистра памяти первого делителя частоты, при этом выход генератора опорной частоты подключен ко входу вычитающего счетчика первого делителя частоты непосредственно, а к счетному входу суммирующего счетчика-через второй делитель частоты, установочный вход которого подключен к клемме источника входного сигнала, отличающееся тем, что, с целью повышения быстродействия и точности работы устройства, в него введены два дополнительных делителя частоты, переключающий элемент, блок вычитания частот, умножитель частоты, блок суммирования частот, триггер и дополнительные вентили переноса кода, причем выход первого делителя частоты и ВЫХОД первого дополнительного делителя частоты через переключающий элемент подключены ко входам блока вычитания частот, выход которого через триггер соединен с первым входом суммирования частот и через второй дополнительный делитель частоты с первым входом умножителя частоты, выход которого подключен ко второму входу блока суммирования частот, третий вход которого соединен с выходом переключающего элемента, управляющий вход-со знаковым выходом блока вычитання частот, а выход является выходом устройства, при этом выход генератора опорной частоты подключен к импульсному входу первого дополнительного делкте; я частоты и ко второму входу умножителя частоты, а устяновочные входы доиол Ительных леллтслей частоты подключены к кодовому выходу суммМрующего счетчика чере:4 дополнитепьиыс вектили нереноса кода, упра зляющ1с входы которых соединены с однпми выходами бло1:а управления, другие выходы которого лодключены к управляющим входам умножителя частоты и переключающего элемента, к сбросовым входам суммирующего счетчика и регистров памят-и первого и двух дололнителвных делителей частоты. 5 Источники информация, принятые во внимание при экспертизе; 1.Авт. св. 354546, кл. Н ОЗК 5/00, 1972. 2.Авт. св. № 357668, кл. Н ОЗК 5/01, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифферинцирования частотно-импульсных сигналов | 1975 |

|

SU526916A1 |

| Умножитель частоты импульсов | 1978 |

|

SU780175A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1978 |

|

SU742967A1 |

| Устройство для преобразования суммы частотно-импульсных сигналов в код | 1976 |

|

SU657441A1 |

| Способ измерения частоты импульсного сигнала и устройство для его осуществления | 1980 |

|

SU911359A1 |

| Устройство для дифференцирования частотно-импульсных сигналов | 1980 |

|

SU894729A1 |

| Умножитель частоты | 1980 |

|

SU928354A1 |

| Устройство для дифференцирования частотноимпульсных сигналов | 1974 |

|

SU495675A1 |

| Цифровой измеритель скорости вращения асинхронного электродвигателя | 1976 |

|

SU632956A1 |

| Устройство для умножения частоты | 1991 |

|

SU1836681A3 |

0.

Авторы

Даты

1976-09-15—Публикация

1975-05-04—Подача