1

Изобретение относится к вычислительной и измерительной технике. Оно может быть использовано в качестве математического узла, выполняюш.его множительно-делительную операцию, или в качестве устройства для усиления частоты.

Известно устройство подобного назначения, содержащее разомкнутое множительно-делительное устройство, реверсивный счетчик, преобразователь кода в напряжение, управляемый генератор частоты, анализатор динамической ошибки, в состав которого входит реверсивный счетчик, группу импульсно-потенциальных схем совпадения, запоминающее устройство, состоящее из счетчика импульсов и схем совпадения и вычитающее устройство. Оно характеризуется больщим временем переходного процесса, определяемым параметрами следящей системы (апериодическое звено).

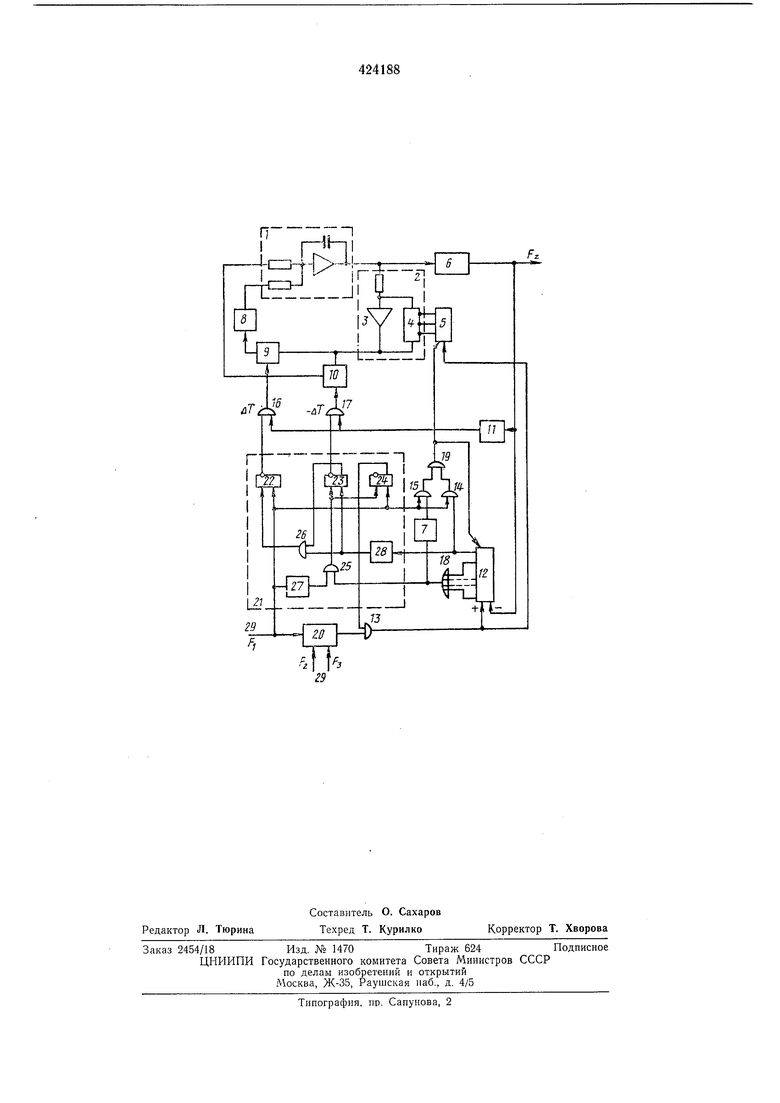

Целью изобретения является увеличение быстродействия устройства и получение мгновенного (периодного) значения выходной частотно-импульсной последовательности. Это достигается тем, что устройство содержит ключи, интегратор и блок выделения разности периодов, входы которого подключены к шине входной частоты, выходу схемы «ИЛИ и выходу реверсивного счетчика, а выходы соединены со вторым входом первой схемы «И и с первыми входами четвертой и пятой схем «И, вторые входы которых подключены к выходу временного калибратора; выходы четвертой и пятой схем «И соединены с первыми входами соответственно первого и второго ключей, вторые входы которых присоединены к выходу блока деления напрял ения на код; выход первого ключа через второй инвертор, а выход второго ключа непосредственно присоединены ко входам интегратора, выход которого подключен ко входам управляемого генератора частоты и блока деления напряжения на код. На чертеже приведена структурная схема

устройства.

Устройство содержит интегратор 1, блок деления напряжения на код 2, состоящий из усилителя постоянного тока 3 и преобразователя кода в напряжение 4; счетчик импульсов 5; управляемый генератор частоты 6; инверторы 7 и 8; ключи 9 и 10, временный калибратор 11; реверсивный счетчик 12; схемы «И 13, 14, 15, 16 и 17, схемы «ИЛИ 18 и 19; множительноделительный блок 20; блок выделения разности периодов 21, включающий три триггера 22, 23 и 24, схемы «И 25 и 26, элемент задерл ки 27 и формирователь импульсов 28. В устройстве шины входных частот 29 (Fi, F и FZ) соедиБены с входами множительно-делительного блока 20. Кроме того, шина частоты

Pi соединена с единичнььми установочными входами триггеров 22 и 24, входами схем «И 14 и 15 и через элемент задержки 27 - со входом схемы «И 25. Выход множительноделительного блока 20 через схему «И 13 соединен с суммирующим входом реверсивного счетчика 12 и входом счетчика имнульсов 5, выходы триггеров которого нодключены к кодовым шинам блока деления напряжения на код 2, выходом соединенного со входами ключей 9 и 10. Ключ 10 выходом соединен с одним ВХ10ДО|М интегратора 1, который другим входом через второй инвертор 8 соединен с выходом ключа 9, а выходом - со входами блока деления напряжения на код 2 и унравляемого генератора частоты 6. Выход управляемого генератора частоты 6 соединен с шиной выходной частоты FZ, входом временного калибратора 11, вычитающим входом реверсивного счетчика 12, единичные выходы триггеров которого соединены со входами первой схемы «ИЛИ 18, выходом подключенной ко входу схемы «И 25 и входу нервого инвертора 7. Выход последнего через третью схему «И 15 соединен со входом схемы «ИЛИ 19, выход которой подключен к шинам установки в нуль счетчика импульсов 5 реверсивного счетчика 12, а второй вход схемы «ИЛИ 19 нодключен к выходу второй схемы «И 14, которая входом соединена с единичным выходом старшего триггера реверсивного счетчика 12 и через формирователь импульсов 28 - со входом схемы «И 26 и единичным установочным входом триггера 23. Нулевой установочный вход триггера 23 соединен с выходом схемы «И 25 и нулевым установочным входом триггера 24, у которого единичный выход соединен со входом первой схемы «И 13. Кроме того, единичный выход триггера 23 через схему «И 26 соединен с нулевым установочным входом триггера 22, который нулевым выходом соединен со входом схемы «И 16, которая выходом подключена ко входу первого ключа 9, а вторым входом - к выходу временного калибратора И и входу пятой схемы «И 17, второй вход которой подключен к нулевому выходу триггера 23, а выход - ко входу второго ключа 10.

Рассмотрим работу устройства для случаев, когда входная частота Л увеличивается и уменьшается.

В установившемся режиме число имнульсов выходной частоты за период равно числу импульсов в «пачке Ni Fa/Fz, и к моменту прихода имнульса частоты i реверсивный счетчик 12 будет обнулен. В этом случае триггеры 22 и 23 находятся в единичном состоянии, а триггер 24 - в нулевом. Поэтому импульсы выходной частоты F не проходят через схемы «И 16 и 17 на вход ключей 9 и 10, т. е. цепь обратной связИ интегратора 1 разорвана. Установка счетчика 5 в нулевое состояние нроисход-ит через схему «И 15, которая открыта инвертированным потенциалом с выхода схемы «ИЛИ 18. Выход последней

подключен к единичным выходам триггера реверсивного счетчика 12, т. е. при обнуленном реверсивном счетчике 12 на выходе первого инвертора 7 будет разрешающий потенциал.

Если период 7 увеличился и стал равен .r.-i-A7 тогда при переходе реверсивного счетчика из состояния 00 ... 00 в состояние 11 ... 11 (что соответствует значению кода -1) от нерепада потенциала на выходе старшего триггера реверсивного счетчика 12 триггер 22 устанавливается в нулевое состояние, и на вход ключа 9 с выхода временного калибратора И поступают импульсные частоты FZ длительностью ТоСреднее значение напряжения на выходе ключевой схемы 7 равно

АГ.ГО

6с„

t--инт

ср

где Ki - коэффициент усилителя постоянного

тока;

Kz - коэффициент пронорциональности; Ьипт. - напряжение интегратора;

Ni - число имнульсов в «пачке. Таким образом, до момента прихода имнульса частоты FI, т. е. на время (+АГ), в цень обратной связи интегратора 1 включено устройство, воснроизводящее квадратичную зависимость, причем напряжение, снимаемое с интегратора, дважды инвертируется. Закон изменения напряжения на выходе интегратора 1 онределяется из выражения

f/o

кт -

У.

1 + .т + KtRC

Пришедший импульс частоты fi устанавливает триггер 22 в единичное состояние, тем самым закрывая четвертую схему «И 16 и разрывая обратную связь интегратора 1. Этот же импульс, проходя вторую схему «И 14, устанавливает в нулевое состояние реверсивный счетчик 12 и счетчик импульсов 5. Разрешающий потенциал на вторую схему «И 14 подается с единичного счетчика 12, который находится в единичном состоянии при отрицательном числе в реверсивном счетчике. При уменьшении нериода

1Н - IC.T Т

к моменту прихода импульса частоты FI в ревер.оввном счетчике 12 останется оп|ределенное число б несписанных имнульсов. Тогда схемы «И 14 и 15 будут закрыты и счетчики 12

и 5 не обнулются. Импульс частоты Fi, задержанный в элементе задержки 27, через открытую схему «И 25 нодается на нулевые установочные входы триггеров 23 и 24. Интервал времени {-АГ) будет равен Ar 6-7z текущее и закончится при переходе реверсивного счетчика 12 из состояния 00 ... 00 в 11 ... 11. Импульс, сформированный от нерепада, установит триггер 23 в единичное состояние, но не пройдет схему «И 26, так как имеется задержка в установке триггера 23.

Напряжение на выходе интегратора

и.

нт

дг

1 -

С.дедующий импульс частоты F устанавливает триггер 24 в единичное состояние, т. е. разрешает прохождение «начек имнульсов через схему «И 17, и, проходя схему «И 14, устанавливает счетчики 12 и 5 в нулевое состояние. Задержанный в элементе задержки 27 импульс частоты fi, не проходит схему «И 25 и триггер 23 остается в единичном состоянии.

Таким образом, устройство позволяет при уменьшении частоты /i к концу первого периода измененной частоты получить необходимое значение выходной частоты F, а при увеличении входной частоты F - точное значение выходной частоты через два периода частоты Fi.

Предмет изобретения

Частотно-импульсное множительно-делительное устройство, содержаш,ее множительноделительный блок, входы которого подключены к шинам |входйых частот, а выход соединен с первым входом первой схемы «И, выход которой присоединен к первому входу реверсивного счетчика и первому входу счетчика импульсов, выходы которого соединены со входами блока деления нанряжения на код;

управляемый генератор частоты, выход которого соединен с выходом устройства, входом временного калибратора и вторым входом реверсивного счетчика, выходы которого присоединены к первому входу второй схемы «И и входам первой схемы «ИЛИ, выход которого через первый инвертор соединен с первым входом третьей схемы «И, вторые входы указанных схем «И присоединены к шине входной частоты, а их выходы через вторую схему «ИЛИ подключены ко второму входу счетчика импульсов и входу «установка в нуль реверсивного счетчика; второй инвертор и схемы «И, отличаюш,ееся тем, что, с

нелью повышения быстродействия, оно содержит ключи, интегратор и блок выделения разности периодов, входы которого подключены к шине входной частоты, выходу схемы «ИЛИ и выходу реверсивного счетчика, а выходы соединены со вторьш входом первой схемы «И и с первыми входами четвертой и пятой схем «И, вторые входы которых подключены к выходу временного калибратора; выходы четвертой и пятой схем «И соединены

с первыми входами соответственно первого и второго ключей, вторые входы которых присоединены к выходу блока деления напряжения на код; выход первого ключа через второй инвертор, а выход второго ключа непосредственио присоединены ко входам интегратора, выход которого подключен ко входам управляемого генератора частоты и блока деления напряжения на код.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Устройство для измерения амплитуды синусоидального сигнала | 1985 |

|

SU1302203A1 |

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| УМНОЖИТЕЛЬ ЧАСТОТЫ СИГНАЛОВ | 1971 |

|

SU420082A1 |

| Устройство для извлечения корня | 1975 |

|

SU552620A1 |

| Аналого-цифровой преобразователь температуры | 1979 |

|

SU855412A1 |

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Частотно-импульсное устройство преобразования сигнала с мостового датчика | 1986 |

|

SU1383474A1 |

| Устройство для управления инвертором | 1990 |

|

SU1709482A1 |

Даты

1974-04-15—Публикация

1972-06-02—Подача