Изобретение относится к цифровой измерительной технике, а именно к устройствам измерения параметров сигналов, и может быть использовано для измерения амплитуды синусоидального напряжения, имеющего постояннзто составляющую.

Цель изобретения - повышение точности измерений, быстродействия и помехозащищенности за счет оптимизации режима работы компаратора и автоматического применения тактовой частоты при изменяющихся параметрах входного сигнала.

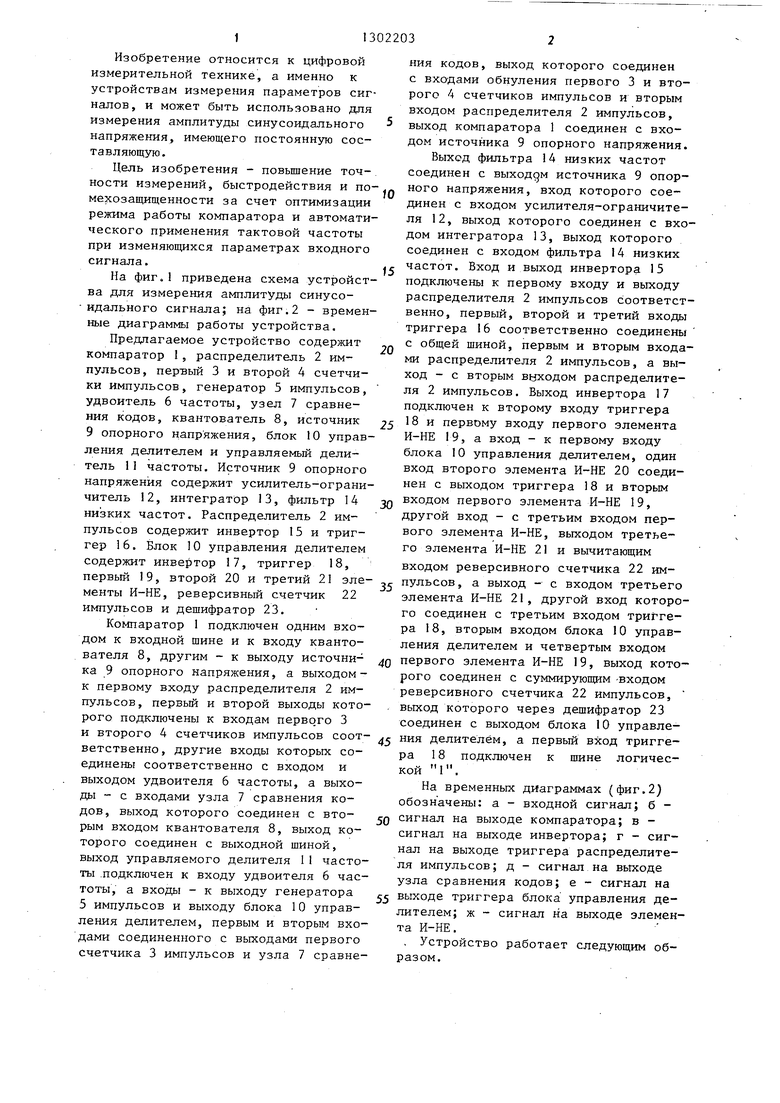

На фиг.1 приведена схема устройства для измерения амплитуды синусоидального сигнала; на фиг.2 - временные диаграммы работы устройства.

Предлагаемое устройство содержит компаратор 1, распределитель 2 импульсов, первый 3 и второй 4 счетчики импульсов, генератор 5 импульсов, удвоитель 6 частоты, узел 7 сравнения кодов, квантователь 8, источник 9 опорного напряжения, блок 10 управления делителем и управляемый делитель 1I частоты. Источник 9 опорного напряжения содержит усилитель-ограничитель 2, интегратор 13, фильтр 14 низких частот. Распределитель 2 импульсов содержит инвертор 15 и триггер 16. Блок 10 управления делителем содержит инвертор 17, триггер 18, первый 19, второй 20 и третий 21 элементы И-НЕ, реверсивный счетчик 22 импульсов и дешифратор 23.

Компаратор I подключен одним входом к входной шине и к входу квантователя 8, другим - к выходу источника 9 опорного напряжения, а выходом- к первому входу распределителя 2 импульсов , первый и второй выходы которого подключены к входам первого 3 и второго 4 счетчиков импульсов соответственно, другие входы которых соединены соответственно с входом и выходом удвоителя 6 частоты, а выходы - с входами узла 7 сравнения кодов, выход которого соединен с вторым входом квантователя 8, выход которого соединен с выходной шиной, выход управляемого делителя 1I частоты .подключен к входу удвоителя 6 частоты, а входы - к выходу генератора 5 импульсов и выходу блока 10 управления делителем, первым и вторым входами соединенного с выходами первого счетчика 3 импульсов и узла 7 сравне

5

0

ния кодов, выход которого соединен с входами обнуления первого 3 и второго 4 счетчиков импульсов и вторым входом распределителя 2 импульсов, выход компаратора 1 соединен с входом источника 9 опорного напряжения.

Выход фильтра 14 низких частот соединен с выходдм источника 9 опорного напряжения, вход которого соединен с входом усилителя-ограничителя 12, выход которого соединен с входом интегратора 13, выход которого соединен с входом фильтра 14 низких частот. Вход и выход инвертора 15 подключены к первому входу и выходу распределителя 2 импульсов соответственно, первый, второй и третий входы триггера 16 соответственно соединены с общей шиной, первым и вторым входами распределителя 2 импульсов, а выход - с вторым вь5ходом распределителя 2 импульсов. Выход инвертора 17 подключен к второму входу триггера

5 18 и первому входу первого элемента И-НЕ 19, а вход - к первому входу блока 10 управления делителем, один вход второго элемента И-НЕ 20 соединен с выходом триггера 18 и вторьм

п входом первого элемента И-НЕ 19, другой вход - с третьим входом первого элемента И-НЕ, выходом третьего элемента И-НЕ 21 и вычитающим входом реверсивного счетчика 22 имс пульсов, а выход - с входом третьего элемента И-НЕ 21, другой вход которого соединен с третьим входом триггера 18, вторым входом блока 10 управления делителем и четвертым входом

0 первого элемента И-НЕ 19, выход которого соединен с суммирующим -входом реверсивного счетчика 22 импульсов, выход которого через дешифратор 23 соединен с выходом блока 10 управле5 ния делителем, а первый вход триггера 18 подключен к шине логичес- II

кой

На временных диаграммах (фиг.2) обозначены: а - входной сигнал; б 5Q сигнал на выходе компаратора; в - сигнал на выходе инвертора; г - сигнал на выходе триггера распределителя импульсов; д - сигнал на выходе узла сравнения кодов; е - сигнал на

55 выходе триггера блока управления делителем; ж - сигнал на выходе элемента И-НЕ.

, Устройство работает следующим образом.

3 1302203

Принцип формирования выходного сигнала компаратора 1 следующий. Для того, чтобы компаратор работал с максимальной точностью и помехозащищенностью, необходимо, чтобы он переклю- 5 чался в моменты времени, когда входной сигнал имеет максимальную скорость изменения.

Для исключения влияния напряжения смещения компаратора 1 и постоянной 0 составляющей входного сигнала на работу компаратора 1 с его выхода на вход заведена обратная связь по скважности его выходного сигнала. Она дейдит в единичное состояние, на его и версном выходе - сигнал логического О.

В момент времени t по переходу

О

нарастающего напряжения на входе ус ройства через нуль напряжение на вы ходе компаратора 1 становится равны логической 1. Счетчик 3 останавли вается. Триггер 16 переходит в нуле вое состояние и разрешает счет счет чику 4. В некоторый момент времени коды на выходах счетчиков 3 и 4 становятся одинаковыми и узел 7 срав нения кодов вырабатывает импульс, к

ствует таким образом, чтобы поддержи- 5 торый переводит триггеры 16 и 18 в

вать на выходе компаратора 1 скважность сигнала, равной 2. Вместе с тем скважность выходного сигнала компаратора равна 2 только в том случае, когда напряжение смещения компаратора и постоянной .составляющей входного сигнала полностью скомпенсированы Эту компенсацию осуществляет отрицательная обратная связь по скважности

сигнала. Усилитель-ограничитель 2

/

преобразует выходной сигнал компаратора 1 так, что амплитуды положительных и от1 ицательных полуволн его выходного сигнала одинаковы. Интегратор 13, интегрируя зтот сигнал, изме няет свое напряжение таким образом, чтобы скомпенсировать постоянную составляющую входного сигнала и напряжение смещения компаратора 1. Фильтр

20

25

-30

единичное и нулевое состояния соответственно, счетчики 3 и 4 обнуляются. Одновременно через формирователь импульсов на элементах И-НЕ 21 и 20 проходит импульс, уменьшающий код на выходе реверсивного счетчика 22. Дешифратор 23 дешифрирует этот код и увеличивает коэффициент деления управляемого делителя 11 частоты. Час тота сигнала, поступающего на входы счетчиков 3 и 4, уменьшается. Процесс повторяется до тех пор, пока счетчик 3 прекратит входить в переполнение .

При недогрузке счетчика 3 происходит аналогичный процесс. При этом анализируется старший разряд его кода элементом И-НЕ 19: если он равен нулю, то сигналы узла 7 сравнения

14.низких частот служит для подавле- .35 кодов, проходя через элемент 19, так

18 и 16 находятся в нулевом и еди- ного сигнала производится следуюш:им

.ния пульсаций выходного сигнала интегратора 13.

Таким образом производится формирование выходного сигнала компаратора 1.

Установка частоты, поступающей на счетчики 3 и 4, производится следующим образом. Перед циклом измерения счетчики 3 и 4 обнулены, триггеры

ничном состояниях соответственно, сигнал на выходе узла 7 сравнения кодов равен нулю. Частота на входах счетчика 3 такова, что при измерении счетчик 3 входит в переполнение.

В момент времени t по переходу спадающего входного напряжения через нуль компаратор 1 вырабатывает на своем выходе сигнал логического О, который проходит через инвертор 15 и запускает счетчик 3. В некоторый момент времени t происходит переполнение счетчика 3, триггер 18 перехо40

изменяют состояние счетчика 22, дешифратора 23, управляемого делителя 11 частоты, чтобы старший разряд счетчика 3 в конце счета при перепаде нарастающего входного напряжения через нуль был равен логической 1.

Таким образом производится установка тактовой частоты.

Процесс измерения амплиГтуды вход50

55

образом. Предположим, что схемы формирования выходного сигнала компаратора и тактовой частоты работают в установившемся режиме, входной сигнал не имеет.постоянной составляющей В начальном состоянии счетчики 3 и 4 обнулены, триггер 16 - в единичном состоянии.

В момент времеш t по переходу спадающего входного напряжения через нуль компаратор 1 вырабатывает на своем выходе сигнал логического О, счетчик 3 запускается и подсчитывает

дит в единичное состояние, на его инверсном выходе - сигнал логического О.

В момент времени t по переходу

О

нарастающего напряжения на входе устройства через нуль напряжение на выходе компаратора 1 становится равным логической 1. Счетчик 3 останавливается. Триггер 16 переходит в нулевое состояние и разрешает счет счетчику 4. В некоторый момент времени коды на выходах счетчиков 3 и 4 становятся одинаковыми и узел 7 сравнения кодов вырабатывает импульс, который переводит триггеры 16 и 18 в

20

25

30

единичное и нулевое состояния соответственно, счетчики 3 и 4 обнуляются. Одновременно через формирователь импульсов на элементах И-НЕ 21 и 20 проходит импульс, уменьшающий код на выходе реверсивного счетчика 22. Дешифратор 23 дешифрирует этот код и увеличивает коэффициент деления управляемого делителя 11 частоты. Час тота сигнала, поступающего на входы счетчиков 3 и 4, уменьшается. Процесс повторяется до тех пор, пока счетчик 3 прекратит входить в переполнение .

При недогрузке счетчика 3 происходит аналогичный процесс. При этом анализируется старший разряд его кода элементом И-НЕ 19: если он равен нулю, то сигналы узла 7 сравнения

ного сигнала производится следуюш:им

изменяют состояние счетчика 22, дешифратора 23, управляемого делителя 11 частоты, чтобы старший разряд счетчика 3 в конце счета при перепаде нарастающего входного напряжения через нуль был равен логической 1.

Таким образом производится установка тактовой частоты.

Процесс измерения амплиГтуды вход0

5

образом. Предположим, что схемы формирования выходного сигнала компаратора и тактовой частоты работают в установившемся режиме, входной сигнал не имеет.постоянной составляющей. В начальном состоянии счетчики 3 и 4 обнулены, триггер 16 - в единичном состоянии.

В момент времеш t по переходу . спадающего входного напряжения через нуль компаратор 1 вырабатывает на своем выходе сигнал логического О, счетчик 3 запускается и подсчитывает

импульсы, приходящие с управляемого делителя I1 частоты.

В момент времени t при переходе

О

нарастающего входного напряжения через нуль на выходе компаратора 1 появляется сигнал логической IV Счетчик 3 останавливается, на его выходах - код, соответствующий половине периода входного сигнала. Одновременно триггер 16 изменяет свое состояние и счетчик 4 начинает подсчитывать импульсы, приходящие с выхода удвоителя 6 частоты.

В момент времени t, коды на выходах, счетчиков 3 и 4 сравняются и узел 7 сравнения кодов вырабатывает импульс, который обнуляет счетчики 3 и 4, переводит триггер 16 в единичное состояние, запрещающее счет счетчику 4. Одновременно по этому импульсу, точно соответствующему моменту времени, когда входной сигнал нахо- дится в экстремуме, квантователем 8 производится кватование этого сигнала. Схема готова к очередному измерению, которое начинается в момент времени t g.

Аналогично прои зводятся измерения при наличии постоянной составляющей во входном сигнале и изменении его параметров.

Измерение производится не раз в два периода, а в каждый период входного сигнала. При этом быстродействие увеличивается в два раза.

Предлагаемое устройство обладает большей точностью, помехозащищенностью и большим быстродействием, позволяет автоматизировать процесс измерения и производить измерения при непре 1,гено меняющихся параметрах измеряемого сигнала.

Формула изобретения

1. Устройство для измерения амплитуды синусоидального сигнала, содержащее распределитель импульсов, пер- вьй и второй счетчики импульсов, генератор импульсов, удвоитель частоты узел сравнения кодов, квантователь, источник опорного напряжения и компаратор, один вход которого подключен к входу квантователя и входной шине, другой - к выходу источника опорного напряжения, а выход - к первому входу распределителя импульсов, первый и второй выходы которого подключены

0

5

0

5

0

5

0

5

к входам первого и второго счетчиков импульсов соответственно, другие входы которых соединены соответственно с входом и выходом удвоителя частоты, а выходы - с входами узла сравнения кодов, выход которого соединен с вторым входом квантователя, выход которого соединен с выходной шиной устройства, отличающееся тем, что, с целью повышения точности измерений, быстродействия и помехозащищенности, в него введены блок управления делителем и управляемый делитель частоты, выход которого подключен к входу удвоителя частоты, а входы - к выходу генератора импульсов и выходу блока управления делителем, первый и второй входы которого соединены с выходами первого счетчика импульсов и узла сравнения кодов, выход которого соединен с входами обнуления первого и второго счетчиков импульсов и вторым входом распределителя импульсов, выход компаратора соединен с входом источника опорного напряжения.

2.Устройство по п.1, о т л и - чающееся тем, что распределитель импульсов содержит триггер и инвертор, вход и выход которого соединен с первыми входом и выходом распределителя импульсов, соответственно, первый, второй и третий входы триггера соединены с общей шиной, первым и вторым входами распределителя импульсов, а выход - с вторым выходом распределителя импульсов.

3.Устройство по п.1, о т л и - чающееся тем, что источник опорного напряжения содержит последовательно соединенные усилитель-ог-г раничитель, интегратор, фильтр низких частот, выход которого соединен

с выходом источника опорного напряжения, вход которого соединен с входом усилителя-ограничителя.

4.Устройство по п.1, о т л и - чающееся тем, что блок управления делителем содержит триггер, первый, второй и третий элементы И- НЕ, реверсивный счетчик импульсов, дешифратор и второй инвертор, выходом подключенный к второму входу триггера и первому входу первого элемента И-НЕ, а входом - к первому входу блока управления делителем, один вход второго элемента И-НЕ соединен с выходом триггера и вторым

713

входом первого элемента И-НЕ, другой вход - с третьим входом первого эле мента И-НЕ, выходом третьего элемента И-НЕ и вычитающим входом реверсивного счетчика импульсов, а выход - с входом третьего элемента И-НЕ, дру- ,гой вход которого соединен с третьим входом триггера, вторым входом блока

t, it ,и ts tf t, tt

VU9,Z

Редактор H.Тупица

Составитель А.Морозов Техред И.Попович

Заказ 1213/44Тираж 731 Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

управления делителем и четвертым входом первого элемента И-НЕ, выход которого соединен с суммирующим входом реверсивного счетчика импульсов, выход которого череэ дешифратор соединен с выходом блока управления делителем, первый вход триггера подключен к шине логической 1.

Корректор Н.Король

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения амплитуды переменного напряжения | 1985 |

|

SU1272261A1 |

| Устройство для измерения амплитуды синусоидального напряжения | 1985 |

|

SU1272262A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Устройство управления | 1984 |

|

SU1229721A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Устройство для измерения амплитуды синусоидального напряжения | 1982 |

|

SU1045142A1 |

| МНОГОКАНАЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2177637C2 |

| Цифровой фазометр | 1982 |

|

SU1061062A1 |

| Устройство для автоматического измерения амплитуды переменного сигнала | 1977 |

|

SU711482A1 |

| Устройство автоматической подстройки частоты | 1987 |

|

SU1539999A2 |

Изобретение относится к измерительной технике и может быть использовано для измерения амплитуды синусоидального напряжения, имеющего постоянную составляющую. Цель изобретения - повьшение точности измерения, быстродействия и помехозащищенности достигается путем оптимизации режима работы компаратора и автоматического J применения тактовой частоты при изменяющихся параметрах входного сигнала. Для этого в устройство введены блок 10 управления делителем и управляемый делитель 11 частоты. Кроме того, устройство содержит компаратор 1, распределитель 2 импульсов, счетчики 3 и 4 импульсов, генератор 5 импульсов, удвоитель 6 частоты, узел 7 сравнения кодов, квантователь 8, источник 9 опорного напряжения, содержащий усилитель-ограничитель 12, интегратор 13, фильтр 14 низких частот. В состав распределителя 2 входят инвертор 15 и триггер 16. Блок 10 содержит инвертор 17, триггер 18, элементы И-НЕ 19, 20 и 21, реверсивной счетчик 22 импульсов и дешифратор 23. 3 з.п. ф-лы, 2 ил. SS сл со о ю ГчЭ О со Фиг.1

| Устройство для измерения амплитуды синусоидального напряжения | 1982 |

|

SU1045142A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-04-07—Публикация

1985-03-20—Подача