1

Предлагаемое устройство относится к области автоматики и вычислительной те.хники и иредназначеыо для проверки иреобразователей угол-код.

Иифор.мационпая способность является обобщающим параметром, характеризующим качество преобразователей угол-код. Однако ее определение ведется, как правило, вручную, т. е. производится большое число измерений ошибок преобразователя, а также трудоемкий расчет.

Известны устройства для автоматической проверки преобразователей угол-код, содержашие генератор стабильной частоты, привод равномерной скорости, делитель частоты, блоки реальных и эталонных сигналов, усилительформирователь сигналов опроса, дешифратор, пороговые устройства, преобразователь специальных кодов в натуральные и логические элементы. Оно решает задачу автоматического определения ошибки преобразования угла в код и лишь создает иредиосылки для возможного расчета информационной способности преобразователей.

Целью изобретения является определение информационной способности преобразователей угол-код, т. е. повышение эффективности контроля преобразователей угол-код.

Предлагаемое устройство позволяет почти полностью автоматизировать определепие количественного показателя информационной способности преобразователей угол-код, сведя весь расчет к нескольким арифметическим действиям.

Поставленная цель достигается тем, что в известное устройство введены счетчик оборотов, счетчик эталонного кода, блок сравнения кодов, регистр кода угла поворота, счетчик импульсов разпости кодов, линия задержки, элементы задерлчки, триггер и схемы «И, «МЛН и «Запрет. Выход делителя частоты соединен с первыми входами схемы «Запрет i первой схемы «П, вторые входы которых подключены к единичному выходу триггера. Выход схемы «Запрет соединен с первым ЗХО.ТОМ схемы «ПоЧП, выход первой схемы «1Ь - со входом формирователя эталонных сигналов, выход которого подключен через первый элемент задержкп ко входу счетчика эталонного кода, п через линию задержки с объединенными отводами - ко второму входу схемы «ИЛИ, выход которой соединен с усилителем-формирователем, и через второй элемент задержкп - ко входу блока сравнения кодов, к другим входам которого подключены выходы счетчика эталонного кода и регистра 1;ода угла поворота. Выход блока сравнения кодов соедп ен со входом счетчика импульсов разности кодов. Входы регистра кода угла поворота соединены с выходами вторых схем

«И, лервые входы которых иодключс: : к выходам ирсобразозатслк 11 едиалы;ых кодов в натуральные, вторые - к одиикчно/ у выходу триггера, единичны зход которого сосдннен с нулевыл выходом дешифратора, дулс;ю11 - с выходом третьей схемы «И, нервый вход которой подключен к единичнолау выходу дешифратора и входу счетчика оборотов, а второй вход - к выходу счетчика оборотов.

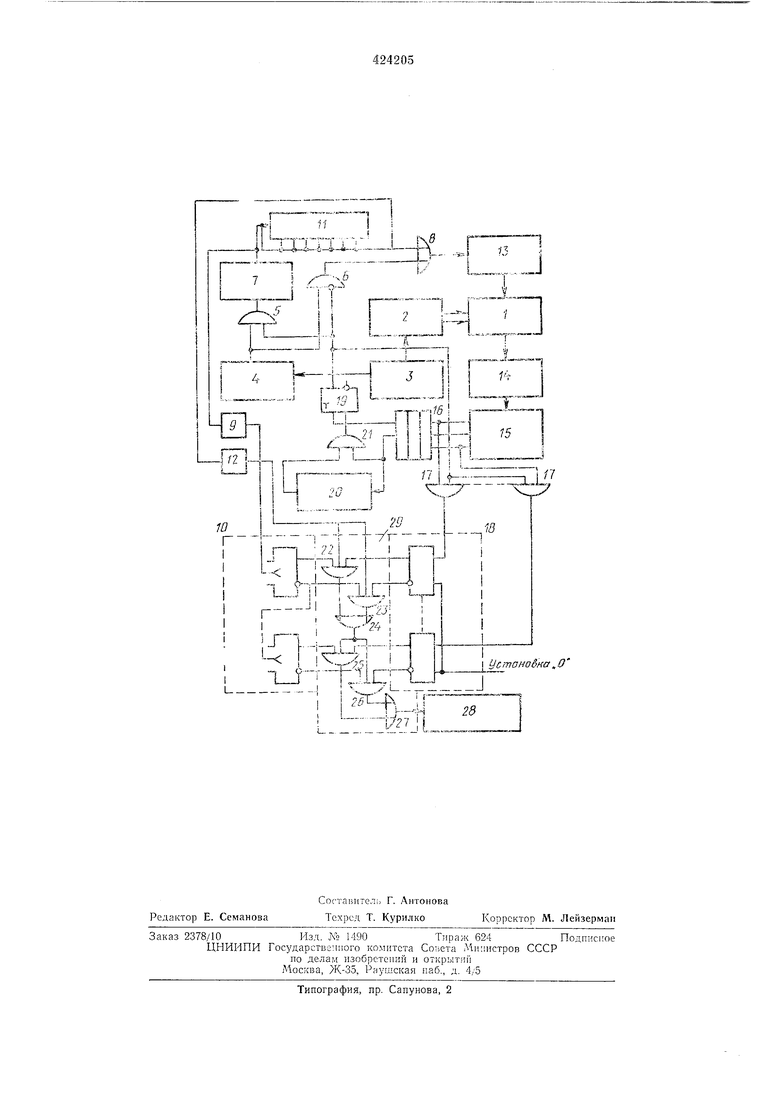

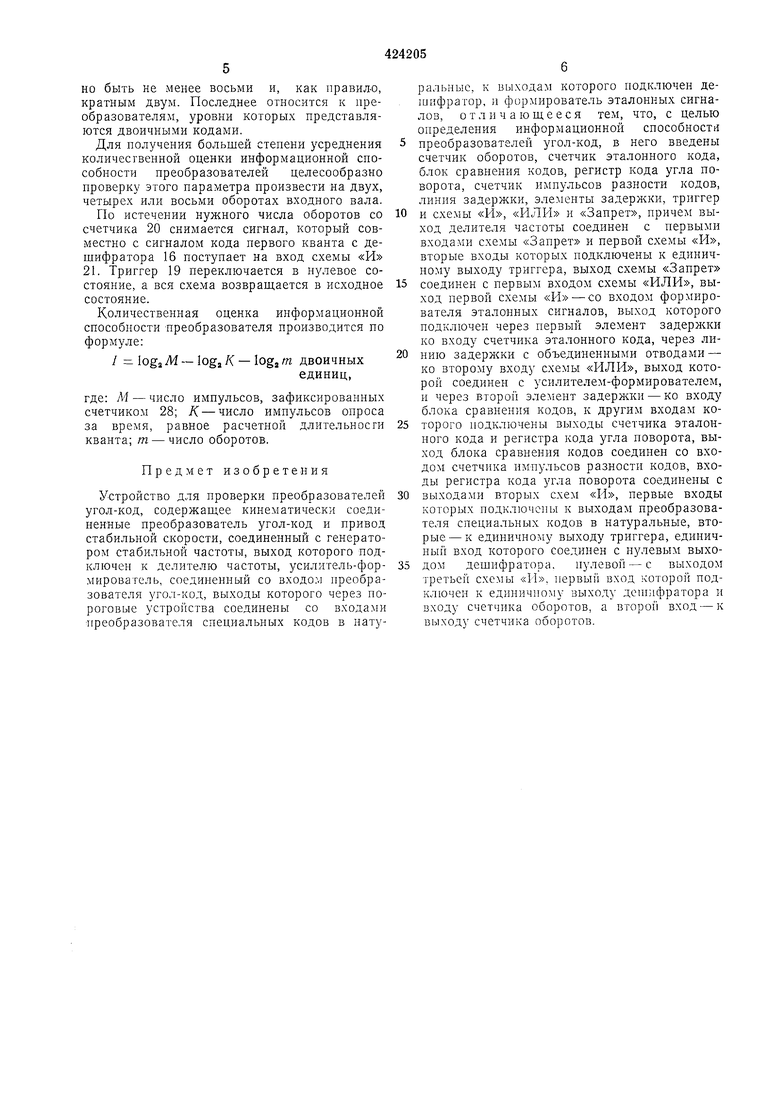

На чертеже нредставле11а фун}аи1ональная схема устройства.

ИспытываемьЙ нреобразовате,:ь у| ол-код 1 кинематически связан с нриводол; стабильной скорости 2, вход которого соединен с выходом генератора 3 стабильной частоты. Второй выход носледнего соединен со входом делителя

4частоты, выход которото соединен со входом схемы «И 5 н схемы «Занрет 6. Выход нерBoij из них иодключен ко входу фо1)мнрователя 7 эталонных сигналов, а второй-- ко входу схемы «ИЛИ 8.

Выход формирова1еля 7 соединен через нервый элеме1гг задержки 9 со входо.м счетчика 10 эталонного кода н со входом линии задержки И. Выход и отводы иоследией нодключены ко входу второго элемента задержки 12 и ко второму входу схемы «ИЛИ 8, выход которой соединен со входо: 1 уснлителяфор птрователя 13 сигналов онроса.

Выход нреобраоовагеля угол-код i через нороговые устр011С;ва 14 соединен со входом преобразователя 1Ь снедиальных ко;шв в натуральные, выходы которого соединены со входами дешифратора 16 и схем «И 17. Выходы носледних подключены ко входам регистра 18 кода угла поворота.

Выход кода нулевого кванта ден нфратора 16 соединен с едииичным входом триггера 19, а выход кода иервого кгзаи1а - со входом счетчика 20 оборотов н схемы «И 21, второй вход которой иодключеи к выходу счетчика 20. Выход схемы «И 21 соединен с нулевым входом триггера 19, еднннчиый выход которого соединен со вторым входом схемы «PI

5и заирешающим входом схемы «Занрет 6. Выход элемента задержки 12 соединен с

первыми входами схем «И 22 н 23, н т)етий входы нервой нз них соединены с едннлчными, а второй - с нулевыми выходами триггеров счетчика 10 и регистра 18.

Выходы схем «I-i 22 и 23 соединены со ВХОДОЛ1 схемы «PLlPi 24, выход которой нодключеи ко входам схемы «И 25 и 28, вторые и третьи входы которых нодключены вышеописанным сиособом к выходам триггеров счетчика 10 и регистра 18, а выходы---/:о входу схемы «ИЛИ 27. Выход последней соеднН(;н со входом счетчика 28 имиулвсов разности кодов. Схемы «И 22, «И 23, «ИЛИ 24, «И 25 и 26 н «ИЛИ 27 в совокупности образуют блок сравнения кодов 29.

стройство функционнрует следующим образом.

Испытываемый преобразователь угол-код 1 приводится в равно: герное вращение приводом 1;абил1ми)11 скорости 2, сннхроннзадия ; оторо о обеснечнвается генератором 3 стабильной частоты. До онределения нозндии нулевото кванта нреобразователя на време1п:ой оси опрос носледнего осунхествляется но нени: генерагор 3, делител.з 4 частоты, схема «Занрет 6, схема «ИЛИ 8 и усилитель-фор.мир1)ватель 13. при этом иа выходе преобразователя угол-код 1 ири иереходе входной угловой величины с одного его квантованного уровня на другой происходит смена кода, когорый фикснруетея, а зател; преобразуется в натуральный в преобразователе 15.

Ири ноявлении кода нулевого уровня на

выходе дешифратора 16 возинкает сигнал, но которому трнггер 1у перебрасывается в единичное состояние. При этом на схему «Занрет 6 поступает сигнал занрета, а схема «И 5 открываетея. ИоСоТедним достигается

начальная фазировка фор.мирователя 7 эталонных сигналов.

В формирователе 7 фор.мируется эталонный сигнал ciiCHbi кода иутем пересчета имнульсов стаби,чьной частоты, подаваел;ых на ето вход

с генератора 3 через делитель 4 за расчетный интервал времени. Этот сигнал поступает через эле.мент задержкн 9 на вход счетчика 10 н на вход лннин задержки 11. С носледней снимается серия нмиулосов, которыми через

ехе.му «ИЛИ 8 и усилитель-формирователь 13 опрап1ивается преобразователь угол-код 1 в расчетиые -моменты )зремени.

Но каждому онроеному импульсу снимается код, натуральное значение которого, сформярованное в преобразователе 15, через схе.мы «I-i 17, открытые но второму входу СИ1налом с едииичното выхода триггера 19, посгунает на регистр 10 кода угла поворота.

Одновременно онросные н.мпульсы с липни

задержки И через элемент задержки 12 ноетупа от на входы схем «И 22 и 23, управляемых ирямыми и инверсными выходами первых разрядов счетчика 10 н регистра 18. Если выходные сигналы с носледннх совнадают, то импульсы через схе.му «ИЛИ 24 поступают па вход схем «И следующего разряда, если эталонный и реальный коды совпадают, то импульсы поступают на счетчик 28. В случае идеального преобразователя, у

которого величина реального н расчетного );ванта одинакова, все нмнульсы, сформированные на выходе ли)1ии задержки 11, регистрируются счетчиком 28. В реальных преобразователях величина

Бсхшроизведеиного кванта является случайпой, поэтому положения границ смены кода колеблются в некоторых зонах, которые являются зонами неопределенности. В последних эталонный и реальные коды, как нравнло, не совпадают. Отсюда на счетчике 28 не учитываются те нмнульсы, которые нонадают в зоны несовпадений кодов.

Д.ЛЯ у-меньшення возможности пропуска зон неонределеиностей количество имиульсов

Г) серии за расчетный ингсрва,т времени .а;олжно быть не менее восьми и, как правило, кратным двум. Последнее относится к преобразователям, уровни которых представляются двоичными кодами.

Для получения большей степени усреднения количественной оценки информационной способности преобразователей целесообразно проверку этого параметра произвести на двух, четырех или восьми оборотах входного вала.

По истечении нужного числа оборотов со счетчика 20 снимается сигнал, который совместно с сигналом кода первого кванта с дешифратора 16 поступает на вход схемы «И 21. Триггер 19 переключается в нулевое состояние, а вся схема возвращается в исходное состояние.

Количественная оценка информационной способности преобразователя производится по формуле:

/ - logj М - logj /( - logj т двоичных

единиц,

где: М - число импульсов, зафиксированных счетчиком 28; К - число импульсов опроса за время, равное расчетной длительноеги кванта; т - число оборотов.

Предмет изобретения

Устройство для проверки преобразователей угол-код, содержаш,ее кинематически соединенные преобразователь угол-код и привод стабильной скорости, соединенный с генератором стабильной частоты, выход которого подключен к делителю частоты, усилитель-формирователь, соединенный со входом преобразователя угол-код, выходы которого через пороговые устройства соединены со входами преобразователя специальных кодов в натуральные, к выходам которого подключен дешифратор, и формирователь эталонных сигналов, отличающееся тем, что, с целью определения информационной способности

преобразователей угол-код, в него введены счетчик оборотов, счетчик эталонного кода, блок сравнения кодов, регистр кода угла поворота, счетчик импульсов разности кодов, линия задержки, элементы задержки, триггер

и схемы «И, «ИЛИ и «Запрет, причем выход делителя частоты соединен с первыми входами схемы «Запрет и первой схемы «И, вторые входы которых подключены к единичному выходу триггера, выход схемы «Запрет

соединен с первым входом схемы «ИЛИ, выход первой схемы «И - со входом формирователя эталонных сигналов, выход которого подключен через первый элемент задержки ко входу счетчика эталонного кода, через линию задерл ки с объединенными отводами - ко второму входу схемы «ИЛИ, выход которой соединен с усилителем-формирователем, и через второй элемент задержки - ко входз блока сравнения кодов, к другим входам которого подключены выходы счетчика эталонного кода и регистра кода угла поворота, выход блока сравнения кодов соединен со входом счетчика импульсов разности кодов, входы регистра кода угла поворота соединены с

выходами вторых схем «И, первые входы которых подключены к выходам преобразователя специальных кодов в натуральные, вторые- к единичному выходу триггера, единичный вход которого соединен с нулевым выходом дешифратора. пулевой - с выходом третьей схемы «И, первый вход которой подключен к единичному выходу деп ифратора и входу счетчика оборотов, а второй вход - к выходу счетчика оборотов.

rfiПI

11

L-.-f....-.-. J

,.4-i-L-

г

,±LLJ LJI

.t , .J

Si -.-.

i j- r t::iu;

1-г::::р1 11

Uci-поноёна ,0

„,;iu j

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения погрешности преобразователя угла поворота вала в код | 1985 |

|

SU1295516A1 |

| Устройство для автоматической проверки преобразователя угла поворота вала в код | 1985 |

|

SU1279063A1 |

| Устройство для контроля преобразователей угла поворота вала в код | 1981 |

|

SU970429A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1388989A2 |

| Устройство для проверки преобразователей "угол-код | 1978 |

|

SU934527A1 |

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Устройство для определения погрешностей преобразователя угла поворота вала в код | 1987 |

|

SU1464288A1 |

| УСТРОЙСТВО КОНТРОЛЯ ТОЧНОСТИ ЦИФРОВЫХ ПРЕОБРАЗОВАТЕЛЕЙ УГЛА | 2015 |

|

RU2577186C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ СЕРИИ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1968 |

|

SU208038A1 |

| Устройство формирования и регистрации путевых параметров для управления шахтной подъемной установкой | 1989 |

|

SU1835383A1 |

Даты

1974-04-15—Публикация

1971-10-07—Подача