1

Предлагаемое изобретение относится к области вычислительной техники, в частности к запоминающим устройствам, и может найти применение в технических средствах автоматизированных систем управления производством.

Известны запоминающие устройства, содержащее накопитель с контрольными разрядами, соединенный с выходами формирователей адресных токов, резистор, регистр записи, индикаторы записи нечетности и выдачи нечетности, усилитель контрольного разряда, формирователь тока контрольного разряда и логический элемент «эквивалентность.

Целью настоящего изобретения является упрощение и иовыщение надежности запоминающего устройства.

Поставленная цель достигается тем, что в запоминающем устройстве выходы первого, второго, третьего и четвертого разрядов регистра записи соответствующими проводами разрядной записи, проходящими соответственно через отверстия опроса третьего, четвертого, нервого и второго разряда индикатора заииси нечетности и проходящие встречно через отверстия записи первого, второго, третьего и четвертого разряда индикатора записи нечетности, соединены с соответствующими входами накопителя, выходы первого, второго, третьего и четвертого разряда накопителя

проводами выдачи разрядов, проходящими через одноимсниые отверстия опроса индикатора выдачи нечетности и через отверстия заииси третьего, четвертого, первого и второго разряда индикатора выдачи нечетности, соединены с общим резистором, подключенным другим своим концом к источнику напряжения, провод подготовки цроходит через отверстия записи индикаторов заниси нечетности и

выдачи нечетности согласно, ировода считывания индикаторов записи нечетности и выдачи нечетности соединены со входами одноименных усилителей, выход усилителя записи нечетности соединен через формирователь тока контрольного разряда с шиной разрядной записи контрольного разряда, выход усилителя выдачи нечетности соединен с первым выходом логического элемента «эквивалентность, второй вход которого соединен с выходом усилителя контрольного разряда.

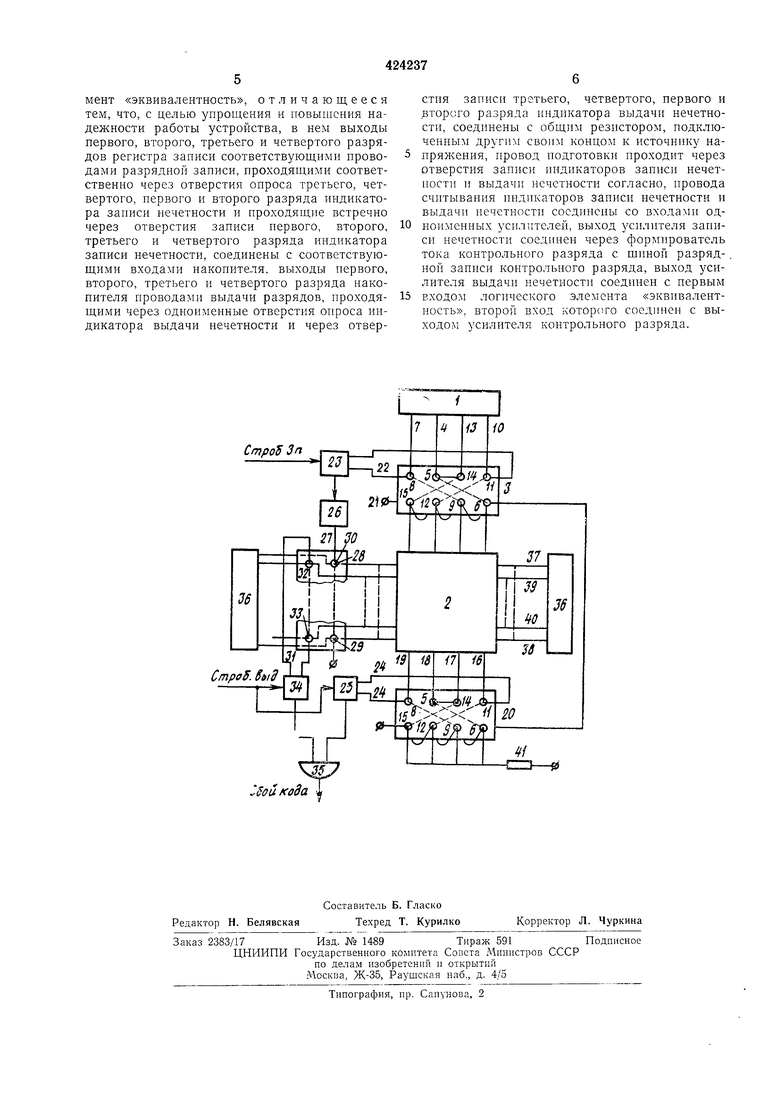

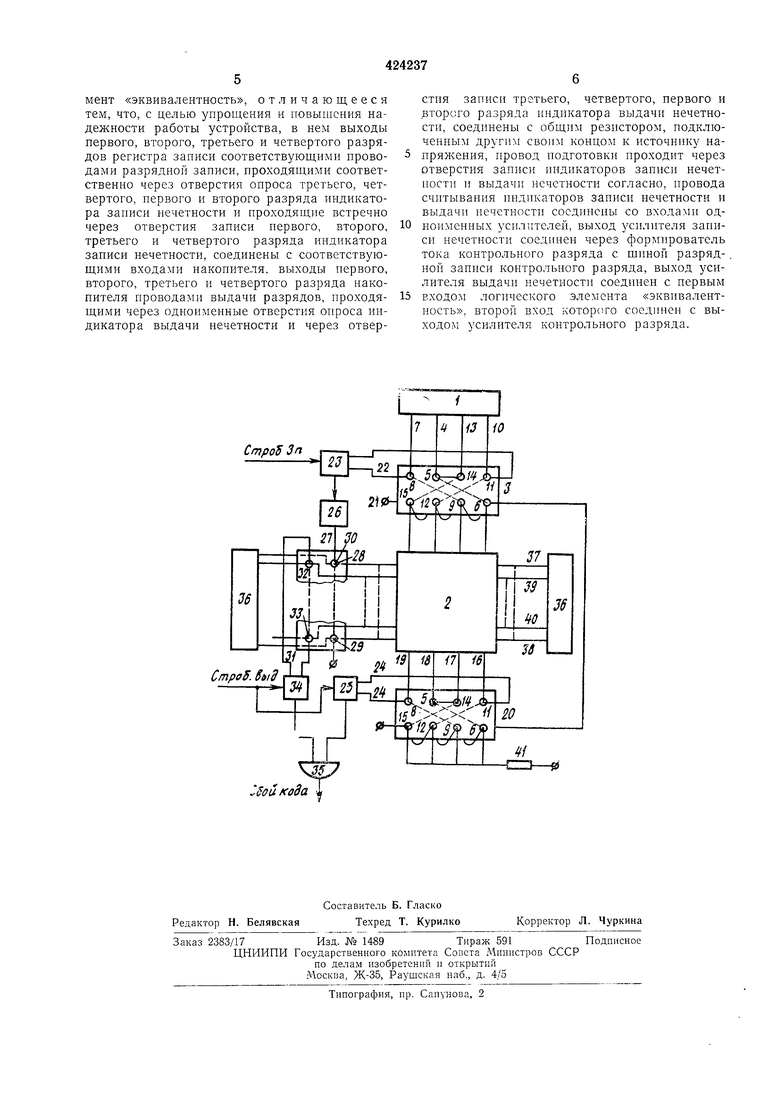

На чертеже представлена схема запоминающего устройства, содержащая регистр записи 1, накопитель 2, индикатор 3 записи иечетностн, провод 4 первого разряда заннси, отверстие 5 опроса третьего разряда, отверстие 6 записи первого разряда, провод 7 второго разряда записи, отверстие 8 опроса четвертого разряда, отверстие 9 записи второго разряда, провод 10 третьего разряда записи, отверстие 11 опроса иервого разряда, отверстие

12 записи третьего разряда, проиод 13 четвертого разряда записи, отверстие 14 опросе второго разряда, отверстие 15 записи четузертого разряда, провод 16 выдачи первого разряда, провод 17 выдачи второго разр5:да, провод 1о выдачи разряда, провод ; г.ыдачи четвертого разряда, ипдикатор 20 выдачи печетиостп, провод 21 подготовки, провод 22 считывания индикатора заииси исчетпости, двухполярпви усид1ггель 23 иидикатора заииси аечетности, провод 24 считывания пидикатора выдачи нечетности, двухиоляриви усилитсл) 25 иидикатора выдачи нечетности, формирователь тока коитролвиого разряда 25, гиипа 27 разрядной заииси коитролвиого разряда, отверстие 28 заипси контрольного разряда первого слова, отверстие 29 записи контрольного разряда «я-го слова, коитрол1 ив1Й разряд 30, провод 31 считывания контрольного разряда, отверстие 32 опроса контрольного разряда первого слова, отверстие 33 оироса коитрольиого разряда ««-го слова, усилитель 34 коитрольного разряда, логический элемент «эквивалентность 35, формирователи адресиых токов 36, шииа 37 числовой заииси иервого слова, ишна 38 числовой «/х-го слова, HJJIна 39 опроса первого слова, гиина 40 опроса «п-го слова, резистор 41.

На чертеже юображеио запомииаюитее устройство емкостью «п слов но четыре двоичных разряда каждое. Регистр заииси 1 соединен с иакоиителем 2 через индикатор 3 заииси печетиости так, что ировод 4 иервого разряда заииси ироиизан через отверстие 5 оироса третвего разряда п прогиит встречно через отверстие 6 заииси иервого разряда индикатора заииси иечстиости. Провод 7 второго разряда заииси ироиизаи через отверстие 8 оироса четвертого разряда иидикатора 3 и ирошит р.стречио через отверст ю 9 записи второго разряда этого индикатора. Провод К) третьего разряда записи ирошнт встречно через отверстие 11 (лфоса иервого разряда и отверстие 12 заииеи третьего разряда, а провод 13 четвертого разряда заииси ирони т встречно -.срез OTBCpcTiie 14 оироса второго разряда и отверстие 15 записи четвертого разряда иидикатора заинеи нечетиоети. Иакоиитель еоединеи проводами 16, 17, 18. 19 выдачи иервого, второго, третьего и четвертого разрядов соотг.етственно с иид1и :атором 20 выдачи иечетиост;так, что каждьи из них иронизан через отверстия 11, 14, 5 и 8 оироса одноименного разряда иидикатора выдачи иечстиости и каждый ло отдельности ирошит встреч ю через o iBepстия 12, 15, 6 и 9 записи третьего, четвертого, иервого н второго разрядов еоответствеиио этого индикатора, по ввьходе провода выдачи разрядов объединены н подключены к резистору 41, Провод подготовки 21 ироп1ит согласио через отверстия записи иидикатора заииси нечетности и индикатора выдачи нечетности. Провод 22 считывания г идикатора записи нечетности ирошнт встречно через отВ| РСТНЯ оироса этого индикатора и соединен

со входо. двухиолярного усилителя 23 сигнала иидикатора заииси нечетности, а ировод 24 считывания индикатора выдачи нечетности npoHuiT встречио че)ез остверстия оироса одиои генного иидикатора к соединен со входом двухиолярного усилителя 25 индикатора выдачи нечетиоети. Двухнолярный yci-иЛйтель запнеи иечетностн соединен с формирозате.ле:, 26 TOK;i контрольного разряда, выход которого еоедниеи с шииой 27 разрядной заиисн контрольного разряда. Шина разрядной записи коитрольиого разряда прошита встречно через отверетпе 28 заииси контрольного разряда иервого елова п отверстие 29 заииси контрольного разряда я-го слова контрольного разряда 30. Провод 31 считывания контрольного разряда нрошит встречно через отверстие 32 оироса контрольного разряда первого слова и отверстие 33 заинеи контрольного разряда

д-го слова н соединен со входом усилителя 34 контрольного разряда. Выходы двухполярного усилителя индикатора выдачи нечетности и усилителя контрольного разряда соединены с входами логического элемента «эквивалентность 35. Формирователи адресных тохов 36 вк.лючеиы по токовым схемам «И, нзгрузкаД1и которых являются области намагниченности вокруг отверстий записи 28, 9, отверстий ojipoca 32, 33 контрольного разряда и заиоминающие элемеиты накоиителя. Подключение формирователей адрееных токов к нагрузкам осуиюствляется нри иомош,и шин числовой заниси первого елова 37 и п-го слова 38, а т-акже пптн опроса первого слова 39 и п-го слов а 40.

Прсдлагас-мое запоминающее з/стройство работает в дв;-х основных режимэх - «Запиеь п «Выдач;;. Кроме функции обычной записи .4 Bb,:;, гп1фор:лации, настояндее запоминаюiii.ec yeTpofiCTBo выполняет функцию оперативгюго контроля достоверности информации, В режиме «Заиис, кроме записи информации 15 иакопитель i:o выбранному слову, сиределястся чст; ост-ь или нечеткость записываемой

ппформатип ч производится занист: четкой или печеткол ичформации в контрольный разряд данного слова. В режиме «Выдача выдается выбранная 1шформап,ия, спред-гляется ее четкость пли исчет1 ость и определяется эквивалгчп-цост;; записанной к выданной информац1П. Четкость иечеткость записываемой ппформа1;,1П1 о;:ределяется индикатором записи нечетное : ;, а четность или нечетность -вылавасгюй гнсрормацин -- индикатором в-ыдачи

печетпости, которые выполняют суммиро-ваппе по модулю два.

П р е д м е т н з о б р е т е н и я

Запо.мип;иом:ое устройство, содержатдее наьопитель с ко117рольБыми разрядами, соедииеппы:; с 1;;,:;.();;амп формирователей адресных

токов. |.). регистр записи, нндлкаторы

печетпости и 15ыдачи нечетности, уси;пггель Koirrpo/iinioro разряда, формирователь

тока контрильиого разряда и логический элемент «эквивалентность, отличающееся тем, что, с целью упрощения и повышения надежности работы устройства, в нем выходы первого, второго, третьего и четвертого разрядов регистра записи соответствующими проводами разрядной записи, проходящими соответственно через отверстия опроса третьего, четвертого, первого и второго разряда индикатора записи нечетности и проходящие встречно через отверстия записи первого, второго, третьего и четвертого разряда индикатора записи нечетности, соединены с соответствующими входами накопителя, выходы первого, второго, третьего и четвертого разряда накопителя проводами выдачи разрядов, проходящими через одноименные отверстия опроса иидикатора выдачи нечетности и через отверстия записи третьего, четвертого, первого и второго разряда индикатора выдачи нечетности, соединены с общим резистором, подключенным другим своим концом к источнику напряжения, провод подготовки проходит через отверстия записи индикаторов записи нечетпости и выдачи нечетности согласно, провода считывания пндикаторов записи нечетности и выдачи нечетности соединены со входами одпоименных усилителей, выход усилителя записи нечетности соединен через формирователь тока контрольного разряда с шиной разрядной записи контрольного разряда, выход усилителя выдачи нечетности соединен с первым

входом логического элемента «эквивалентность, второй вход которого соед1И1еп с выходом усилителя контрольного разряда.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU347797A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1969 |

|

SU236863A1 |

| Ассоциативное запоминающее устройство | 1976 |

|

SU731474A1 |

| Телевизионное устройство для просмотра информации | 1974 |

|

SU595876A1 |

| ФОРМИРОВАТЕЛЬ КОДА МОРЗЕ | 1972 |

|

SU331498A1 |

| Счетчик импульсов | 1981 |

|

SU978358A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Логическое запоминающее устройство | 1986 |

|

SU1316047A1 |

| Устройство для магнитной записи измерительной информации | 1990 |

|

SU1727164A1 |

| Счетчик импульсов | 1983 |

|

SU1112576A1 |

CmpoS Зп

So и кода ,

Даты

1974-04-15—Публикация

1971-05-31—Подача