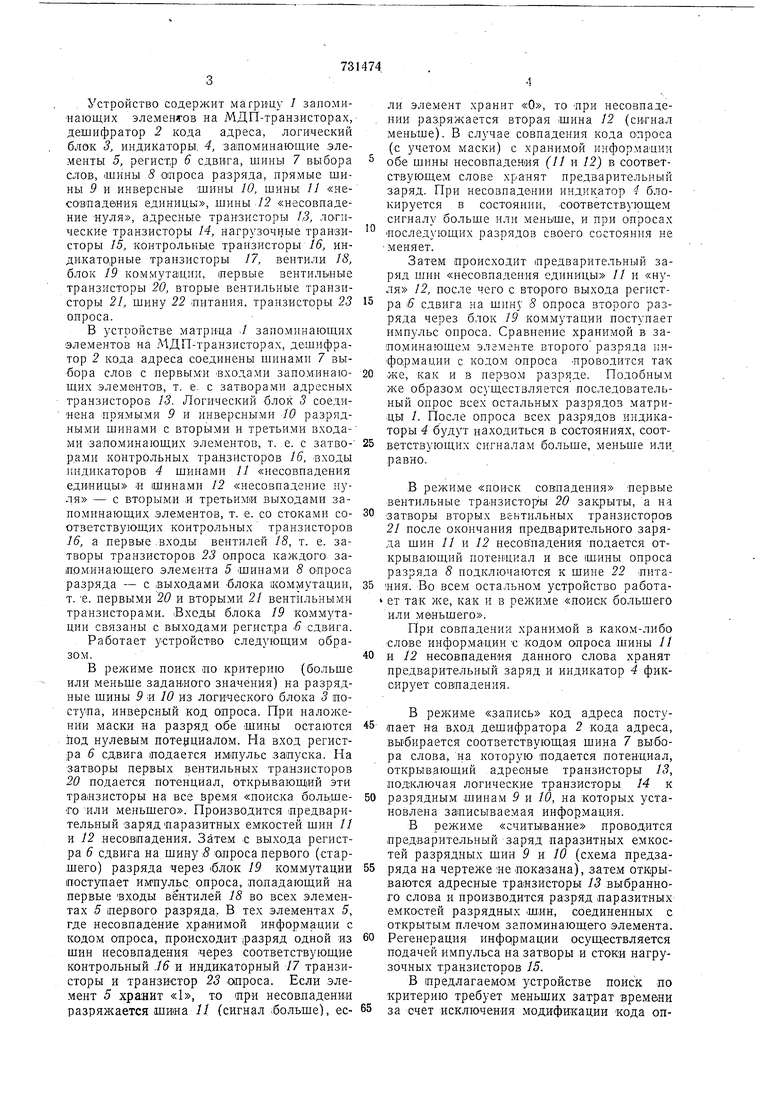

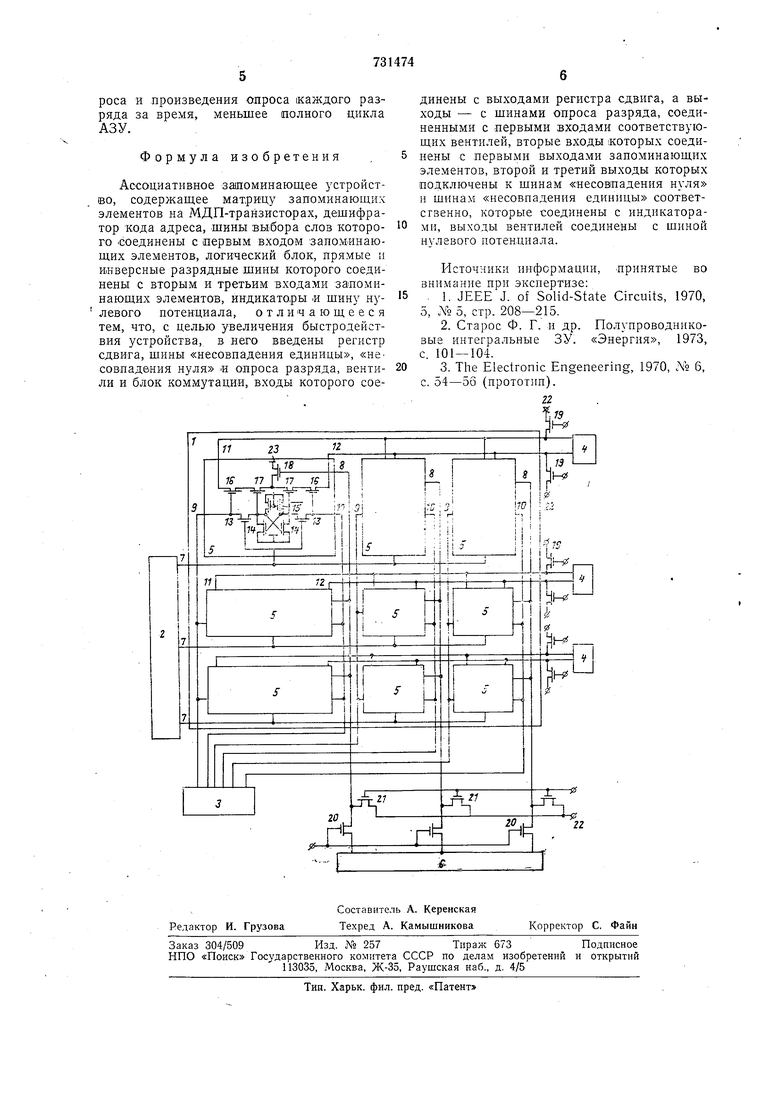

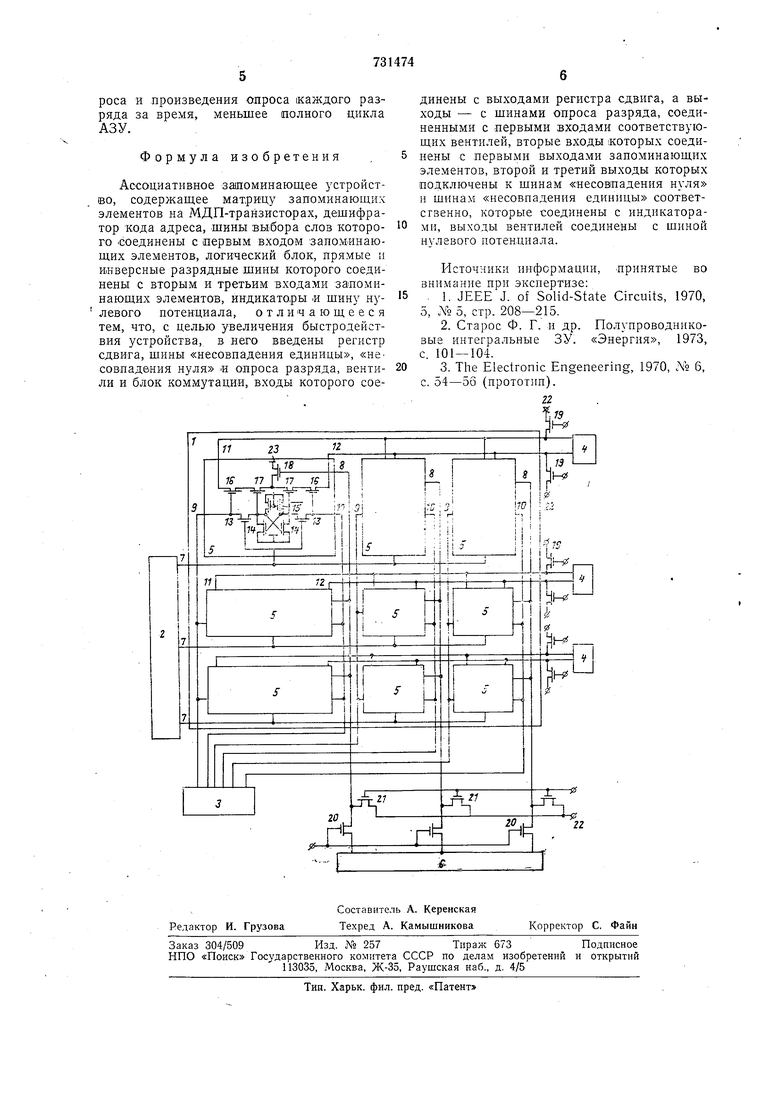

Устройство содержит матрицу / запоминающих элементов на МДП-транзисторах, дешифратор 2 кода адреса, логический блок 8, индикаторы. 4, запоминающие элементы 5, регист.р 6 сдвига, шины 7 выбора слов, шины 8 опроса разряда, нрямые шины 9 и инверсные шины 10, шины 11 «несовпадения единицы, шины /2 «несовпадение нуля, адресные транзисторы 1,3, логические транзисторы 14, нагрузочные транзисторы 15, контрольны.е транзисторы /, индикаторные транзисторы 17, вентили 18, блок 19 коммутации, первые вентильные транзисторы 20, вторые вентильные транзисторы 21, шину 22 питания, транзисторы 23 опроса.

В устройстве матрица ./ заноминаюших элементов на МДП-транзисторах, дешифратор 2 кода адреса соединены шинами 7 выбора слов с первыми входами запомпнаюших элементов, т. е. с затворами адресных транзисторов 13. Логический блок 3 соединена прямыми 9 и инверсными 10 разрядными шинами с вторыми и третьими входами запоминающих элементов, т. е. с затворами контрольных транзисторов 16, входы индикаторов 4 шинами // «несовпадения единицы и шинами 12 «несовиадение нуля - с вторыми и третьими выходами запоминающих элементов, т. е. со стоками соответствующих контрольных транзисторов 16, а иервые .входы веитилей /8, т. е. затворы транзисторов 23 оироса каждого за1по1минающего элемента 5 шинами 8 опроса разряда - с .выходами блока коммутации, т. -е. первыми 20 и вторыми 21 вентильными транзисторами. Входы блока 19 коммутации связаны с выходами регистра & сдвига.

Работает устройство следующим образом.

В иоиск по критерию (больще или меньще заданного значения) на разрядные щины 9 и 10 из логического блока 3 поступа, инверсный код опроса. При иаложении маски на разряд обе шины остаются под нулевым потенциалом. На вход регистра 6 сдвига подается импульс запуска. На затворы первых вентильных транзисторов 20 подается потенциал, открывающий эти транзисторы на все время «поиска большего или меньщего. Производится предварительный заряд паразитных емкостей щин // и 12 несовпадения. Затем € выхода регистра 6 сдвига на шину .8 опроса первого (старшего) разряда через блок 19 коммутации поступает им-пульс опроса, попадающий на первые ВХОДЫ вентилей 18 во всех элементах 5 первого разряда. В тех элементах 5, где несовпадение хранимой информации с кодом опроса, происходит |разряд одной из шин несовпадения через соответствующие контрольный .16 и индикаторный 17 транзисторы и транзистор 23 опроса. Если элемент 5 хранит «1, то 1при несовпадении разряжается шина Л (сигнал .больше), если элемент хранит «О, то при несовпадеНИИ разряжается вторая шина 12 (сигнал меньше). В случае совпадения кода опроса (с учетом маски) с хранимой информации обе шины несовпадения (// и 12) в соответствующем слове хранят предварительный заряд. При несовпадении индикатор 4 блокируется в состоянии, .соответствуюшем сигналу больше или меньше, и при опросах последующих разрядов своего состояния не меняет.

Затем происходит предварительный заряд шин «песовпаде шя единицы // и «нуля 12, после чего с второго выхода регистра 6 сдвига на шину 8 опроса второго разряда через блок 19 коммутации поступает импульс опроса. Сравпение хранидюй в запоминающем элементе второго разряда информации с кодом опроса проводится так

же, как и в первом разряде. Подобным же образом осуществляется последовательный опрос всех остальных разрядов матриды 1. После опроса всех разрядов индикаторы 4 будут иаходиться в состояниях, соответствующих сигналам больше, меньше или равно.

В режиме «поиск совпадения первые вентильные транзисторы 20 закрыты, а на

затворы вторых вентильных транзисторов 2/ после окончания предварительного заряда шин 11 и 12 несовпадения подается открывающий потенциал и все шины опроса разряда 8 подключаются к шине 22 питаиия. Во всем остальном устройство работает так же, как и в режиме «поиск большего или меньшего.

При совпадении хранимой в каком-либо слове информации -с кодом опроса шины 11

и 12 несовпадения данного слова хранят предварительный заряд и индикатор 4 фиксирует совпадения.

В режиме «запись код адреса поступает на вход дешифратора 2 кода адреса, вьгбирается соответствующая шина 7 выбора слова, на которую подается потенциал, открывающий адресные транзисторы 13, подключая логические транзисторы 14 к

разрядным шинам 9 и 10, на которых установлена записываемая информация.

В режиме «считывание проводится предварительный заряд паразитных емкостей разрядных шин 9 и 10 (схема предзаряда на чертеже не показана), .затем отк;рываются а.дресные транзисторы 13 выбранного слова и производится разряд паразитных емкостей разрядных шнн, соединенных с открытым плечом запоминающего элемента.

Регенерация информации осуществляется подачей импульса на затворы и стоки нагрузочных транзисторов 15.

В предлагаемом устройстве поиск по критерию требует меньших затрат времени

за счет исключения модификации кода опроса и произведения опроса каждого разряда за время, меньшее полного цикла АЗУ.

Формула изобретения

Ассоциативное запоминающее устройст1во, содержащее матрицу запоминающих элементов на МДП-транзисторах, дешифратор кода адреса, шины выбора слов которого .соединены с первым входом запоминающих элементов, логический блок, прямые н ннверсные разрядные шины которого соединены с вторым и третьим входами запоминающих элементов, индикаторы .и шину нулевого потенциала, отличающееся тем, что, с целью увеличения быстродействия устройства, в него введены регистр сдвига, шины «несовпадения единицы, «несовладения нуля и опроса разряда, вентили и блок коммутации, входы которого соединены с выходами регистра сдвига, а выходы - с шинами опроса разряда, соединенными с первыми входами соответствующих вентилей, вторые входы которых соединены с первыми выходами запоминающих элементов, второй и третий выходы которых подключены к шинам «несовпадения нуля и шинам «несовпадения единицы соответственно, которые соединены с индикаторами, выходы вентилей соединены с шиной нулевого потенциала.

Источники информации, принятые во внимание при экспертизе:

1.JEEE J. of Solid-state Circuits, 1970, 5, .YO 5, стр. 208-215.

2.Старое Ф. Г. и др. Полупроводниковые интегральные ЗУ. «Энергия, 1973, с. 101 - 104.

3.The Electronic Engeneering, 1970, Л 6, с. 54-56 (прототип).

22

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| АССОЦИАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО НА МДП-ТРАНЗИСТОРАХ | 1973 |

|

SU408374A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Устройство для считывания информации из ассоциативной памяти | 1981 |

|

SU955203A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1056269A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| ФОТОМЕТР УЛЬТРАФИОЛЕТОВОГО ИЗЛУЧЕНИЯ | 1992 |

|

RU2069843C1 |

Авторы

Даты

1980-04-30—Публикация

1976-09-27—Подача