1

Изобретение относится к вычислительной технике.

Характеристики накопителя на МДП-структурах определяют особенности адресного формирователя как устройства, обеспечивающего коммутацию режимов (зались, считывание) и выходных импульсов управления одной полярности как в режиме записи, так и в режиме считывания. Кроме того, адресный формирователь должен обес11ечив,ать необходимый перепад напряжения независимо от нагрузки, т. е. работать в режиме генератора напряжения.

Известные адресные формирователи для накопителя на МДП-структурах, содержащие входной согласующий элемент, делитель напряжения с активными элементами, согласующий элемент режима, характеризует относительно большая длительность фронтов формируемых импульсов при переходе от одного уровня напряжения через нуль к другим уровням напряжения, определяемым режимами записи и считывания; зависимость уровня формируемого напряжения при считывании от параметров выходной ключевой схемы (коэффициент усилия, 1ко); большое значение потребляемой мощности в исходном состоянии; наличие четырех источников питания.

Цель изобретения - уменьшение длительности импульсов при переходе от режима

записи к считыванию, обеспечение стабильности уровней этих импульсов, снижение потребляемой мощности в исходном состоянии формирователя и экономия оборудования.

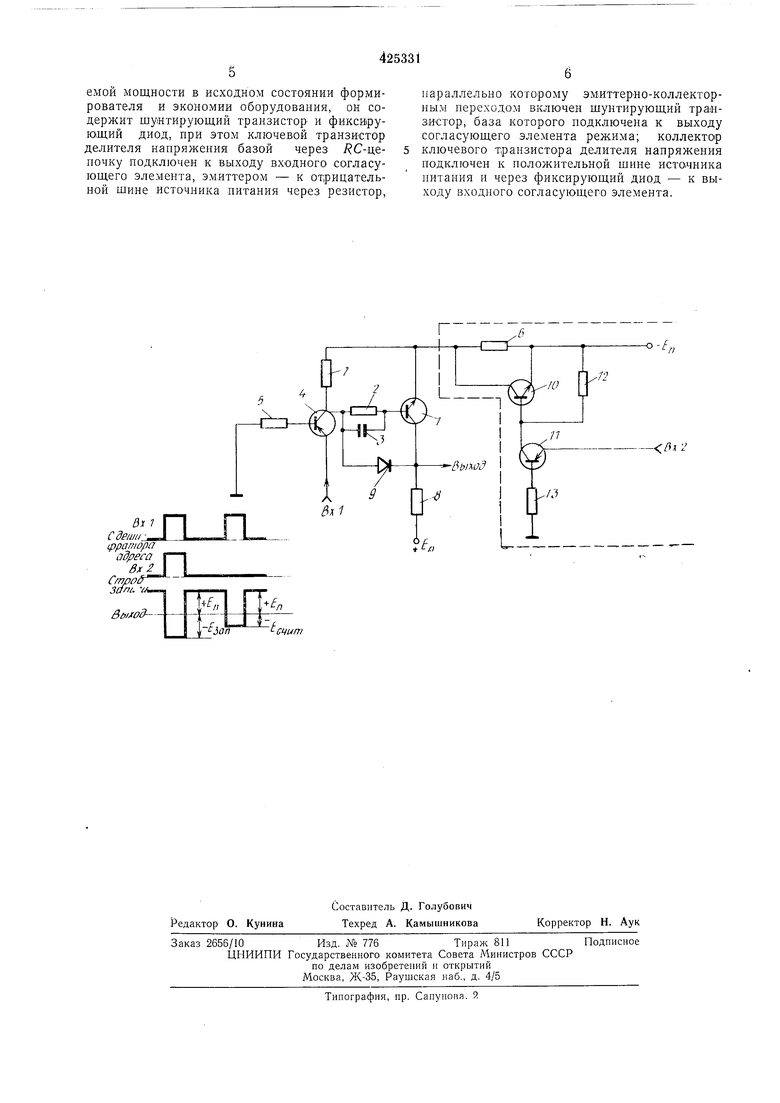

Для этого формирователь снабжен шунтирующим транзистором и фиксирующим диодом, при этом ключевой транзистор делителя напряжения базой через С-цепючку подключен к выходу входного согласующего элемента, эмиттером - к источнику питания через резистор, параллельно которому эмиттерноколлекторным переходом включен шунтирующий транзистор, база которого подключена к коллектору транзистора согласующего элемента режима; коллектор указанного ключевого транзистора подключен к источнику питания противоположной полярности и через фиксирующий диод - к выходу входного согласующего элемента.

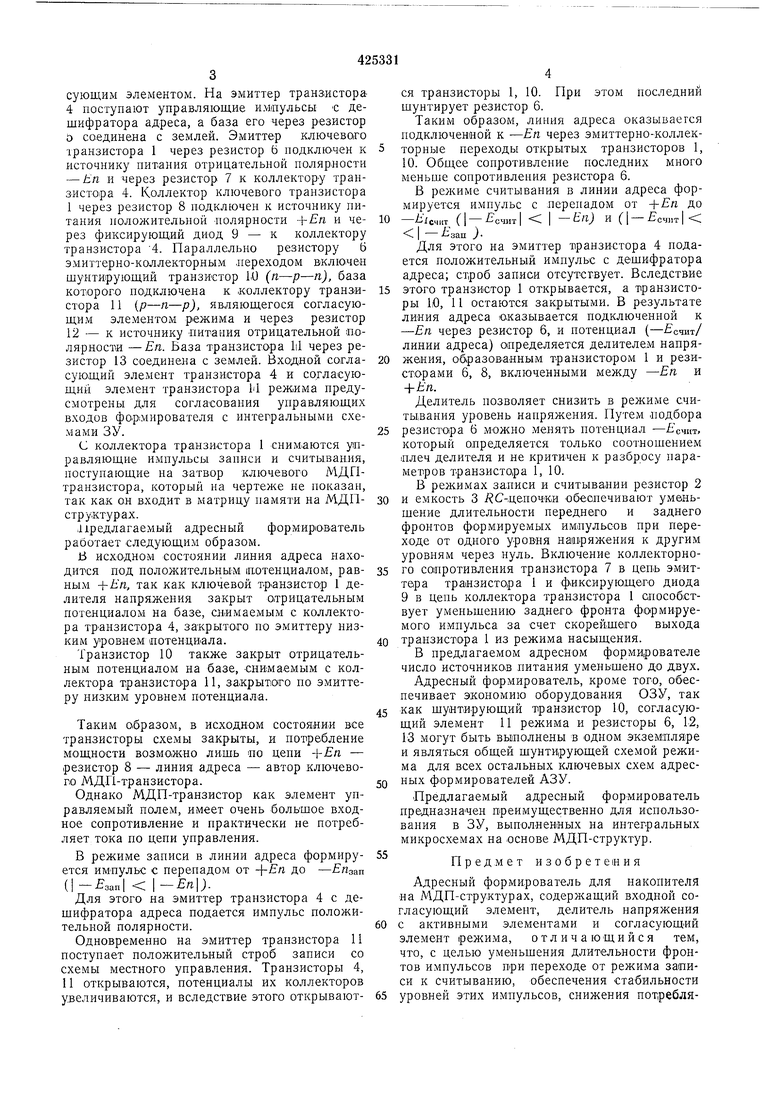

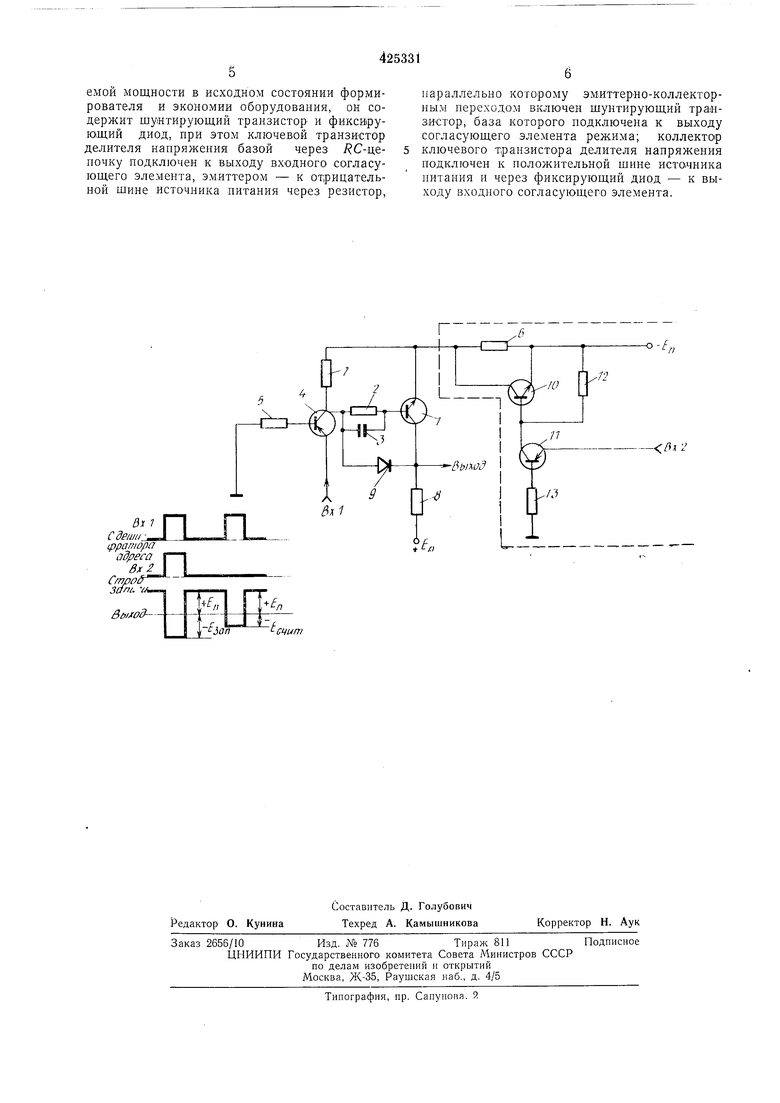

На чертеже приведена принципиальная электрическая схема предлагаемого формирователя для накопителя на МДП-структурах. В схеме предлагаемого формирователя ключевой транзистор 1 (п-р-п), обеспечивающий формирование в линию адреса управляющих импульсов записи и считывания, базой через / С-цепочку, содержащую резистор 2 и емкость 3, подключен к коллектору транзисгора 4 (р-п-р), являющегося входным согласуюащм элементом. На эмиттер транзистора 4 поступают управляющие импульсы € дешифратора адреса, а база его через резистор 0соединена с землей. Эмиттер ключевого аранзистора 1 через резистор 6 подключен к источнику питания отрицательной полярности - Ьп и через резистор 7 к коллектору транзистора 4. Коллектор ключевого транзистора 1через резистор 8 подключен к источнику питания положительпой полярности +Еп и через фиксируюпгий диод 9 - к коллектору транзистора 4. Параллельно резистору 6 эм,иттерно-коллекторным переходом включен шунтирующий транзистор 10 (п-р-п), база которого подключена к коллектору транзистора 11 (р-я-р), являюш,егося согласуюш,им элементом режима и через резистор 12 - к источнику питания отрицательной полярности - Еп. База транзистора 111 через резистор 13 соединена с землей. Входной согласующий элемент транзистор а 4 и согласующий элемент транзистора М режима предусмотрены для согласования управляющих входов формирователя с интегральными схемами ЗУ. С коллектора транзистора 1 сним-аются управляющие импульсы записи и считывания, поступающие на затвор ключевого МДПтранзистора, который на чертеже не показан, так как он входит в матрицу памяти на МДПструктурах. .Предлагаемый адресный формирователь работает следующим образом. В исходном состоянии линия адреса находится под положительным тотенциалом, равным + Еп, так как ключевой транзистор 1 делителя напряжения закрыт отрицательным потенциалом на базе, снимаемым с коллектора транзистора 4, закрытого по эмиттеру низким уровнем потенциала. Транзистор 10 также закрыт отрицательным потенциалом на базе, снимаемым с коллектора транзистора 11, закрытого по эмиттеру низким уровнем потенциал а. Таким образом, в исходном состоянии все транзисторы схемы закрыты, и пот1ребление мощности возможно лишь по цепи -{-Еп - резистор 8 - линия адреса - автор ключевого МДП-транзистора. Однако МДП-транзистор как элемент управляемый полем, имеет очень больщое входное сопротивление и практически не потребляет тока по цепи управления. В режиме записи в линии адреса формируется импульс с перепадом от -{-Еп до -fWaan ( -Еп). Для этого на эмиттер транзистора 4 с дешифратора адреса подается импульс положительной полярности. Одновременно на эмиттер транзистора 11 поступает положительный строб записи со схемы местного управления. Транзисторы 4, 11 открываются, потенциалы их коллекторов увеличиваются, и вследствие этого открываются транзисторы 1, 10. При этом последний шунтирует резистор 6. Таким образом, линия адреса оказываегся подключенной к -Еп через эмиттерно-коллекторные переходы открытых транзисторов 1, 10. Общее сопротивление последних много меньше сопротивления резистора 6. В режиме считывания в линии адреса формируется импульс с перепадом от +Еп до --Ь/счнт (I С I Ьп) и (I -Ссчнт С I - Езйп ) Для ЭТОГО на эмиттер транзистора 4 подается положительный импульс с дешифратора адреса; строб записи отсутствует. Вследствие этого транзистор 1 открывается, а транзисторы 10, 11 остаются закрытыми. В результате линия адреса оказывается подключенной к -Еп через резистор 6, и потенциал (- счит/ линии адреса) определяется делителем напряжения, образованным транзистором 1 и резисторами 6, 8, включенными между -Еп и +Ь/г. Делитель позволяет снизить в режиме считывания уровень напряжения. Путем подбора резисто ра 6 можно менять потенциал , который определяется только соотношением плеч делителя и не критичен к разбросу параметров транзистора 1, 10. В режимах записи и считывании резистор 2 и емкость 3 / С-деночки обеспечивают уменьшение длительности переднего и заднего фронтов формируемых импульсов при переходе от одного уровня напряжения к другим уровням через нуль. Включение коллекторного сопротивления транзистора 7 в цепь эмиттера транзистора 1 и фиксирующего диода 9 в цепь коллектора транзистора 1 способствует уменьшению заднего, фронта формируемого импульса за счет скорейшего выхода транзистора 1 из режима насыщения. В предлагаемом адресном формирователе число источников питания уменьшено до двух. Адресный формирователь, кроме того, обеспечивает экономию оборудования ОЗУ, так как щунтирующий транзистор 10, согласующий элемент 11 режима и резисторы 6, 12, 13 могут быть вьшолнены в одном экземпляре и являться общей шунтирующей схемой режима для всех остальных ключевых схем адресных формирователей АЗУ. Предлагаемый адресный формирователь предназначен преимущественно для использования в ЗУ, выполненных на интегральных микросхемах на основе МДП-структур. Предмет изобрете ния Адресный формирователь для накопителя а МДП-структурах, содержащий входной соласующий элемент, делитель напряжения активными элементами и согласующий лемент режима, отличающийся тем, то, с целью уменьщения длительности фронов импульсов при переходе от режима запии к считыванию, обеспечения стабильности ровней этих импульсов, снижения потребляемой мощности в исходном состоянии формирователя и экономии оборудования, он содержит шунтирующий транзистор и фиксирующий диод, при этом ключевой транзистор делителя напряжения базой через RC-цепочку подключен к выходу входного согласующего элемента, эмиттером - к отрицательной и1ине источника питания через резистор.

параллельно которому эм.иттер«о-коллекторным переходом включен шунтирующий траизистор, база которого подключена к выходу согласующего элемента режима; коллектор ключевого транзистора делителя напряжения подключен к положительной шине источника питания и через фиксирующий диод - к выходу входного согласующего элемента.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки | 1976 |

|

SU650223A1 |

| СТАБИЛИЗИРОВАННЫЙ ИСТОЧНИК ПИТАНИЯ | 2013 |

|

RU2559800C2 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство записи и считывания информациидля НАКОпиТЕлЕй HA МНОп ТРАНзиСТОРАХ | 1979 |

|

SU830563A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Усилитель считывания | 1977 |

|

SU748505A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ЦИФРОВОЙ ИНДИКАЦИЕЙ | 1973 |

|

SU399857A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ | 1973 |

|

SU374656A1 |

| Ключевой стабилизатор постоянного напряжения | 1984 |

|

SU1198499A1 |

| "Формирователь импульсног тока4 | 1977 |

|

SU661744A1 |

rLJT, Сдеши-j (рратдра адреса |Ш. Cmoffi ЗсГпи

ЧГ ВыМд

Даты

1974-04-25—Публикация

1972-05-29—Подача