1

Изобретение относится к вычислительной технике, в частности может быть использовано для построения блоков памяти, в которых в качестве запоминающих элементов используются МНОП-транзисторы.

Известно устройство, которое содержит дешифратор адреса, два источника питания, формирователи записи и считывания 1.

Недостатком этого устройства записи и считывания является то, чт на выбранную строку накопителя (на затворы МНОП-транзисторов) при записи подается импульс напряжения записи (,) амплитудой - 48 В, а при считывании - импульс напряжения считывания ( амплитудой - 5,5 что из-за большой разницы амплитуд импульсов требует применения отдельных формирователей импульсов записи и считывания.

Наиболее близким техническим решением к изобретению является устройство записи и считывания, содержащее блок управления, первый и второй выходы которого соединены с соответствующими входами дешифратора адреса, выходы которого подключены к первым входам соответствующих адресных формирователей считывания, формирователи записи и два источника п-итания 2 .

К недостаткам данного устройства относятся сравнительно большие габариты и невысокая надежность, вызванные громоздкостью и большим количеством формирователей записи и считывания. Подтверждением этого

0 является и тот факт, что элементы памяти на МНОП-транзисторах в настоящее время выпускаются промышленностью в интегральном исполнении (микросхемы 519РЕ1, 519РЕ2), а фор5миро.ватели строятся на навесных дискретных элементах (резисторах, транзисторах и т.п.), в связи с чем имеют габариты несравнимо большие, чем накопитель.

0

Цель изобретения - повышение надежности устройства.

Указанная цель достигается тем, что устройство записи и считывания информации для накопителей на МНОП5транзисторах, содержащее блок управления, первый и второй выходы которого соединены с соответствующими входами дешифратора адреса, выходы которого подключены к первым

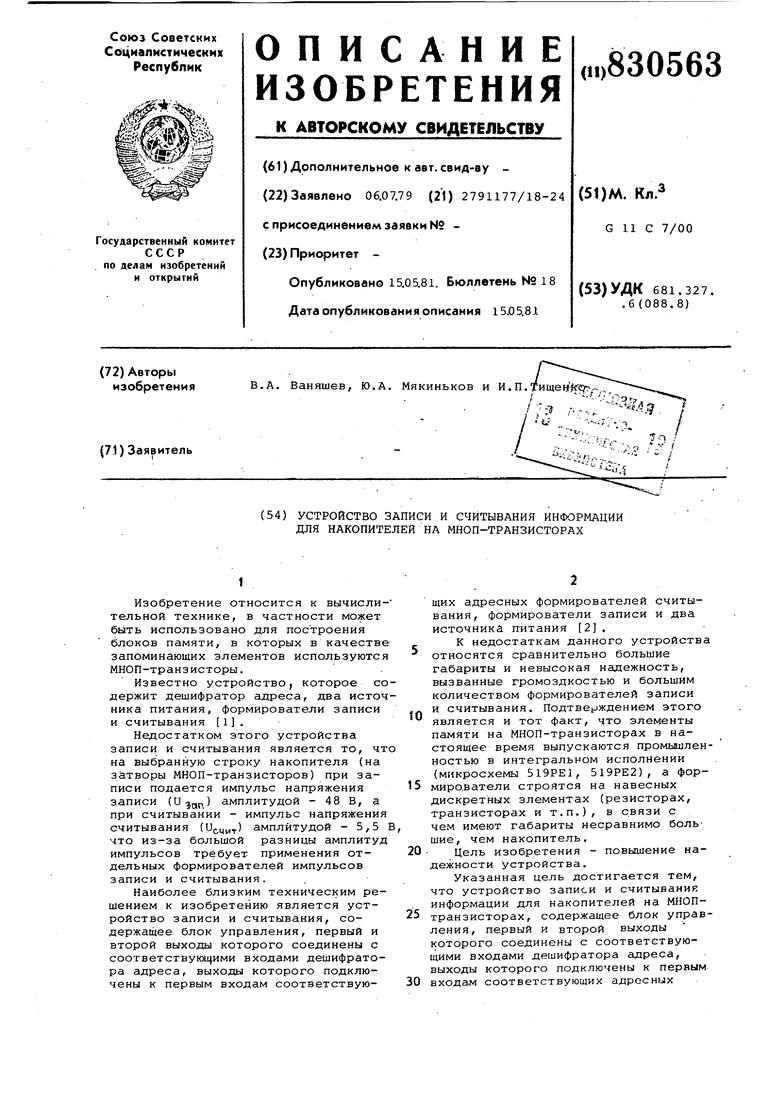

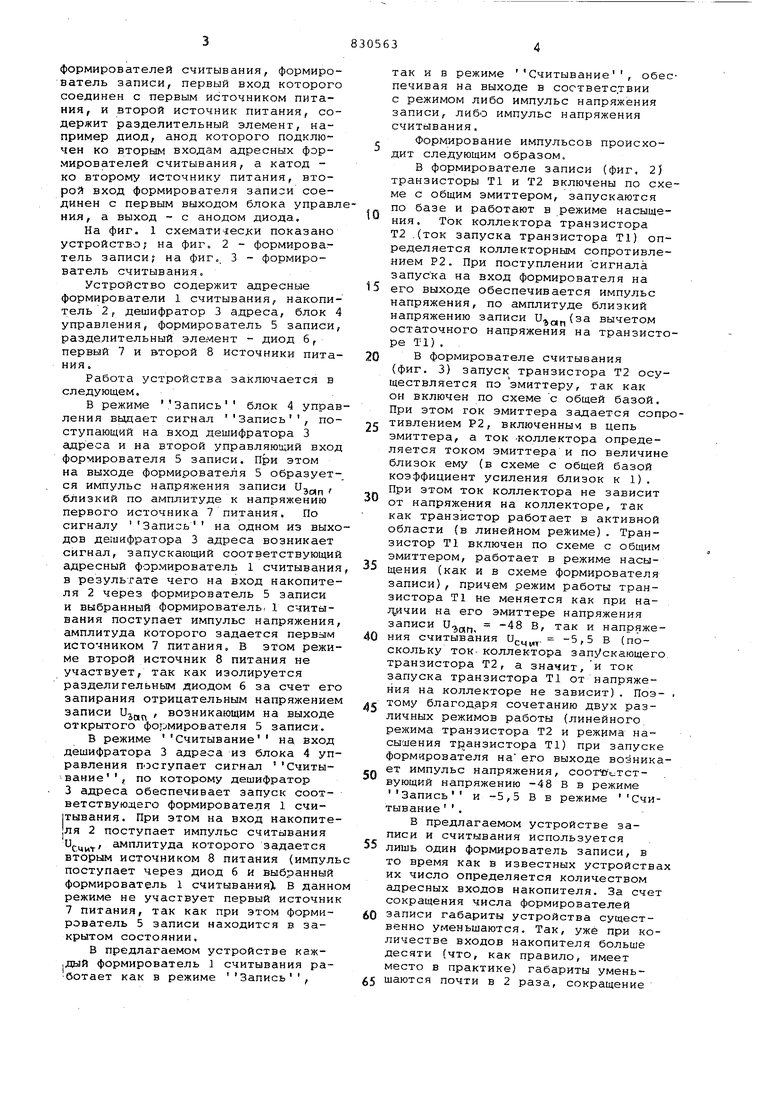

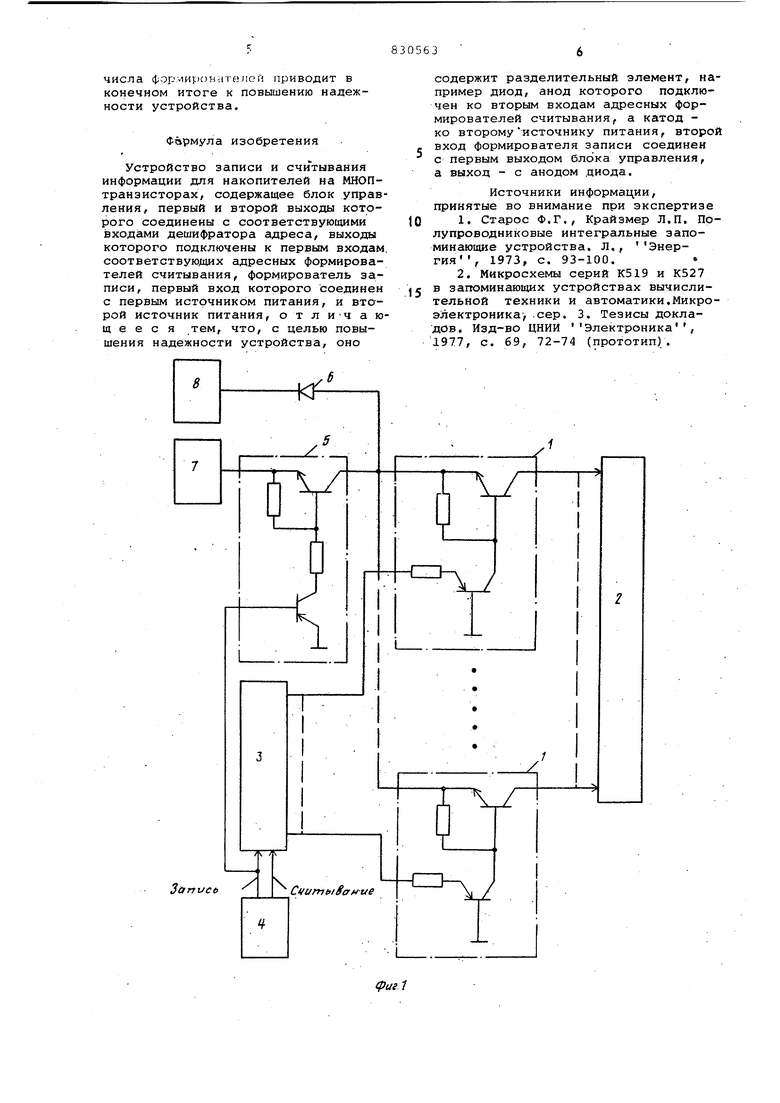

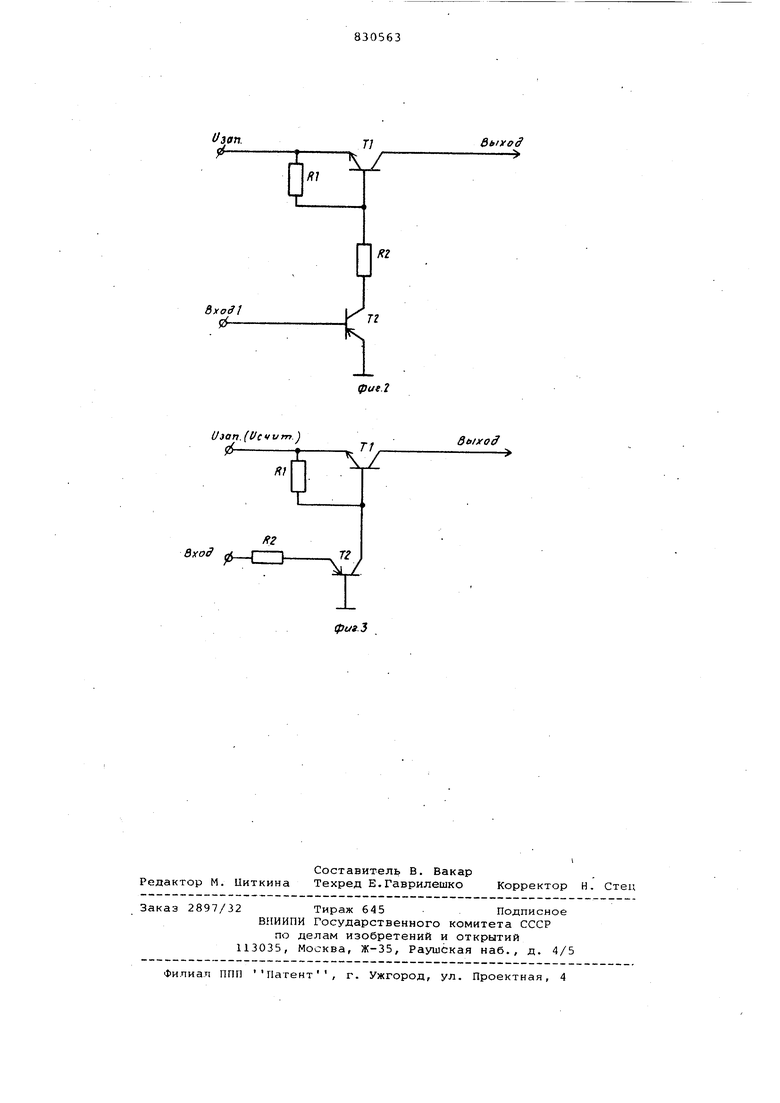

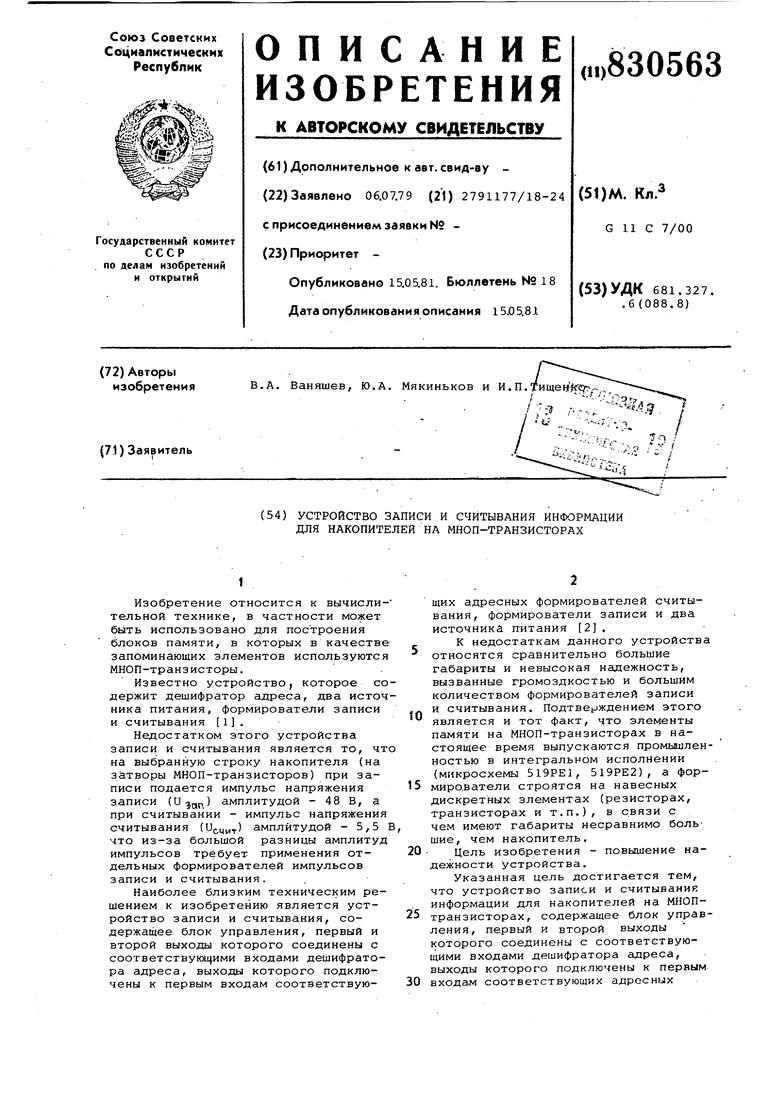

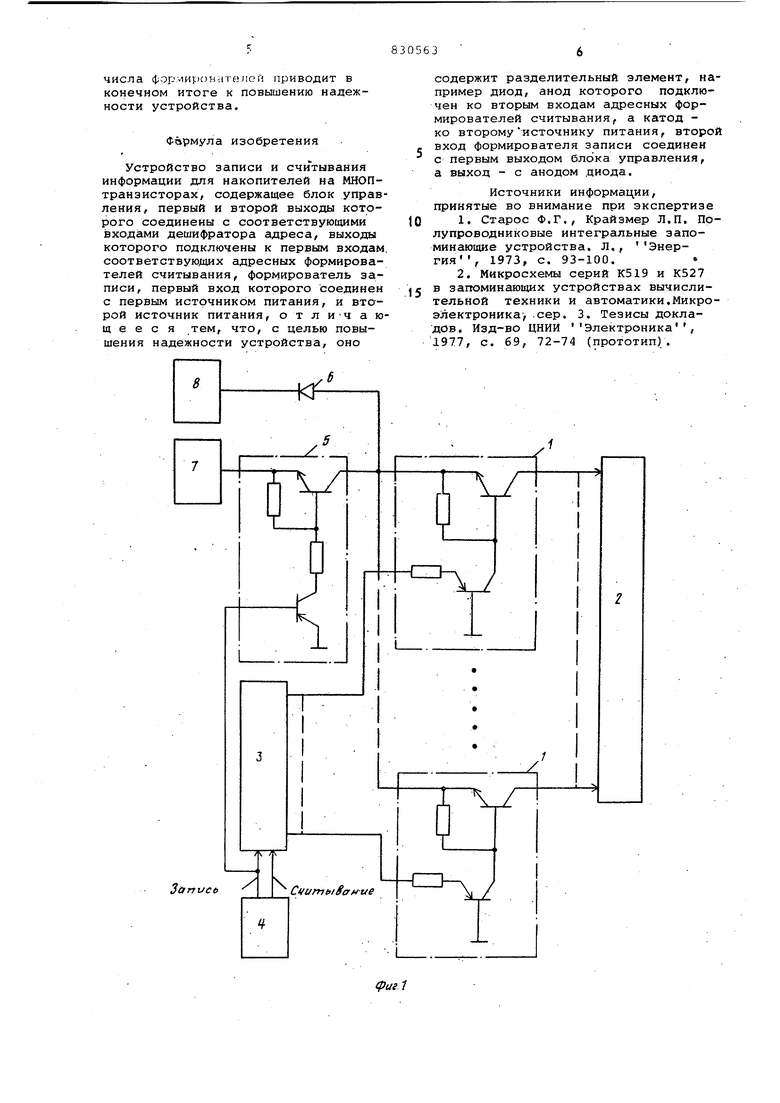

0 входам соответствующих адресных формирователей считывания, формирователь записи, первый вход которого соединен с первым источником питания, и второй источник питания, содержит разделительный элемент, например диод, анод которого подключен ко вторым входам адресных формирователей считывания, а катод ко второму источнику питания, второй вход формирователя записи соединен с первым выходом блока управл ния, а выход - с анодом диода. На фиг, 1 схемати есди показано устройство; на фиг, 2 - формирователь записи на фиг,. 3 - формирователь считывания. Устройство содержит адресные формирователи 1 считывания, накопитель 2 , дешифратор 3 адреса, блок 4 управления, формирователь 5 записи, разделительный элемент - диод б, первый 7 и второй 8 источники питания. Работа устройства заключается в следующем. В режиме .Запись блок 4 управ ления вьвдает сигнал Запись, поступающий на вход дешифратора 3 адреса и на второй управляющий вход формирователя 5 записи. При этом на выходе формирователя 5 образуется импульс напряжения записи Uj, , близкий по амплитуде к напряжению первого источника 7 питания. По Запись на одном из выхо сигналу дов дешифратора 3 адреса возникает сигнал, запуска ощий соответствующий адресный формирователь 1 считывани в результате чего на вход накопите ля 2 через формирователь 5 записи и выбранный формирователь, 1 считывания поступает импульс напряжения амплитуда которого задается первым источником 7 питания, В этом режи ме второй источник 8 питания не участвует, так как изолируется разделигельным диодом 6 за счет ег запирания отрицательным напряжение записи , возникающим на выходе открытого формирователя 5 записи. В режиме Считывание на вход дешифратора 3 адреса из блока 4 уп равления поступает сигнал Считывание, по которому дешифратор 3 адреса обеспечивает запуск соответствуюд1его формирователя 1 считывания. При этом на вход накопите ля 2 поступает импульс считывания счит амплитуда которого задается вторым источником 8 питания (импул поступает через диод 6 и выбранный формирователь 1 считывания), В данн режиме не участвует первый источни 7 питания, так как при этом формирователь 5 записи находится в закрытом состоянии. В предлагаемом устройстве каж,дый формирователь 1 считывания раЗаписьботает как в режиме так и в режиме Считывание, обеспечивая на выходе в соответствии с режимом либо импульс напряжения записи, либо импульс напряжения считывания. Формирование импульсов происходит следующим образом. В формирователе записи (фиг, 2) транзисторы Т1 и Т2 включены по схеме с общим эмиттером, запускаются по базе и работают в режиме насыщения. Ток коллектора транзистора Т2 .(ток запуска транзистора Т1) определяется коллекторным сопротивлением Р2. При по.ступлении сигнала запуска на вход формирователя на его выходе обеспечивается импульс напряжения, по амплитуде близкий напряжению записи (за вычетом остаточного напряжения на транзисторе Т1) . . В формирователе считывания (фиг. 3) запуск транзистора Т2 осуществляется по эмиттеру, так как он включен по схеме с общей базой. При этом ГОК эмиттера задается сопротивлением Р2, включенны в цепь эмиттера, а ток -коллектора определяется током эмиттера и по величине близок ему (в схеме с общей базой коэффициент усиления близок к 1). При этом ток коллектора не зависит от напряжения на коллекторе, так как транзистор работает в активной области (в линейном режиме). Транзистор Т1 включен по схеме с общим эмиттером, работает в режиме насыщения (как и в схеме формирователя записи), причем режим работы транзистора Т1 не меняется как при на его эмиттере напряжения записи -48 В, так и напряже -5,5 В (пония считывания CJ скольку ток-коллектора запускающего транзистора Т2, а значит, и ток запуска транзистора Т1 от напряжения на коллекторе не зависит), Поэ- , тому благодаря сочетанию двух различных режимов работы (линейного, режима транзистора Т2 и режима насышения транзистора Т1) при запуске формирователя наего выходе возникает импульс напряжения, соот тствующий напряжению -48 В в режиме Запись и -5,5 В в режиме Считывание . В предлагаемом устройстве записи и считывания используется лишь один формирователь записи, в то время как в известных устройствах их число определяется количеством адресных входов накопителя. За счет сокращения числа формирователей записи габариты устройства существенно уменьшаются. Так, уже при количестве входов накопителя больше десяти (что, как правило, имеет место в практике) габариты уменьшаются почти в 2 раза, сокращение

числа фчЭрми1;)ОН;|тнлей приводит в конечном итоге к повышению надежности устройства.

Формула изобретения

Устройство записи и считывания информации для накопителей на МНОПтранзисторах, содержащее блок управления, первый и второй выходы которого соединены с соответствующими входами дешифратора адреса, выходы которого подключены к первым входам, соответствующих адресных формирователей считывания, формирователь записи, первый вход которого соединен с первым источником питания, и второй источник питания, о т л и-ч а ющ е е с я .тем, что, с целью повышения надежности устройства, оно

содержит разделительный элемент, например диод, анод которого подключен ко вторым входам адресных Формирователей считывания, а катод ко второмуисточнику питания, второй , вход формирователя записи соединен с первым выходом блока управления, а выход - с анодом .диода.

Источники информации, принятые во внимание при экспертизе

0 1. Старое Ф.Г., Крайзмер Л.П. Полупроводниковые интегральные запоминающие устройства. Л., Энергия, 1973, с. 93-100.

2. Микросхемы серий К519 и К527

е В запоминающих устройствах вычислительной техники и автоматики.Микроэлектроника-, .сер. 3. Тезисы докладов, Изд-во ЦНИИ Электроника, 1977, с. 69, 72-74 (прототип).

Вхов

0-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для стирания информации в блоках памяти на МНОП транзисторах | 1981 |

|

SU955194A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ ДЛЯ НАКОПИТЕЛЯ НА МДП-СТРУКТУРАХ | 1972 |

|

SU425331A1 |

| Запоминающее устройство | 1976 |

|

SU608197A1 |

| Запоминающее устройство с сохранением информации при отключении питания | 1986 |

|

SU1365133A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1101890A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| ВЫХОДНАЯ СХЕМА С ТРЕМЯ СОСТОЯНИЯМИ | 1992 |

|

RU2072629C1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1133621A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU385314A1 |

i/jan.(.)

/f/

ff2

тг

L

Bfixoff

vz

Авторы

Даты

1981-05-15—Публикация

1979-07-06—Подача