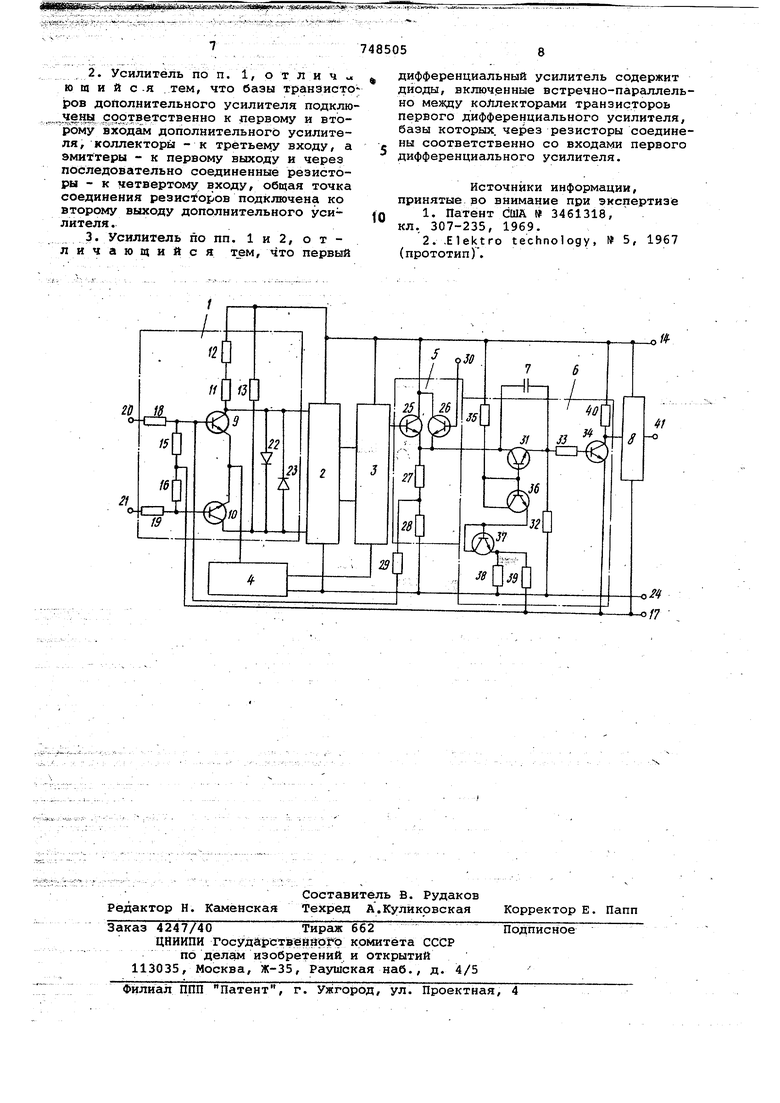

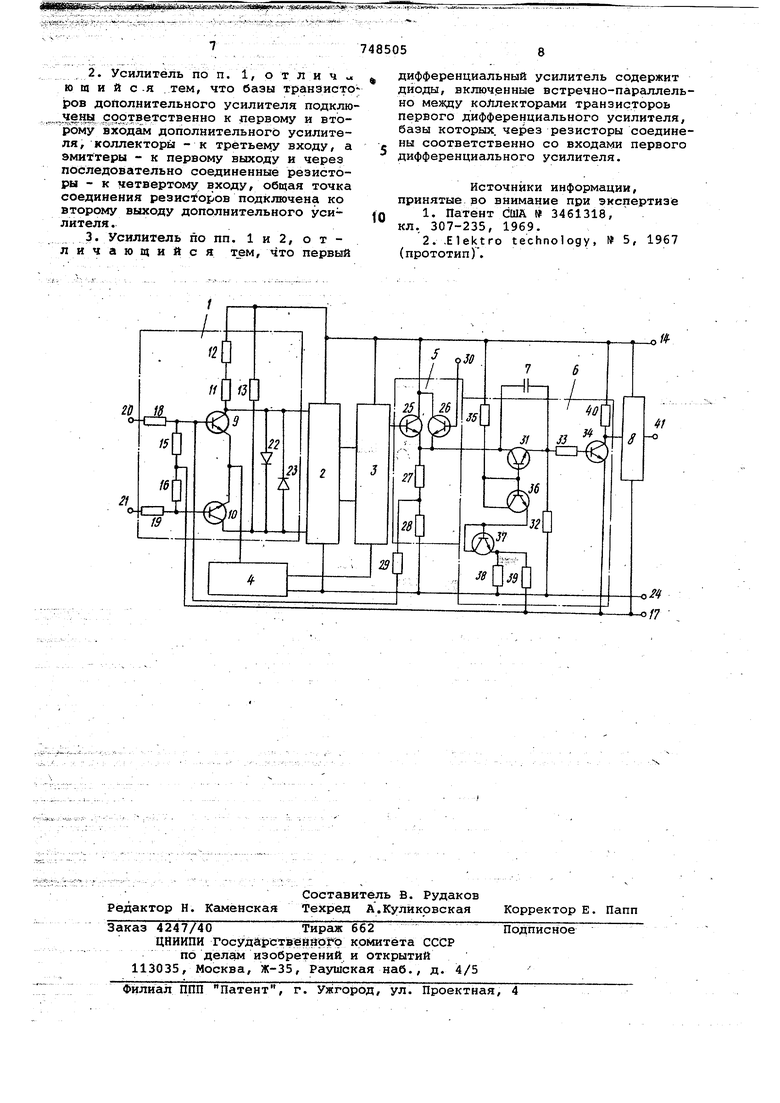

Изобретение относится к области запоминающих устройств. Известен усилитель считывания,со держащий многокаскадный усилитель с гальваническими межкаскадными связями, амплитудный селектор, формирователь выходного сигнала, конденсатор 1 .. Недостатком этого усилителя являе ся низкаяпомехоустойчивость. . Наиболее близким техническим реше нием к данному иэобрет ениго является усилитель считывания, содержаний по следовательно соединенные транзисторные дифференциальные усилители с непосредственными межкаскадными свя зями, последовательно соединенные .амплитудный селектор и формировател выходного сигнала, управлянлцую шину и шины питания 2 .. Недостатками эт.ого усилителя считывания являются зависимость порога срабатывания усилителя от амплитуды и полярности входных импульсов помех, что снижает его функциональную надежность и помехоустойчивость, высокая чувствительность к неидентичности параметров элементов, так как для обеспечения рабочего режима уси лителя необходимо выполнение жестких требований к идентичности номиналов резисторов и вольтамперных характеристик транзисторов дифференциальных усилителей с непосредственными межюаск.адными связями. Целью изобретения является повышение надежности и помехоустойчивости усилителя считывания, снижение чувствительности к неидентичности па.раметров элементов усилителя считы вания. Поставленная цель достигается тем, что предлагаемый усилитель считыва- , ния содер:: ит дополнительный транзисторный усилитель и элемент обратной связи, причем первый вход дополнительного усилителя подключен к выходу одного из дифференциальных усилителей , второй вход - к управляющей шине, третий и четвертый входы - к шинам питания,.первый выход дополнительного транзисторного усилителя соединен со входом амплитудного селектора, второй выход через элемент обратной связи - с одним из входов первого дифференциального усилителя; при этом базы транзисторов дополнительного усилителя подключены соответственно к первому и второму входам дополнительного усидителя, кол лекторы - ктретьему входу, а эмятТеры - к первому выходу и через по.следовательно соединенные резисторы - к четвертому .входу, общая точ ка соединения резисторов подключена ко второму выходу дополнительного у .литедя. ПejpвыйдифференциаДьный усь литель целесообразно выполнить так, чтобы он содержал диоды, включенные встречно-параллельно между коллекто рами транзисторов первого дифференциадьного усилителя, базы которых ч рез резисторы соединены соответстве но со входами первого дифференциаль ного усилителя. На чертеже представлена эдектрическая схема предлагаемого усилителя считывания. Усилитель считывания содержит тр дифференциальных транзисторных усилителя 1-3 с непосредственными межкаскалными связями, источник постоя ных отношений тока 4,дополнительны транзисторный усилитель 5,амплитудный селектор б, конденсатор 7, формирователь выходного сигнала 8. Первый усилитель 1 выполнен на транзисторах 9 и 10 с резисторами 11-13 в цепях коллекторов, подключенньгми к. положительной шине 14 питания, и базовыми резисторами 15, 16 соответственно, подключенньаш к шине нудевого потенциала 17. К базам транзисторов 9 и 10 подключены резисторы 18 и 19 соответственно , другие выводы которых подключены к соответствующим входным шинам 20 и 21, являющимся входами усилителя 1. Между коллекторами транзисторов 9 и 10 включены встречно-параллельно цва диода 22, 23. Второй усилитель 2 представляет собой эмиттерный повторитель, подключенный к шин 14,.отрицательной шине питания 24 к к коллекторам транзисторов 9, 10 усилителя 1. Третий усилитель 3 пОдкдючен к усилителю 2, шине 14 и шине 24. Дополнительный усилитель 5 содержит два транзистора 25 и 26, кол лекторы которых подключены к шине 14, эмиттеры соединены и через два последовательно соединенных резисто ра 27 и 28 подключены к шине 24. Об щая точка соединения резисторов 27 и 28 через элемент обратной. связи, например резистор 29, соединена с б зой транзистора 9. Базы транзисторов 25 и 26 подключены соответстве но к первому и второму 30 входам .усилителя 1. .,., Амплитудный селектбр б содерхгит транзистор 31, коллектор которого подключен к общей точке соединения резистЪра 27 и эмиттеров транзисторов 25 и 26, а эмиттер через резистор 32 - к шине 24 и через резистор 33 - к базе транЭистора 34 ампдитудного селектора 6. Между коллектором

748505 и эмиттером транзистора 31 вк.лючен переходной конденсатору 7. База транзистора 31 через резистор 35 соединена с шиной 14 и непосредственно - с базой и коллектором транзистора 36, эмиттер которого подключен к- коллектору и базе транзистора 37. Эмиттер тран« зистора 37 через резистор 38 соединен с шиной 24 и через резистор 39 с шиной 17. Эмиттер транзистора 34 подключен к шине 17, коллектор транзистора 34 через резистор 40 соединен с шиной 14 и непосредственно - с формирователем выходного сигнала 8, соединенным с выходной шиной 41. Устройство работает следующим образом. В исходном состоянии, при отсутствии входных, сигналов, транзисторы 2, 3, усилителей 9 и 10 работают в ли нейном режиме. Величины резисторов 11 и 13 в цепях коллекторов транзисторов 9 и 10 не равны - величина резисJTOpa 11 меньше,чем величина резистора 13. При отключенном резисторе 29 от базы транзисторов 9 путем выбора величины резистора 12 производится выбор рабочей точки транзисторов 9 и 10 усилителя 1 и, соответственно, линейного режима усилителей 2, 3с .непосредственными связями, т.е. про:ИЗводится симметрирование плеч дифференциальных усилителей по постоянному току, устранение исходного разбаланса, вызванного неидентичностью параметров транзисторов 9 и 10, резисторов 15 и 16 и элементов в плечах усилителей 2,3, после чего резистор 29 подключается к базе транзисторов 9. Это позволяет снизить требования к идентичности параметров элементов усилителя считывания. За счет того, что величина резистора 11 .меньше величины резистора 13, возможно устранение р1азбаланса обеих ,по-. лярностей. , , Транзистор 26 дополнительного уси.лителя 5 закрыт за счет пол.ожитель-. ного смещения, подаваемого на его эмиттер с выхода усили.теля 2 через переход база-эмиттер транзистора 25, работающего в линейном режиме. Режим работы дополнительйого усилителя, определяемый величиной потенциала, поступившего на базу транзистора 25, и токозадающими резисторами 27 и 28, выбран таким образом, что общая точка соединения резисторов 27 и 28 имеет исходный нулевой потен-. циал при отрегулированном (выбором величины резистора 12) режиме усилителей 1-3. При нарушении симметрии (например, в диапазоне температур, ух&д параметров элементов во времени и т.д.) плеч усилителей статический режим и динамические параметры усилителей 1-3,а также потенциал эмиттеров транзисторов 25 и 26 дополнительного усилителя 5 стабилиэ руется за счет отрицател1 ной обратной С1вяэи из нулевой точки дополнительг ftoro усилителя через резистор 29 на базу входного транзистора 9, повышая тем самым устойчивость работы и надежность усилителя считывания. Влияние обратной связи на б.азу транзистора 10 незначительно, так как оно ос лабляется резисторами 18, 19, подключенными к входным шинам 20, 21, которые соединяются с разрядной обмоткой накопителя (на чертеже не показан). Транзистор 34 амплитудного селектора б закрыт за счет того, что его эмиттер соединен с шиной 17, а на его базу подается напряжение смещ ния, недостаточное для отпирания. Be личина этого напряжения смещения определяется величиной потенциала в об щей точке соединения резисторов 38, 39 и эмиттера транзистора 37 и регулируется путем изменения величины ре зистора, например резистора 38, обес печивая тем самым регулировку порога срабатывания усилителя считывания. Транзисторы 36 и 37 в диодном включе НИИ и переход база- эмиттер транзисто ра 31 соединены с переходом база-эми тер транзистора 34 через ограничител ный резистор 33 таким образом, что обеспечивается температурная зависимость исходного смещения транзистора 34, эквивалентная температурной зави симости его напряжения смещения. Для повышения идентичности этой зависимости целесообразно применить однотипные транзисторы 31,34,36,37,все или попарно,например,31 и 36,34 и 37 Переход коллектор-эмиттер транзистора 31 и конденсатор 7 исключает влияние статического режима дифференциальных каскадов 1, 2, 3 на исходное смещение транзистора 34, а, следовательно, и на порог срабатывания усилителя считывания. На входные шины 20 и 21 поступают полезные сигналы в режиме считывания информации и двухполярная помеха в режиме записи информации. Амплитуда помехи на несколько порядков больше амплитуды полезного сигПоступающие на шины 20 и 21 уси.лителя считывания полезные сигналы и помехи усиливаются усилителями 1-3 через переход база-эмиттер транзистора 25 поступают на коллектор транзистора 31 и через конденсатор 7 и резистор 33 - на базу транзистора 34 Диоды 22,23 исключают режим насыщения транзисторов 9 и 10 при поотуплении на них импульса помехи с амплитудой, значительно превышающей амплитуду полезного сигнала, повышая .помехоустойчивость усилителя считы вания.. На базу транзистора 34 полезный сигнал поступает относительно исходного, регулируемого, например резистором 38, напряжения смещения; если сумма амплитуды усиленного сигнала и напряжения смещения превышает напряжение отпирания транзистора 34, он отпирается и на его коллекторе появляется импульс отрицательной полярности, который поступает на формирователь выходного сигнала 8, а оттуда - на выходную шину 41. В режиме записи информации в накопитель памяти на вход 30, т.е. на базу транзистора 26, подается импульс запрета положительной полярности, во времени совпадающий с помехой в режиме записи и имеющий амплитуду, достаточную, для компенсации усиленной амплитуды импульса помехи отрицательйой полярности. Импульс запрета через перехбд база-эмиттер транзистора 26 поступает в общую точку соединёния эмиттеров транзисторов 25, 26 и конденсатора 7, где он складывается с помехой положительной или отрицательной полярности, в результате чего через конденсатор 7. в режиме записи информации запрещается прохождение импульсов помех отрицательной полярности и обеспечивается прохожден ие импульсов только положительной полярности. При этом повышается помехоустойчивость усилителя считывания, так как независимо от полярности помехи разряд конденсатора 7 происходит через низкое сопротивление открытого транзистора 31 и переходные процессы конденсатора 7 не влияют на исходное напряжение .смещениятранзистора 34, а следовательно, и на порог срабатывания усилителя считывания. Формула изобретения 1. Усилитель считывания, содер5кащий последовательно соединенные дифференциальные усилители с непосредственными межкаскадными, связями, последовательно соединенные амплитудный селектор и формирователь выходного сигна-, ла, управляющую шину и шины питания, отличающийся тем, что, с целью повышения надежности усилителя, он содержит элемент обратной связи, и дополнительный транзисторный усили:Тель, первый вход которого подключен :к выходу одного из дифференциальйых Усилителей, второй вход - к управляющей Шине, третий и четвертый входы к шинам питания, первый выход дополнительного транзисторного усилителя соединен со входом амплитудного селектора, второй выход через элемент обратной связи - с одним из входов первого дифференциального усилителя.

2.Усилитель по п. 1, о т л и ч «о щ и и с -Я тем, что базы транзистоipOB дополнительного усилителя подключщы соответственно к первому и второму входам дополнительного усилителя , коллекторй - к третьему входу, а эмиттеры - к первому выходу и через последовательно соединенные резисторы - к четвертому входу, общая точка соединения резисторов подключена ко второму выходу дополнительного усилителя,

3.Усилитель по пп. 1 и 2, о т личающийся , что первый

дифференциальный усилитель содержит диоды, включенные встречно-параллельно меаду коллекторами транзисторов первого дифференциального усилителя, базы которых, через резисторы соединены соответственно со входами первого дифференциального усилителя.

Источники информации, принятые во внимание при экспертизе 1, Патент США № 3461318, кл, 307-235, 1969,

2, .Elektro technology, № 5, 1967 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Источник питания электрофильтра | 1983 |

|

SU1201807A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Система для автоматического резервирования телевизионных линий связи и устройство допускового контроля | 1981 |

|

SU1061291A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1993 |

|

RU2060564C1 |

| Устройство емкостной гальванической развязки | 1986 |

|

SU1370767A1 |

| Устройство считывания информации | 1988 |

|

SU1547027A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛА ВКЛЮЧЕНИЯ ПОМЕХ | 1993 |

|

RU2122281C1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| АВТОДИННЫЙ АСИНХРОННЫЙ ПРИЕМОПЕРЕДАТЧИК СИСТЕМЫ РАДИОЗОНДИРОВАНИЯ АТМОСФЕРЫ | 2022 |

|

RU2786415C1 |

| Формирователь импульсов | 1974 |

|

SU657601A1 |

Авторы

Даты

1980-07-15—Публикация

1977-10-11—Подача