1

Изобретение относится к области связи и может быть использовано при передаче телекодовой информации по каналам связи.

Известны устройства исправления ошибок, использующие локализацию ошибок в кодовой последовательности и восстановление переданных символов, содержащие блок приема, ВЫХОД которого одновременно подключен через первый вход и первый выход блока обнаружения ошибок В комбинациях строк ко ВХОДУ блока фиксирования искаженных комбинаций строк, а через первый вход и выход блока памяти, первый вход и первый выход блока стирания строк, вход и выход первого регистра, первый вход и выход блока восстановления стираний и исправления ошибок - к первому входу второго регистра, ко второму ВХОДУ которого подсоединен первый выход блока управления, причем выход второго регистра является ВЫХОДОМ устройства.

С целью повышения достоверности в предлагаемом устройстве ВЫХОД блока фиксирования искаженных комбинаций строк через первый ВХОД и ВЫХОД блока программирования исправления ошибок в комбинациях столбцов подсоединен к первому входу блока памяти, подсоединенного вторым входом ко второму. ВЫХОДУ блока управления, третий выход которого через первый вход и первый выход блока запрета стираний искаженных комбинаций

строк подключен одновременно через второй ВХОД и второй ВЫХОД блока стирания строк ко второму входу блока восстановления стираний и исправления ошибок, к третьему входу второго регистра и первому входу блока управления, подсоединенного своим четвертым ВЫХОДОМ через первый вход и первый ВЫХОД блока проверки восстанавливаемости одновременно к входу счетчика, а через второй ВХОД и второй ВЫХОД блока запрета стираний искаженных комбинаций строк одновременно ко второму входу блока программирования исправления ошибок в комбинациях столбцов и ко второму входу блока управлеПИЯ, пятый ВЫХОД которого подключен к третьему входу блока стираиия строк, а шестой ВЫХОД блока управления подсоединен к третьему входу блока программирования исправления ошибок в комбинациях столбцов,

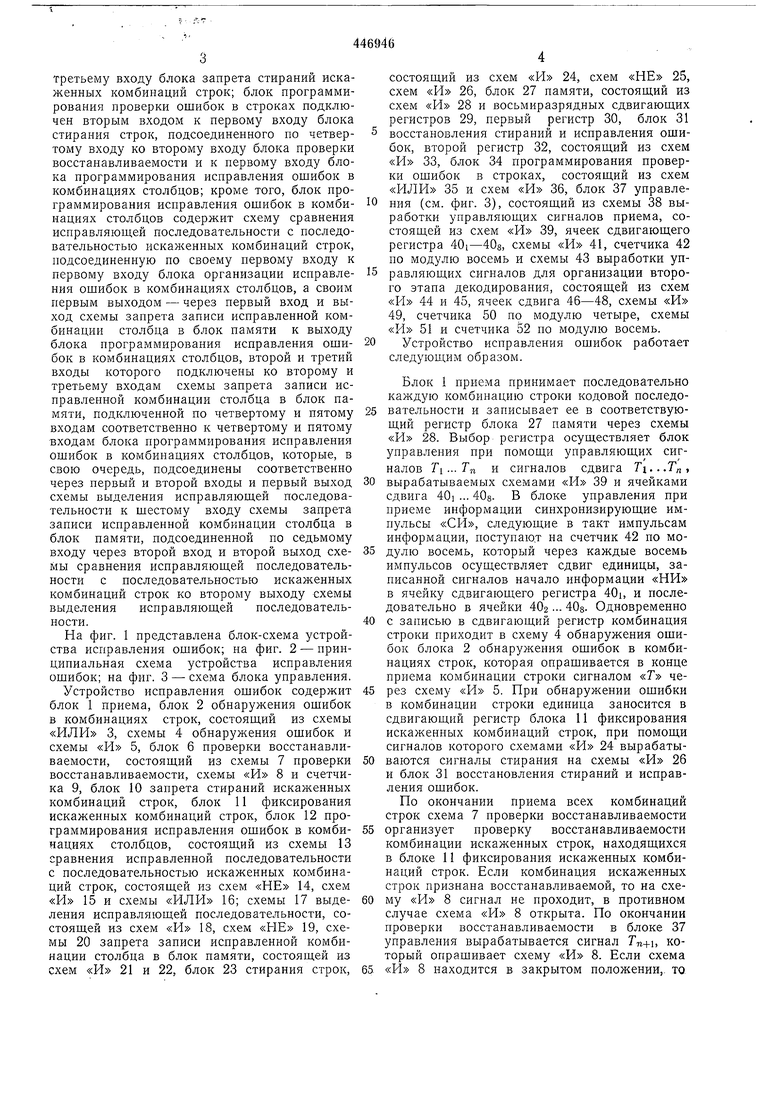

к четвертому и пятому входам которого подключены соответственно первый вход второго регистра и выход первого регистра; второй ВЫХОД блока проверки восстанавливаемости подсоединен к третьему входу блока управления, первый выход которого через первый ВХОД и ВЫХОД блока программирования проверки ошибок В строках подключен одновременно ко второму входу блока памяти и через второй ВХОД и второй ВЫХОД блока обкаружения ошибок в комбинациях строк к третьему входу блока запрета стираний искаженных комбинаций строк; блок программирования проверки ошибок в строках подключен вторым входом к первому входу блока стирания строк, подсоединенного но четвертому входу ко второму входу блока проверки восстанавливаемости и к первому входу блока программирования исправления ошибок в комбинациях столбцов; кроме того, блок программирования иснравления ошибок в комбинациях столбцов содержит схему сравнения нспраБляюш,ей последовательности с носледовательностью искал енных комбинаций строк, подсоединенную по своему первому входу к первому входу блока организации исправления ошибок в комбинациях столбцов, а своим первым выходом - через первый вход и выход схемы запрета записи исправленной комбинации столбца в блок памяти к выходу блока программирования исправления ошибок в комбинациях столбцов, второй и третий входы которого подключены ко второму и третьему входам схемы запрета записи исправленной комбинации столбца в блок памяти, подключенной по четвертому и пятому входам соответственно к четвертому и пятому входам блока программирования иснравления ошибок в комбинациях столбцов, которые, в свою очередь, подсоединены соответственно через первый и второй входы и первый выход схемы выделения исправляющей последовательности к щестому входу схемы запрета записи исправленной комбинации столбца в блок памяти, подсоединенной по седьмому входу через второй вход и второй выход схемы сравнения исправляющей последовательности с последовательностью искаженных комбинаций строк ко второму выходу схемы выделения исправляющей последовательности. На фиг. 1 представлена блок-схема устройства исправления ошибок; на фиг. 2 - принципиальная схема устройства исправления ошибок; иа фиг. 3 - схема блока управления. Устройство исправления ошибок содержит блок 1 приема, блок 2 обнаружения ошибок в комбинациях строк, состоящий из схемы «ИЛИ 3, схемы 4 обнаружения ошибок и схемы «И 5, блок 6 проверки восстанавливаемости, состоящий из схемы 7 проверки восстанавливаемости, схемы «И 8 и счетчика 9, блок 10 запрета стираний искаженных комбинаций строк, блок 11 фиксирования искаженных комбинаций строк, блок 12 программирования исправления ощибок в комбинациях столбцов, состоящий из схемы 13 сравнения иснравленной последовательности с последовательностью искаженных комбинаций строк, состоящей нз схем «НЕ 14, схем «И 15 и схемы «ИЛИ 16; схемы 17 выделения исправляющей последовательности, состоящей из схем «И 18, схем «НЕ 19, схемы 20 запрета записи исправленной комбинации столбца в блок памяти, состоящей из схем «И 21 и 22, блок 23 стирания строк, состояший из схем «И 24, схем «НЕ 25, схем «И 26, блок 27 памяти, состоящий из схем «И 28 и восьмиразрядных сдвигающих регистров 29, первый регистр 30, блок 31 восстановления стираний и исправления ошибок, второй регистр 32, состоящий из схем «И 33, блок 34 программирования проверки ошибок в строках, состояший из схем «ИЛИ 35 и схем «И 36, блок 37 управления (см. фиг. 3), состоящий из схемы 38 выработки управляющих сигналов приема, состоящей из схем «И 39, ячеек сдвигающего регистра 40i-408, схемы «И 41, счетчика 42 по модулю восемь и схемы 43 выработки управляющих сигналов для организации второго этапа декодирования, состоящей из схем «РЬ 44 и 45, ячеек сдвига 46-48, схемы «И 49, счетчика 50 по модулю четыре, схемы «И 51 и счетчика 52 по модулю восемь. Устройство исправления ошибок работает следующим образом. Блок 1 приема принимает последовательно каждую комбинацию строки кодовой последовательности и записывает ее в соответствуюЩ™ регистр блока 27 памяти через схемы «И 28. Выбор регистра осуществляет блок управления при помощи управляющих сигналов TI ... Гп и сигналов сдвига Ti...Tn, вырабатываемых схемами «И 39 и ячейками сдвига 40 ... 408. В блоке управления при приеме информации синхронизирующие импульсы «СИ, следующие в такт импульсам информации, поступают на счетчик 42 по модулю восемь, который через каждые восемь импульсов осуществляет сдвиг единицы, записанной сигналов начало информации «НИ в ячейку сдвигающего регистра 40i, и последовательно в ячейки 402 - 408- Одновременно с записью в сдвигающий регистр комбинация строки приходит в схему 4 обнаружения ошибок блока 2 обнаружения ошибок в комбинациях строк, которая опрашивается в конце приема комбинации строки сигналом «Г через схему «И 5. При обнаружении ошибки в комбинации строки единица заносится в сдвигающий регистр блока 11 фиксирования искаженных комбинаций строк, при помощи сигналов которого схемами «И 24 вырабатываются сигналы стирания на схемы «И 26 и блок 31 восстановления стираний и исправления ошибок. По окончании приема всех комбинаций строк схема 7 нроверки восстанавливаемости организует проверку восстанавливаемости комбинации искаженных строк, находящихся в блоке 11 фиксирования искаженных комбинаций строк. Если комбинация искаженных строк признана восстанавливаемой, то на схему «И 8 сигнал не проходит, в противном случае схема «И 8 открыта. По окончании проверки восстанавливаемости в блоке 37 управления вырабатывается сигнал Tn+i, который опрашивает схему «И 8. Если схема «И 8 находится в закрытом положении,, то

вырабатывается сигнал , сигналы Г и Т со схемы организации второго этапа декодирования блока управления организуют последовательный выбор комбинаций столбцов из регистров 29 через схемы «И 26, осуществляющие стирание символов комбинаций строк, в которых при приеме обнаружены ошибки, в первый регистр 30 и далее в блок 31 восстановления стираний и исправления ошибок.

Сигналом Р с блока управления комбинация столбца, прошедшая через блок исправления, выдается получателю. После выбора всех столбцов в блоке 50 управления срабатывает счетчик, устанавливаюш,ий все устройство в исходное состояние. Если полученная комбинация искаженных строк при их стирании может оказаться невосстаиавливаемой, то сигнал со схемы «И 8 поступает на блок 10 запрета стираний искаженных комбинаций строк и на счетчик 9. Блок 10 запрета запрещает выдачу сигналов стираиий со схем «И 24 на схемы «И 26 и в блок 31 восстановления стираний и исправления ошибок. Кроме того, сигнал Кг с блока 10 запрета стираний искаженных комбинаций строк поступает на схему «И 51, открывая вход на счетчик 52, который подсчитывает число комбинаций столбцов, прошедших через блок 31 восстановления стираний и исправления сшибок.

Сигнал Гп+ь поступив в конце приема кодовой последовательности на схему «И 45, открывает вход синхроимпульсов на сдвиг единицы в ячейках 46-48, обеспечивая выработку сигналов Т Р, Т, при помощи которых комбинации столбцов поступают в первый регистр 30 блока 31 восстановления стираний и исправления ошибок. Из блока 31 восстановления стираний и исправления ошибок исправленная комбинация столбца поступает на схему 17 выделения исправляющей последовательности, на схемы «И 19, на второй вход которых поступают сигналы с первого регистра 30, в последнем находится неисправленная комбинация столбца. На выходе схемы 17 образуется исправляющая последовательность, содержащая единичные символы на позициях, на которые в блоке 31 восстановления стираний и иснравления ошибок произведено исправление символов на противоположные.

Исправляющая последовательность со схем «НЕ 18 поступает на схемы «И 15 схемы 13 сравнения исправляющей последовательности с последовательностью искаженных комбинаций строк, поступающей с блока 11 через схемы «НЕ 14 на вторые входы схем «И 15. В зависимости от результата сравнения в сдвигающие регистры 29 блока 27 памяти записывается либо комбинация, црошедщая исправление и находящаяся на выходе схем «И 22, либо через схемы «И 21 неяспрарленная комбинация, находящаяся в первом регистре 30.

По окончании выбора из памяти и исправления всех комбинаций столбцов на выходе счетчика 52 вырабатывается сигнал Г, который прекраи;ает выработку сигнала Тп+, и подается на схемы «И 35, 44. Синхроимпульсы TQ поступают через схему «И 44 на счетчик 42 и схемы «И 39, обеспечивающие выработку тактовых сигналов сдвига и организации перепроверки кодовой последовательности. Перепроверка организуется последовательно для каждой комбинации строки. По окончании перепроверки на выходе ячейки сдвига 40 появляется сигнал Тп+, который поступает на схему «И 45, открывая проход синхроимпульсов на ячейки сдвига 46-48 и на схему проверки восстанавливаемости.

Если комбинация искаженных строк, полученная в результате перепроверки признана невосстанавливаемой, то на выходе «И 8 появляется сигнал, который поступает на счетчик 9, уже хранящий единицу. Сигнал, появляющийся в результате этого на выходе счетчика 9, свидетельствует о неисправимой комбинации ошибок и осуществляет сброс всей схемы в исходное состояние. Если сигнал схемой «И 8 не вырабатывается, то сигнал Kz с блока 10 запрета стираний открывает схему «И 49, при этом К равно четырем циклам выбора комбинаций столбцов на блок 31 восстановления стираний и исправления ощибок с выдачей информации получателю.

Предмет изобретения

1. Устройство исправления ощибок, использующее локализацию ошибок в кодовой последовательности и восстановление переданных символов, содержащее блок приема, выход которого одновременно подключен через первый вход и первый выход блоха обнаружения ощибок в комбинациях строк ко входу блока фиксирования искаженных комбинаций строк, а через первый вход и выход блока памяти, первый вход и первый выход блока стирания строк, вход и выход первого регистра, первый вход и выход блока восстановления стираний и исправления ошибок к первому входу второго регистра, ко второму входу которого подсоединен первый выход блока управления, причем выход второго регистра является выходом устройства, отличающееся тем, что, с целью повыщения достоверности, выход блока фиксирования искаженных комбинаций строк через первый вход и выход блока программирования исправления ошибок в комбинациях столбцов подсоединен к первому входу блока памяти, подсоединенного вторым входом ко второму выходу блока управления, третий выход которого через первый вход и первый выход блока запрета стираний искаженных комбинаций строк подключен одновременно через второй вход и второй выход блока стирания

строк ко второму входу блока восстановления стираний и исправления ошибок, к третьему входу второго регистра и первому входу блока управления, подсоединенного своим четвертым выходом через первый вход и первый выход блока проверки восстанавливаемости одновременно к входу счетчика, а через второй вход и второй выход блока запрета стираний искаженных комбинаций строк одновременно ко второму входу блока программирования исправления ошибок в комбинациях столбцов и ко второму входу блока управления, пятый выход которого подключен к третьему входу блока стирания строк, а шестой выход блока управления подсоединен к третьему входу блока программирования исправления ошибок в комбинациях столбцов, к четвертому и пятому входам которого подключены соответственно первый вход второго регистра и выход первого регистра; второй выход блока проверки восстанавливаемости подсоединен к третьему входу блока управления, первый выход которого через первый вход и выход блока программирования проверки ошибок в строках подключен одновременно ко второму входу блока памяти и через второй вход и второй выход блока обнаружения ошибок в комбинациях строк к третьему входу блока запрета стираний искаженных комбинаций строк; блок программирования проверки ошибок в строках подключен вторым входом к первому входу блока стирания строк, подсоеди енного по четвертому входу ко второму входу блока проверки восстанавливаемости и к первому входу блока программирования исправления ошибок в комбинациях столбцов.

2. Устройство по п. 1, отличаюшееся

тем, что блок программирования исправления ошибок в комбинациях столбцов содержит схему сравнения исправляюшей последовательности с последовательностью искаженных комбинаций строк, подсоединенную по своему первому входу к первому входу блока организации исправления ошибок в комбинациях столбцов, а своим первым выходом - через первый вход и выход схемы запрета записи исправленной комбинации столбца в

блок памяти к выходу блока программирования исправления ошибок в комбинациях столбцов, второй и третий входы которого подключены ко второму и третьему входам схемы запрета записи исправленной комбинации столбца в блок памяти, подключенной по четвертому и пятому входам соответственно к четвертому и пятому входам блока программирования исправления ошибок в комбинациях столбцов, которые, в свою очередь,

подсоединены соответственно через первый и второй входы и первый выход схемы выделения исправляющей последовательности к шестому входу схемы запрета записи исправленной комбинации столбца в блок памяти,

подсоединенной по седьмому входу через второй вход и второй выход схемы сравнения исправляющей последовательности с последовательностью искаженных комбинаций строк ко второму выходу схемы выделения исправляющей последовательности.

Нг

Уд Л ,

Рш.З

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХРАЗНЕСЕННЫХ И СОСРЕДОТОЧЕННЫХВ ПАКЕТЫ ОШИБОК | 1972 |

|

SU428435A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК ПРИ ИТЕРАТИВНОМ КОДИРОВАНИИ | 1969 |

|

SU251253A1 |

| ДЕКОДЕР С ОБРАБОТКОЙ СПИСКА БАЗОВОГО КЛАСТЕРА | 2015 |

|

RU2605365C1 |

| ДЕКОДЕР ПРОИЗВЕДЕНИЯ КОДОВ РАЗМЕРНОСТИ 3D С ЗАПРОСАМИ | 2014 |

|

RU2562415C1 |

| Устройство для декодирования итеративного кода | 1988 |

|

SU1547080A1 |

| Устройство для коррекции ошибок в блоках памяти | 1982 |

|

SU1086460A1 |

| Устройство исправления стираний | 1975 |

|

SU581589A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1974 |

|

SU526898A1 |

| СПОСОБ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2344544C2 |

Авторы

Даты

1974-10-15—Публикация

1972-01-26—Подача