paiomCiM канале ве|роятаость трансформации ялбмсатов комбияации РТ выбирают значительно меньшее варояпности стирания элемента Комбинации

ArCSi,

S, -. PS

4s;

где PS-вероятность стирания трансформированного элемента комбинации; s-вероятность стирания (Нравильно принятого эле мента комбинации. Кроме того, в известном устройстве не и-оправляются ошибки, стирания с которых частично или полностью не введены о 6.ЛОК формирования полино.моВ ошибок изза перенолнения счетчика стираний. Покажем это -на inpHiMepe. При использовании корректирующего (п, k - кода с (i 3, исправляющего ошибки до кратаюсти / 2, емкость счетчика стираний / 2. Если будут -правильно приняты на пнтервале стирания (s) второй и иятый эле-менты комбинации и трансфор МИровап на интервале стиран-ия (Ря) восьмой элемент, то после регистрации второго и пятого элементов счетчик стираний перснолняется, завдзывает ключ и стирание БОСЬ.МОГО трансформирсва-нлого элемента не поступает в блок формирования .полиномов ошибок. Однократная ошибка, обуслйзлеипая восьмым элементО;м, не нонраеляется. Чи1сло различных вариа1ггов ош.ибок данного типа составляет

а ве.роятность цоявле1ния ошибкн данного типа СНределится ;выра|Жением

Р, - J-C,C,; : - sPs-T ,

где q-вероятность правильного элемента комбинации.

Пе исправляется и двухкратная ошибка следующего , обусловленная траисформацией иа интервале стирания PS третьего элемента, правильного приема на интервале стирания qs шестого элемента и трансформацией на интервале етира1Н,ия P.s- девятого элемента комбинации, так как после регистрации третьего и шестого элементов счетчик стираний переполняется, закрьгоает ключ и «стирание даВЯтого эле-мента ие поступает в блок формирования полинО:Мов ошибок. В результате двухкратная ошибка {третий и девятый элементы) не исправляется. Число различных вариантов ошибок данного типа составляет

.1

- г- г ..

а вероятность появления ош;иок.и данного типа определяется выражением

Р,-., C,,Cl,-q,.

(2)

Оценка вероятностей исправляе.мых однократоЕых и двухкратных ошибок для известного устройства .может быть выполнена по слбдующил формулам

Р , - С„.А;-Г- -1- C,,.C,.Qs . PS . «-2 ..

P,-C,, у-С„.С,.р2,,9-з). (4)

Кроме того, известное устройство имеет с; ож:ную KOiricTpyiKHino, обусловленную наличием второго бло.ка обна1руже,ния ошибок, выходного накопителя, счетчика и ключа.

Цель изобрете ния - упрощение устройства и увеличение числа исправляемых ошибок.

Это достигается тем, что iB предлагаемом устройстве выход двухпароговой схемы соединен с первы:М 15ходом б.тока фор.мирования полиномов ошибок, второй вход которого соедпнеп с вторым выходом блока обнаружения ошибок, выход сумматора по модулю два соединен с входом б.тока обНа ружения ошибок.

В результате все «стираиия, фиксируемые двухпороговой схемой, вводятся в блок формирсзания полгпюмоз ошибок, что позволяет исправить все ошибки в пределах обпаруживаюпи1х С1;особ;:остей кода, за исключсиием ошибок, обуслов;1еи1Н,ых трансфо.рмацией вие интервала стирч1ния (Рт ) элементов комбииа:ции. Однако количество этих ошибок может быть сде, Сколь yioniio малы.м :ja счет выбора достаточной .ны интерва/ia етнра ;ия. В известном устройстве это Прннципиально исключается, так как с увел; чение1М ширины ИНтерзала стир;;:: ия увеличнвается число «стираний, а следО|Вательио и ЧИсло неионравляемых ошибок за счет того, что не все «стирания зв.одятсп в бло.к формирования полиномов ошибок из-за п:реполнсния счетчика стираний.

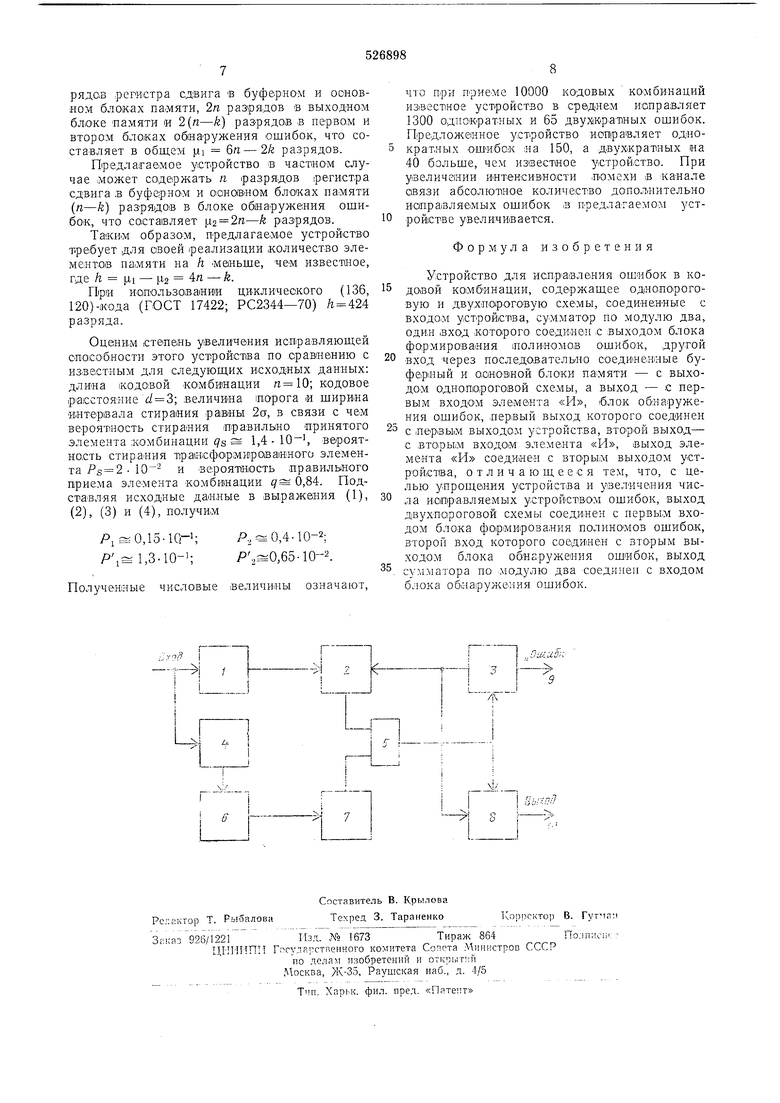

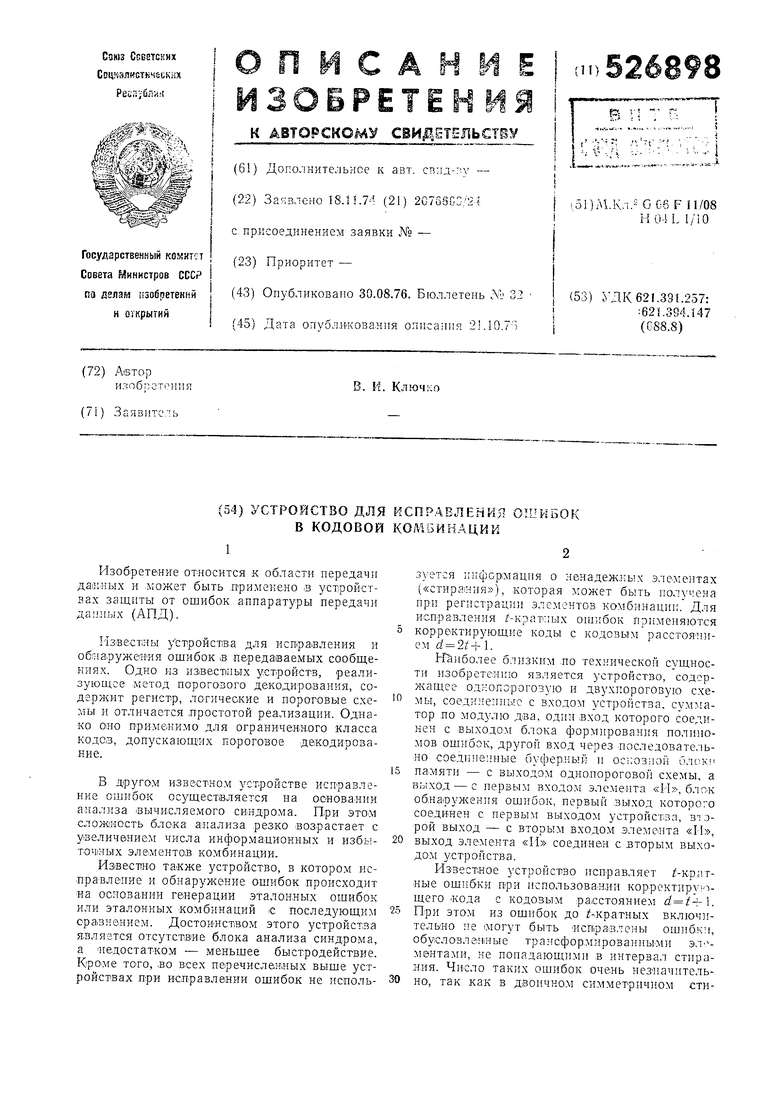

Па чертеже представлена функциональная

схелга устройства для исправления ошнбок в кодовой комбинации.

Устройство содержит двухпороговую схему /, блок 2 формирования полиномов ошибок, блок 3 обиаружения ошибок, однопороговую схему 4, сумолатор 5 но модулю два, буферный 6 и основной 7 блоки памяти, элемент «И 8, первый выход 9 и второй выход 10.

ДвуХ)Порогозая схема / осуществляет ,выявление ненадежных элементов («стираний) в кодовой кО(Мби;нации. Бло,к 2 формирования нолиномсв .ошибок воспринимает «стирания и. на их ооновс фс.:)ми:рует различ.ные поли.номы ошибо.к, вк/1ючающие нулевой полином,

полиномы с оди.-кратными ошибками, полиномы с д1вух1крат:нЫ|МИ ошибками, поли.номы с -кранными ошибками. Причем пе.р;ВЫ|М всегда фор,мИ1рует:ся (Нулевой полином, а далее - полиномы ошибок в порядке убывания ,верояткостей их появления в иопользуемом канале связи. Так, .например, при работе в двоичном симметричном ствраюш&м канале без памяти .после .нулевого .полинома фор мируются полиномы О.ДНобратных ошибок, зате.м полистомы двухкратных ошибок и так далее, в.ключая фо.р.мирование полиномов кратных ошибок. Так ка.к число «стираний г воз:можно в нределах от нуля до п, то для обеспечения наибольшей исиравляюшей способности блок фо;р.ми.рова1ния полиномо в ошибок должен формиро.вать

/ S Сг полинОМО з.

В каждом конкретнОМ случае величина S выбирается на соловании неравенства

tt

V ci с . о / С) с ,jj Ь „

П,ри необиаружении ошиб.ки в определенно-м цикле проверки по сигналу из блока 3 обнаружения ошибок в очередном цикле блок 2 формирует полином ошибки аналогичный п.редыдун ему.

Блок 3 обнаружения ошибок анализирует принимае.мую .кодо.вую комбинацию и разл1:чные варианты } справляемых комбинаций на наличие или отсутствие ошибок. Сумматор 5 по модулю два предназ--1аче Н для наложения иа провс.ряемую ко мбинацию .нолиномо.в ошибок, форми1руемых блоком 2. Одноиорого.вая схема 4 я.вляется регистр|Ируюш,им устройством, реализующи-м, например, днскретно-интегральный метод приема сигналов. Буферный блок памяти 6 осушествляет накопле ние эле.ментс.з оче.редной кодовой кo тбинaции в то время, как проверяется предыдущая комбинация. Емкость буферного блока памяти определяется скоростью модуляции передаваемых сообщений и скоростью обработки кодовой комбинации в устройстве. Основной блок иа.мяти 7 предназначен для записи принятой комбинации и выдачи ее до S раз на обработку.

Работа устройства происходит следующим образом.

Принятая кодо.вая ко.мбииация одно.времеш-ю постуиает иа входы однопороговой 4 и двухпс.роговой 1 схем. С выхода од:э.г..о-зоговой схемы 4 кодовая комби.иация, состоящая из последсзательности «О и «1. чс.рез буферный блс.к |На|МЯти 6 .Т11водится в о.:;ноЕ1;;ой блок памяти 7. В результате анализа каждого принимаемого элемента кодовой комбинации на выходе двухпороговой схемы / поялляется .сигнал «стирайшя в том случае, есл.и принятый элемент не может быть отождествлен ни с «1 ни с «О. Эти непадежные элементы подаются в блок 2 формирования полиномов ошибок.

После приема п элементов ко:мбина:ции 5 корре.ктирующего (п,/г)-кода, последняя из основного блока памяти 7 нодается на вход сумматора 5 по модулю два, на другой вход которого одновременно поступает нулевой полином блО|Ка 2 формирования полиномов ошибок. С выхода сумматора 5 элементы ко:мбинации, соответствующие -принятой кодовой комбинации, подаются на вход блока 5 об.наружапия ошибок. На выход устройства элементы не постуиают. Блок 3 обнаружения

5 ошибок анализирует принятую комбинацию и при необна ружении ощ1)бки выдает сигнал в блок 2 формирован :я полиномов ошибок п па второй (ВХОД эле.мента «И 8, открывая его. Блок 2, восприняв сигнал необнаружения

0 ошибки, в очередном цикле формирует полином ошибки, аналогпчиый предыдущему, т. е. нулевой. Кодовая комбинация второй раз постунает из осно.вного блока памяти 7 через сумматор 5 и открытьп элемент «П 8 не5 посредствен} о на выход устройства W.

Если при пСрвом ци.кле проверки блок 3 обна1руживаст ошибку, то комбинация из основного блока памяти 7 выдается на проверку второй раз и при этом блок 2 фор.мирова0 1-ия поЛИно: юв ошибок формирует полнном одно.кратной пшюки, который на суммато.ре 5 по модулю два осуществляет первое исправление пзи.нятой комбИнации. Псправленгая комбинация .ряется блоком 3, который ири необнаружении ошибки выдает сигнал в бло.к 2 п на -гюрой вход элг-мещ-а «И 8, открывая его. Блок 2, восприняв сигнал необ.наружения ошибки, форм11 рует полнном однократной ошибки, аналогичный предыдущему, и исправленная комбинация в очередном цикле через открытый элемент «П о ноступает на .выход устройства 10.

Если блок 3 сбттг.руживает ошибку в первом варианте исправленной комбпнацнн,

5 проверки продолжаются. П.рн этом б:1ок 2 фор.мирует очередной пол Г:-:ом однократной ошибк и та.к далее до nepiioro 1:еобнаружения ошибки в ка.ком-либо из вариантов исправленной ко.мбинац. Исправленная комбинация в очередном цикле работы через открытый элемент «И 8 иостунает на .выход устройства 10. Если ошибка будет обнаружена .при всех циклах проверки, то блок 3 обнаружения ошибок фиксирует наличие в принятой комбинации неисг/олвляемой ошибки, о чгм выдает снг.ал lia выход 9. В системах с решающей обратной связью этот сигнал используется для органнзаци: переспроса ;:скажениого сообп1,.

0Слож: ОС1ь дскоди.руюипх устройств, в ос.НОВ.НОМ, определяется количеством элементов памяти, нсобход:мых для его реализации. Известное уотрэйстзо .ри использовании циклического (п, )-кода без учета блока формирования полиномов ошибок содержит 2 разрядов регистра сдвига в буфернОМ и ооновном блоках па-мяти, 2п разрядов в выходном блоке памяти и 2(«-k) разрядов в первом и втором блоках обнаружения ошибок, что составляет в общем }Д1 6п-2k разрядов. Предлагаемое устройство в частном случае 1может содержать я разрядов регистра сдвига в буфернОМ и Ооносв.ном блоках памяти (п-/г) разрядов в блоке обнаружения ошибок, что соста1вляет ii2 - 2n-k р азрядов. TascHM образом, предлагаемое устройство требует для своей реализации количество элементов памяти на /г меньше, чем известное, где h |j,i - 1.12 4n - k. При ионользовании циклического (136, 120)-кода (ГОСТ 17422; РС2344-70) разряда. Оценим степень увеличения исправляюш,ей способности этого устройства по .сравнению с известным для следующих исходных данных: длина кодовой комбинации кодовое р|асстояние ( 3; величина inopora и ширина интервала стирания равны 2а, в связи с чем вероятность стирания правильно принятого элемента комбинации (s 1,, ве(роятность стирания трансформированного элемента и вероятность правильного приема элемента комби1нации qs 0,84. Подставляя исходные даатные в выражения (1), (2), (3) и (4), получим А, 0,4-10-2; PI O,IO-IQ-I; ,65-10-2. Р 1,3-10-1; Полученные числовые величины означают. что при приеме 10000 кодовых комбинаций известное устройство в среднем исправляет 1300 однократных и 65 двух|Крат1Ных ошибок. Предложенное устройство иоправляет однократных ошибо;к ;на 150, а дву)скратных на 40 больше, чем известное устройство. При увеличении интенсивности помехи в канале авязи абсолютное количество дополнительно И1апра1вляемых ошибок в предлагаемом устройстве увеличивается. Формула изобретения Устройство для исправления ошибок в кодовой комбинации, содержащее однопороговую и двухпороговую схемы, соединенные с входом устройства, сумматор но модулю два, один вход которого соединен с выходом блока формирования полиномов ошибок, другой вход через последовательно соединенные буферный и основной блоки памяти - с выходом однопороговой схемы, а выход - с первым входом элемента «И, блок обнаружения ошибок, первый выход которого соединен с первым выходом устройства, второй выход- с вторым входом элемента «И, выход элемента «П соединен с вторы;м выходом устройства, отличающееся тем, что, с целью упрощения устройства и увеличения числа иопр авляемых устройством ошибок, выход двухпороговой схемы соединен с первым входом блока формирования полиномов ошибок, второй вход которого соединен с вторым выходом блока обнаружения ошибок, выход сумматора по .модулю два соединен с входом блока обнаружения ошибок.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1976 |

|

SU604170A2 |

| Устройство для обнаружения и исправления ошибок в кодовой комбинации | 1974 |

|

SU540389A1 |

| Устройство для обнаружения ииСпРАВлЕНия ОшибОК B КОдОВОйКОМбиНАции | 1979 |

|

SU801283A2 |

| Устройство для исправления ошибок в кодовой комбинации | 1976 |

|

SU599267A2 |

| Устройство для обнаружения ошибок | 1983 |

|

SU1100746A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ОШИБОК В ПОЛИНОМИАЛЬНОЙ СИСТЕМЕ КЛАССОВ | 2014 |

|

RU2560823C1 |

| Устройство магнитной записи для коррекции цифровой информации | 1979 |

|

SU949717A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| Устройство для исправления ошибок кодов Боуза-Чоудхури-Хоквингема | 1987 |

|

SU1531227A1 |

-I

I

/i

-bj

::

/Гч

-

Авторы

Даты

1976-08-30—Публикация

1974-11-18—Подача